基于FPGA的低功耗高速网络报文解析系统设计

2018-02-25杨斌

杨斌

摘要 随着互联网的高速发展,网络规模日益庞大,网络环境日益复杂,使得网络安全问题日益严重,对硬件实现的深度报文检测系统也提出了更高的要求。而基于FPGA实现的报文检测系统一直是实现报文检测系统的一个重要分支,尤其是在商业领域,占据着重要的地位,具有很强的实际研究意义。本文在前人研究的基础上,设计了一种基于FPGA低功耗高速网络报文解析系统,本系统采用模块化设计,充分利用FPGA并行、流水化处理的优势,并且在FPCA内部增加流控信号,提高整个系统的业务承载能力,搭建系统开发环境,完成系统关键模块的仿真和板级验证。

【关键词】低功耗 高速 报文解析系统 FPGA

1 引言

随着计算机网络的高速发展,计算机网络的规模不断壮大,计算机网络正在经济和生活的各个领域迅速普及,信息的获取、共享和传播变得更加方便,构建在互联网上的应用也越来越多,整个社会对互联网的依赖性也越来越强,实时有效的网络报文检测技术对网管系统和网络监控系统越来越重要。

由于在传统的报文检测系统中,整个系统是工作在一个恒定的频率上的,当频率一定时,各个模块的最大的处理频率是一样的,然而网络上的流大小却是突发变化的,并不是以最大的流进行传送的,过高的处理频率虽然满足模块的处理要求,但是却因为过多的消耗资源而引起带宽的浪费。因此,一种低功耗的高速网络报文检测系统呼之欲出。

有鉴于此,本文提出了一种基于硬件的低功耗的高速网络报文检测系统,达到在应用需求不断增加的情况下,用硬件实现网络报文检测的功能,根据网络的需求,实时动态在线调整频率,使其能够根据用户要求更加灵活的提供服务功能。在正常情况下,对传送的数据流量进行统计,读出到达流量的大小和时间,再根据流量大小对应查出系统的处理频率,进行动态控制系统自身处理频率,进而调整系统的实时处理能力,实现对网络报文中内容负载实时在线的深度检测,满足低功耗的要求,以这种思想为指导,对网络报文检测进行了针对性设计,为网络报文检测提供更灵活的手段,实现了根据用户的设置要求来控制处理能力从而达到一种低功耗的目的。本系统可以连续地检测网络流量,对网络起到实时监控的作用。

2 报文解析系统总体设计方案

为了解决上述技术问题,本文提出了一种低功耗的高速网络报文检测系统。总体框架如图1所示,通过硬件实现网络报文检测的结构,降低了对处理器资源的消耗,采用实时动态地控制方法,提升了设备检测的灵活性,适用于大规模的网络报文检测。系统一共包括八个模块,分别是时间戳模块、流量检测模块、报文解析模块、内容萃取模块、匹配控制模块、综合判定模块、格式封装模块、频率控制模块。

时间戳模块用于在到达系统的报文中加入时间标签,为后续模块处理提供时间基准。

流量检测模块用于检测到达报文的数据流量信息,为频率控制模块对本系统的调控提供一个依据。流量检测模块主要功能是转发报文并检测到达报文的数据流量信息,根据报文添加的时间标签,假设在时间t1到t2到达的数据包为n个,第i个数据包为1.比特,则在时间t1到t2通过的总报文比特数为

报文解析模块,用于识别其承载报文协议类型,为网络内容的过滤提供数据报文协议信息及数据报文有效载荷信息。

内容萃取模块可以根据用户配置管理要求,灵活准确地萃取数据报文信息和有效载荷信息。

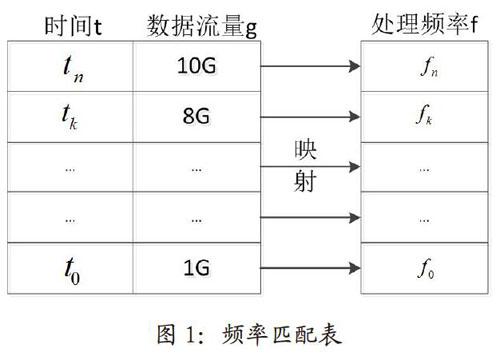

匹配控制模块可以根据萃取的数据相关信息在预先设定好的表项中进行匹配查找,与用户配置的TCAM规则表项中的五元组信息进行匹配。匹配控制模块主要在高速的链路下,基于硬件来实现模式匹配,利用TCAM(Ternary Contenr Accessible Memoery),即三元内容寻址内存+SRAM( Static RandomAccess Memory),即静态随机存取存储器,完成关键字的查找和配送功能,实现高速链路下的匹配,其中TCAM用来放规则的匹配域,SRAM用来放规则对应实施动作,频率匹配表如图1所示。

其中数据流量g是在时间t时刻通过系统的实时数据流量,处理频率f是在通过系统数据流量为g时对整个系统的处理频率。

综合判定模块可以根据匹配结果和用户设定的流量阈值对数据包进行综合判定,进而对数据包进行相应的转发、存储、上报、丢弃等操作。

格式封装模块用于对报文格式头转换和封装,将数据封装成MAC帧,再通过10G高速接口将MAC帧传输到互联网或指定的服务器上。

频率控制模块根据通过系统的实时数据流量,可以动态自适应地调控系统的处理频率,进而对系统整体处理能力进行调控。频率控制模块包括:流量读取单元,用于读取流量检测模块传送的数据流量信息,并记录数据流量g和時间t1和t2;数据流缓存单元,用于存入所记录的数据流量g和时间tl和t2;匹配查找单元,根据记录的数据流量g和时间t1和t2,在频率匹配表中查找出对应的处理频率;调控单元,根据匹配的处理频率,调控系统各个模块的处理频率,使整个系统模块在这个频率下工作。

本系统的内部封装图如图2所示。

内部格式包括:时间戳、匹配命中、匹配结果、解析结果,和原始二层帧,其中匹配的状态如图3所示。

其中,l、00表示不关心;2、01表示不命中;3、11表示命中。

3 报文检测系统总体流程

本文所设计低功耗的高速网络报文检测系统的总体流程如图4所示,首先,时间戳模块在到达数据包中加入到达系统的时间标签,接着,流量检测模块检测出到达的网络数据流量信息,把该信息传送给频率控制模块,同时把报文转发到报文解析模块,然后,报文解析模块解析出数据报文的协议信息和有效载荷,并把数据报文协议信息及数据报文有效载荷信息传送给内容萃取模块,内容萃取模块会根据用户配置的管理要求,萃取出数据报文的协议信息和有效载荷并传送给匹配控制模块进行匹配,匹配控制模块根据萃取的数据相关信息在预先设定好的表项中进行匹配查找,并与用户配置的TCAM规则表项中的五元组信息进行匹配,综合判定模块根据匹配结果和用户设定的流量阈值对数据包进行综合判定,如果判定成功则送入格式封装模块,否则,丢弃,最后,格式封装模块对数据报文进行数据格式封装,完成格式头的转换和封装,将数据封装出MAC帧,再通过10G高速接口将MAC帧传送给互联网或指定服务器上。

3.1 综合判定流程

本文所设计低功耗的高速网络报文检测系统的综合判定流程如图5所示,首先,将匹配控制模块输出的五元组信息送至TCAM芯片,与用户配置的TCAM规则表项中五元组信息进行匹配,等待接收匹配结果,如果是丢弃,则丢弃该报文,否则将判断匹配的数据是否达到指定的服务器,如果是则结束,否则将匹配的数据与用户配置的数据流量阈值进行比较,如果超出阈值则丢弃,否则将数据转发到互联网上。

3.2 频率控制流程

本文所设计低功耗的高速网络报文检测系统的频率控制流程如图6所示,首先提取流量检测模块传送的数据流量信息,并将数据流量信息送入流量缓存,然后将数据流量信息存入流量缓存并记录数据流量和时间,接着,根据记录的数据流量信息,从流量缓存中读出数据流量和时间,查找频率匹配表,找出对应的处理频率,最后根据查找出对应的处理频率,统一调整时间戳模块、流量检测模块、报文解析模块、内容萃取模块、匹配控制模块、综合判定模块、格式封装模块的处理频率。

4 系统实现和仿真

本系统采用传统FPGA开发“自顶而下”的设计方法。“自顶而下”的设计方法是从系统级设计开始,然后往下划分二级模块,再把二级模块继续往划分,一直划分下去,直到能够使用基本模块或者IP核直接实现为止。“自顶而下”的设计方法在描述系统功能时能够独立于芯片之外,在设计之初,研发人员可以摆脱芯片结构的约束,只需要对功能进行设计,这样可规避因设计方法带来的风险,同时也可以缩短系统设计周期。

本系统选用Xilinx公司的Virtex-6系列芯片作为主要开发平台,为了能够适应不断演化的标准和不断提高性能需求,Virtex-6系列芯片比Virtex-5系列功耗降低大约50%,并且该系列产品进行了组合优化,包括灵活性、IP核、收发器以及开发工具等支持。考虑到系统中各个模块之间数据通信的复杂性,本系统采用Xilinx FPGA的SOPC设计方法,在ISE开发环境中来实现系统顶层文件以及其他模块的设计,并最终完成系统的编译、综合和调试等工作。

系统仿真主要是对关键信号的时序仿真和板级验证。板级验证和仿真主要是将比特流文件下载到板卡中,通过ChipScope Pro对系统的信号完整性和电磁干扰进行分析。图7到图9为发送和接受信号以及格式封装模块FIFO读写信号的板级验证和仿真。

5 结束语

随着网络安全问题日益突出,网络规模日益庞大,网络环境日益复杂,对报文检测系统的要求也越来越高。FPGA实现报文检测系统一直是报文检测研究的一个重要分支。本文在前人研究的基础上,设计实现了一种基于FPGA的报文检测系统。

本文提出了一種低功耗的高速网络报文检测系统,本系统,可以通过实时的数据流量,动态地控制系统自身的处理频率,实现对系统实时处理能力的在线调整,进而完成对高速网络中报文内容负载深度检测功能,并大大降低了系统的功耗,可适用于10G高速网络环境,并以并行流水线的方式实现网络报文检测,同时又达到了低功耗的目的。

参考文献

[1]张子文,高效深度报文检测的研究和实现[D].国防科学技术大学,2008 (11).

[2] Aho A V,Corasick M J.Efficient stringmatching: An aid to bibliographicsearch. Comm. of the ACM, 18 (06): 333-340. 1975.

[3] Commentz-Walter B.A string matchingalgorithm fast on the average.Proc.of ICALP, pages 118-132, July 1979.

[4]Wu S,Manber U.A fast algorithm formulti-pat tern searching [M]. Tech.

R. TR-94-17, Dept of Comp Science Univof Arizona,1994.

[5] Jeffrey E. F. Friedl. Master RegularExpressions.Third Edition[M].0' Reilly Media,Inc. 2007:151-156

[6] SNORT Network Intrusion DetectionSystem[DB/OL] . 2015-12. http: //www.snor t. org.

[7]Bro Intrusion Detection System [DB/OL] . 2015-12. ht tp: //bro-ids. org/Overview. html.

[8]Levandoski J,Sommer E,Strait M.Application Layer Packet Classifierfor Linux [M] . 2 015-12. ht tp: //17-filter. sourceforge. net/.

[9]Qiu Tanga,Lei Jianga,Xin-xing Liua,Qiong Dai.A Real-time Updatable FPGA-based Architecture for Fast RegularExpression Ma tching [J] . Informa tionTechnology and QuantitativeManagement (ITQM 2014). ProcediaComputer Science 31 (2014):852-859.

[lO]Shuhui Chen,Rongxing Lu,A regularexpression matching engine withhybrid memories [J]. Computer Standards& Interfaces. 36 (2014): 880-888.

[11] Yoichi Wakaba, Shinobu, A Flexible AndCompact Regular Expression MatchingEngine Using Partial ReconfigurationFor FPGA[J]. 2013 16th EuromicroConference on Digital SystemDesign. 2013: 293-296.

[12] Yuan Wen, Xingsheng Tang, LihanJu, Tianzhou Chen. PeRex: A powerefficient FPGA-based architecturefor regular expression matching[C].2011 IEEE/ACM InternationalConference on Green Computing andCommunications. 2011:188-193.

[13]Jan van Lunteren, Alexis Guanella.Hardware-Accelerated RegularExpression Matching at Multiple Tensof Gb/s [J]. 2012 Proceedings IEEEINFOCOM, 2012:1737-1774.

[14] Chun-Liang L, Yi-Shan L, Yaw-Chung C.A Hybrid CPU/GPU Pattern-Matching Algorithm for Deep PacketInspection [J] . Plos One, 2015, 10 (10) .

[15] Zhan Y R, Wang Z S. Deep PacketInspection Based on Many-CorePlatform[Jl.Journal of Computer &Communications, 2015, 03 (05) : 1-6.

[16] Yu, Xiaodong. Deep packet inspectionon large datasets:Algorithmic andparallelization techniques foraccelerating regular expressionmatching on many-core processors[J].Dissertations&Theses-Gradworks, 2013.