HITCE陶瓷阵列封装板级互联可靠性研究

2018-01-23蒋长顺仝良玉张国华

蒋长顺,仝良玉,张国华

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

1 前言

随着集成电路功能和I/O数目的增加,陶瓷封装引出端数量也相应提高,CDIP、CQFP等传统封装形式已不能满足多I/O芯片的封装要求。陶瓷阵列封装的引出端分布在基板底面,引出端可有效利用的面积更大,从而可以支持更多的引出数量。根据引出端互联形式的不同,陶瓷阵列封装可以分为针栅阵列封装(CPGA)、球栅阵列封装(CBGA)、栅格阵列封装(CLGA)、柱栅阵列封装(CCGA)几种形式。其中CPGA和CLGA引线的密度也相对较低;CBGA和CCGA引出端分别为焊球和焊柱,引出的密度也更高。

集成电路封装材料与组装板材料系统的匹配是影响产品可靠性的关键因素之一,由于不同材料热膨胀系数(CTE)的差异,温变载荷下的周期性热应力往往会造成封装互连的疲劳失效[1]。HTCC氧化铝陶瓷封装的 CTE(约 6.5×10-6/℃)与硅基芯片的 CTE(约 3.5×10-6/℃)匹配良好,芯片与基板之间的倒装焊凸点互联(一级互连)可靠性较好。但陶瓷材料与有机印制板的CTE(约15×10-6/℃)失配较大,令人关注的是其板级互连(或二级互连)可靠性。

本文介绍氧化铝CBGA、CCGA陶瓷阵列封装结构及其封装互连可靠性,采用有限元方法对高热膨胀系数陶瓷材料(HITCE陶瓷)的封装互联可靠性进行了仿真分析。

2 CBGA和CCGA的封装结构与互联可靠性

CBGA和CCGA的主要区别在于焊球和焊柱的高度不同:焊球高度较小,与PCB板的耦合更好,在信号传输、导热路径短等方面有一定优势;而焊柱高度则较大,有利于缓解热失配产生的应力应变,通常应用于大尺寸陶瓷封装中。

2.1 CBGA封装结构与互联可靠性

图1为CBGA的板级安装示意图,焊球通常为高铅材料(90Pb10Sn,熔点>300℃),焊膏多为低温共晶焊料(63Sn37Pb),采用再回流工艺进行植球操作。高铅焊球在回流过程中不会发生塌陷,互连高度不会低于焊球高度。

图1 CBGA板级安装示意图

典型的焊球节距包括1.27 mm、1.0 mm、0.8 mm等,焊球直径也较小(一般小于1 mm)。小尺寸焊球的劣势就是互连刚度高,在经历温度循环载荷时,焊点的应力不能有效释放,容易出现疲劳开裂现象,封装体尺寸大于32 mm×32 mm以上不推荐采用CBGA封装形式。

2.2 CCGA封装结构与互联可靠性

CCGA是通过增加互连高度来提高板级互联可靠性,图2为典型的CCGA外形结构示意图。常规焊柱采用高铅焊料(90Pb10Sn),焊柱的典型高度为2.54mm或2.21 mm,明显高于普通的焊球,可以满足大尺寸陶瓷封装的温循可靠性要求。IBM推荐的CCGA,采用氧化铝HTCC陶瓷基板,90Pb10Sn焊柱(直径0.51 mm、高2.2 mm),其最大尺寸可以达到52.5 mm×52.5 mm(1.0 mm 节距,51×51阵列)[4]。

图2 典型CCGA封装外形示意图

几种 CCGA 焊柱结构如图 3 所示[6~7],图 3(a)为普通的Pb90Sn10焊柱,图3(b)为表面缠绕铜带的焊柱结构,焊柱主体为Pb80/Sn20低温焊料,焊柱表面采用铜带螺旋缠绕,其温循可靠性要高于普通的焊柱。图3(c)为NASA提出的微弹簧互连结构,NASA认为弹簧结构的互连可靠性高于普通焊柱,适用于互连密度更高、可靠性要求更高的场合。

图3 焊柱典型结构图

焊柱互连的优势主要体现在缓解热失配造成的热应力方面,而在抗机械冲击方面,由于焊柱高度较高,电路的板级抗振动性能就会降低;通常在板级组装后,需要在电路的4个角进行点胶加固以满足抗振要求[8~9];且铅锡焊料的材质较软,在加工及后期的存储运输过程中都需要对焊柱进行特别的保护,以避免损坏。

3 HITCE陶瓷封装结构及板级互连可靠性

3.1 HITCE陶瓷材料与封装结构

一些高速、高频器件的应用,需要考虑采用HITCE陶瓷封装材料以满足器件电性能要求。HITCE陶瓷为低温共烧(LTCC)工艺,HTCC和HITCE的典型特性参数对比见表1,由表中可以看到HITCE材料具有以下主要优势:

(1)HITCE陶瓷的CTE更高,与有机基板的CTE匹配更好,从而提升电路的板级互联可靠性。

(2)HITCE陶瓷封装的布线材料采用铜导体,其方块电阻比HTCC陶瓷的布线材料(W、Mo或W-Mo)减小约3倍。

(3)HITCE陶瓷的介电常数和介质损耗角均小于HTCC陶瓷,且在高频信号下(高至60 GHz)电特性参数的稳定性很好。

鉴于以上优势,对于一些高频、高速电路,考虑选用HITCE陶瓷封装能更好地满足电路封装要求。

目前国外针对HITCE陶瓷封装已经有一些可靠性验证工作[10],国内在此方面的研究相对较少。

表1 普通Al2O3陶瓷与HITCE陶瓷材料参数对比

3.2 焊点温循疲劳分析理论

由于不同封装结构材料的CTE不一致,封装的互连部分在温循过程中会因周期性的应力应变而产生疲劳失效,其中焊点温循开裂失效是最常见的问题之一。焊点的温循疲劳属于低周疲劳,目前业内多采用有限元方法对焊点的温循疲劳寿命进行分析预测,常用的寿命预测方法有两种[11]:

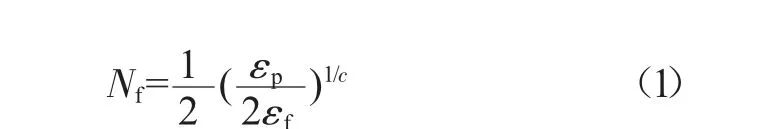

(1)基于塑性应变范围的Coffin-Manson方程,其表达式为:

其中,Nf为焊点的温度循环的特征寿命;εp为每个温循周期焊点的非弹性剪切应变范围;εf为疲劳迟滞系数,对于PbSn共晶焊料来说,εf=0.325;c为疲劳迟滞指数,其值与温循的平均温度和高温保持时间有关,一般在-0.4~-0.7之间。

(2)基于应变能密度的Darveaux方程,它将焊点的失效分为初始裂纹的产生和裂纹扩展至失效两个阶段。初始裂纹的产生和裂纹的扩展速度都和界面单元的能量释放密度有关,其表达式为:

其中,N0为产生初始裂纹的温循次数,Ne为裂纹扩展至失效的温循次数,温循寿命为两者之和。ΔWavg为界面裂纹单元的平均应变能量密度,一般为减小误差,通常取界面单元的体积加权平均能量密度值。因此,为比较焊点的温循寿命,可以对焊点温循过程中的塑性应变范围或应变能量密度进行比较。

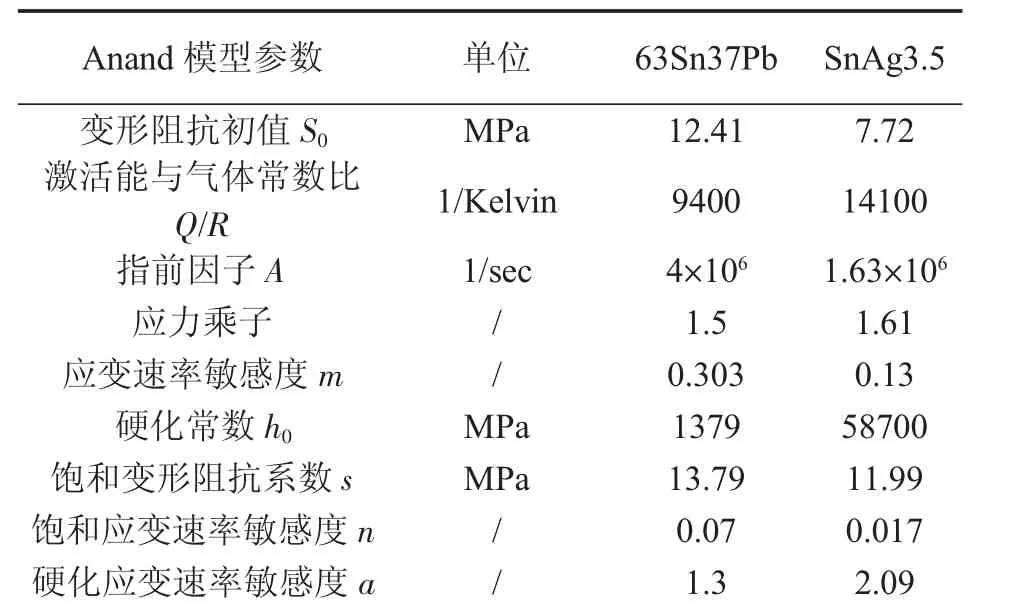

焊点在温循过程中的粘塑性应变行为,多采用Anand粘塑性本构模型,仿真分析中涉及的焊点Anand 模型参数见表 2[12~13]。

表2 焊料Anand模型参数

3.3 HITCE陶瓷封装互连温循可靠性对比分析

HITCE多用于FC产品,仿真分析对比了HTCC和HITCE材料FC-CBGA陶瓷封装的一级互连(芯片凸点)和板级互连(焊球)的温循可靠性。

板级组装结构截面图见图4,模型主要包括芯片、底填料、凸点、陶瓷基板、焊球、PCB等部分,陶瓷基板的尺寸为25 mm×25 mm×2.0 mm。焊料采用Anand模型,具体参数见表2,其他部分只考虑材料的线弹特性,相关尺寸及材料参数见表3。

图4 CBGA板级安装截面图

温循条件按照GJB548B-2005方法1010,试验条件C,温度范围-65℃~150℃,高温、低温段保持时间≥15 min,高温与低温转换时间≤15 min。

图5为BGA焊球温循过程中的塑性应变和塑性应变能密度变化曲线。由图5可知,采用HITCE材料的BGA封装,每个温循周期焊点的塑性应变及塑性应变能量增量均小于HTCC材料的BGA焊点,因此焊点的温循可靠性更高。

表3 仿真模型尺寸及材料参数

图5 CBGA焊点温循过程疲劳参数对比

对凸点和焊球分别采用式(1)对焊点的疲劳寿命进行预估,计算结果见表4。HITCE陶瓷封装焊点的温循疲劳寿命明显高于HTCC陶瓷封装,而芯片凸点的温循疲劳寿命差别并不大,这主要是因为芯片凸点有底部填充料的保护。从整体来看,HITCE陶瓷封装的板级互联可靠性有明显提升。

表4 焊点温循可靠性仿真结果对比

4 结束语

CBGA和CCGA封装的应用越来越广泛,CBGA封装由于焊点高度较小,对于面积较大的陶瓷封装,HTCC陶瓷封装易存在板级互联可靠性问题,HITCE陶瓷封装的板级互联可靠性更高,且电特性更好,可以考虑采用HITCE陶瓷封装以满足电路封装要求。

[1]成钢.电路板设计中的膨胀系数匹配问题[J].电子设计与工程,2011,19(3):57-61.

[2]P E Tegehall,B D Dun.Assessment of the reliability of solder joints to ball and column grid array packages for space applications[M].ESA publication division,2001.

[3]Evaluation ofCeramic BGAPackage Solder-Joint-Reliability With a View to Space Applications[EB/OL].AVIO 23rdMicroelectronics Workshop,2011.

[4]IBM.Ceramic Column Grid Array Assembly and Rework User’s Guide[EB/OL].http://www.chips.ibm.com.

[5]Reza Ghaffarian.Reliability recolumned area array packages[EB/OL].NASA GSFC,2009.

[6]Reza Ghaffarian.Reliability testing of CGA/LGA packaging[EB/OL].NASA GSFC,June,2012.

[7]Reza Ghaffarian.Reliability and failure analysis of CGA/LGA/HDI[EB/OL].NASA GSFC,June,2014.

[8]Reza Ghaffarian.CCGA packages for space applications[J].Microelectronics Reliability,2006(46):2006-2024.

[9]Reza Ghaffarian.Thermal Cycle Reliability and Failure Mechanisms of CCGA and PBGA Assemblies With and Without Corner Staking[J].IEEE TRANSACTIONS ON COMPONENTS AND PACKAGING TECHNOLOGIES,2008,31(2):285-296.

[10]Olivier GAILLARD.State of the art of Hi-TCE Ceramic Packages[EB/OL].ATMEL,April,2005.

[11]Yong Je Lee.Viscoplastic Finite-Element Simulation to Predict the Solder Joint Fatigue Life of Different Flash Memory Die Stacking Architectures[D].The University of Texas at Arlington,2006.

[12]R Darveaux.Effect of simulation methodology on solder joint crack growth correlation[C].Proceeding of IEEE Electronic components and technology conference,2000.

[13]Z Chen,G Wang,etc.Viscoplastic Anand model for solder alloys and its application[J].Soldering and surface mount technology,2000,12:31-36.