基于Verilog—A的两点调制锁相环综合实验设计

2018-01-18周冉冉王永

周冉冉 王永

摘要:两点调制是近年来锁相环芯片研究的热点问题,是一种解决调制带宽限制、实现全通传输的有效新方法。为了让学生深入理解锁相环两点调制的工作机理,本实验首先对锁相环进行Verilog-A行为级建模,以帮助学生快速了解锁相环的动态锁定过程。在此基础上,通过进一步利用两点调制的方式实现二进制频移键控,让学生理解增益匹配的重要性和两点调制锁相环的系统设计方法。整个实验设计由浅入深地涵盖了两点调制锁相环的系统设计及电路实现,有效地帮助学生对集成电路芯片设计前沿知识的理解和掌握。

关键词:锁相环;Verilog-A;两点调制;二进制频移键控

中图分类号:TN402 文献标识码:A 文章编号:1007-9416(2018)09-0101-03

随着集成电路技术的快速发展,射频无线通信系统在人们的生活中得到广泛的应用,以手机射频芯片、北斗导航芯片、物联网芯片为代表的射频通信专用芯片已成为现代集成电路的研究热点之一。作为时钟产生和恢复电路的核心部件,锁相环(Phase-Locked Loop, PLL)在射频电路中占有重要的地位[1-3]。了解和掌握锁相环的性能指标和设计方法,已成为一名射频集成电路工程师必备的专业技能。

山东大学微电子学院开设了射频集成电路设计研究生专业课,设计了基于Verilog-A的锁相环两点调制综合实验,对锁相环进行行为级快速仿真,解决了晶体管级锁相环电路仿真慢的问题,为两点调制锁相环电路的系统指标确定提供了便捷的方法。最终的环路仿真结果表明,该实验可以准确地模拟锁相环两点调制特性,有助于学生学习理解锁相环的工作原理,掌握锁相环的设计方法。

1 锁相环实验设计

锁相环综合实验设计的内容是,采用Verilog-A对电荷泵锁相环进行行为级建模和瞬态仿真,帮助学生理解锁相环的动态锁定过程;通过相位调制的方式实现二进制频移键控(BFSK),帮助学生理解两点调制的设计方法和增益匹配的重要性。鎖相环系统设计采用自上而下(Top-Down)的设计方法,根据系统参数确定每一个模块的设计参数,具体设计步骤如下:

(1)定义系统设计指标。在实验中根据2.4 GHz蓝牙芯片系统的要求来确定系统指标,如表1所示。(2)根据电荷泵锁相环的数学模型确定压控振荡器(VCO)的增益KVCO、分频器整数和小数部分的分频比、环路滤波器的滤波带宽等参数。(3)对锁相环模块进行行为级建模,分别搭建整数型和小数型锁相环环路,对锁相环进行瞬态仿真,研究环路的时域动态锁定过程。(4)在第三步的基础上,从差分积分调制器调制器(DSM)和VCO两点加入基带信号,实现BFSK调制,观察输出信号的时域和频域特性。(5)实验结果分析和撰写实验报告。

2 锁相环系统参数确定

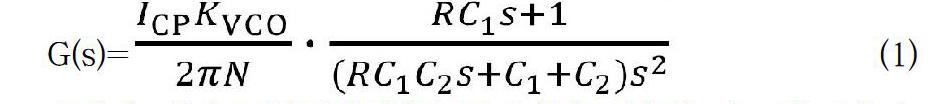

锁相环路本质上是一个相位负反馈自动控制系统[4-6],如图1所示,一个典型的电荷泵锁相环包括鉴频鉴相器(PFD)、电荷泵(CP)、环路滤波器、VCO和分频器等模块,其开环增益可以表示为[7]:

实验中,首先要根据设计指标确定锁相环参数。主要的系统参数包括:(1)VCO压控增益KVCO;(2)电荷泵电流ICP;(3)分频比;(4)滤波器带宽特性。

2.1 压控振荡器压控增益KVCO

典型的BFSK调制如图2所示[8]。对于表1定义的BFSK信号,当发送“1”时,输出频率为2.41GHz;当发送“0”时,输出频率为 2.39GHz。实际设计中,由于非理想因素,VCO的调频曲线在压控区间(0V-1V)不是一条理想线性曲线。为了加快调频锁定速度,选取中值电压0.5V左右调频曲线线性度较好的一段用于压控调频:当输入电压为0.5V时,输出频率为2.4GHz;当输入控制电压为0.42-0.58V时,覆盖2.39-2.41GHz的频率范围。由此VCO的频率压控增益为:

2.2 环路分频比

锁相环输入频率与输出频率的关系为:

fVCO=fref·N (3)

由表1可知,输入参考频率为48MHz,输出频率为2.39- 2.41GHz,对应的分频比为49.7917-50.2083,分频器包括整数分频和小数分频部分。为了解决分频比的整数部分不是一个固定的数值的问题,先将输出信号进行4分频,然后进行分频比为12.f的小数分频。当输出频率为2.4GHz时,小数部分分频比为0.5;当输出频率为2.39GHz时,小数部分分频比为0.44792;当输出频率为2.41GHz时,小数部分分频比为0.55208。

2.3 电荷泵和低通滤波器设计

在图1所示电路中,C1C2,由公式(1)可以得到的锁相环带宽表达式为:

BW= (4)

环路滤波器引入一个零点ωz=1/RC1,一个极点ωp=1/RC2。为了环路的稳定,取ωz=0.2·BW,ωp=3·BW。在设计电荷泵电流时,虽然较大的电荷泵电流能有效提高环路增益,但也要求较大的滤波电容。因此,电荷泵电流的选择要综合考虑环路稳定性和面积的折中,对于确定的环路带宽,电荷泵电流和环路滤波器电阻成反比,与电容成正比。在实验中,选取ICP=40μA,R=20kΩ,可以得到锁相环带宽为BW≈317kHz。由此可以推算,电容取值为C1=150pF, C2=8pF。

2.4 两点调制中的增益匹配

通过锁相环结构实现BFSK调制,最直接的方法是改变分频比或者VCO控制电压。如果基带信号通过DSM加入进行单点调制,反应到锁相环的输出端呈现出低通特性,高频调制信号无法线性地传输到输出端;如果基带信号通过VCO加入进行单点调制,反应到锁相环的输出端呈现高通特性,低频调制信号无法线性地传输到输出端。

两点调制方法可以有效破除锁相环带宽的限制,实现锁相环信号的全通调制。如图3所示,在DSM和VCO两点注入基带信号,通过调整高通支路和低通支路的增益实现增益匹配,从而实现锁相环的全通特性。高通支路经过一个可调增益Khp注入到VCO输入端,低通支路通过一个可调增益Klp注入到DSM,低通滤波器(LPF)传输函数为Hlpf(s),Kpd为电荷泵增益,那么传输函数Htpm(s)为:

Htpm(s)= (5)

要想实现全通特性,传输函数必须满足:

KhpKVCO=1 (6)

假设基带信号s(t)为数据率为500kb/s的伪随机码序列,通过符号转换,并与调频指数βm相乘得到最大频偏,那么输出频率可以通过式(7)和式(8)两种形式表示:

fo=fc+KhpKVCOβmfmsgn(s(t)-0.5) (7)

fo=fc+4frefKlpβmfmsgn(s(t)-0.5) (8)

其中,Δf=βm fm,代表最大頻偏,sgn(n)代表符号函数,结合式(6-8),低通支路和高通支路的增益必须满足:

4frefKlp=KhpKVCO (9)

3 锁相环Verilog-A行为级建模

利用数学模型和参数计算的结果直接进行电路设计、进而验证锁相环系统参数的方法设计周期长、迭代效率低。对于数模混合集成电路系统,采用Verilog-A行为描述语言对锁相环电路模块进行建模是系统设计的较优选择[9]。

Verilog-A是一个Verilog-AMS数模混合信号设计语言中模拟电路行为级描述的子模块[10],应用Verilog-A可以对各种模拟系统进行行为级描述,方便快捷地确定系统方案的可行性。应用Verilog-A语言编写锁相环系统各个子电路的行为级模型[11-12],直流电压源、时钟信号源、电阻、电容等器件采用Cadence的analogLib库中的器件模型,完成系统搭建。最终的行为级锁相环仿真环路如图4所示。

4 实验结果

对图4搭建的电路进行瞬态仿真,在不加入基带信号的情况下,观察锁相环的锁定过程,VCO输入控制电压VC和电容C1电压VC1的瞬态波形如图5所示。随着时间推移,当仿真进行到10s时,VC和VC1都稳定在0.5V,此时锁相环频率锁定在2.4GHz。

在此基础上,在锁相环工作10s后,加入500kb/s的基带信号,实现BFSK调制。此时,VC和VC1的瞬态波形如图6所示。加入基带信号后,基带信号反应在VCO控制电压的变化上,从而引起震荡频率的变化,而此时锁相环的锁定状态并没有因为基带信号的加入而发生变化。图7所示给出了基于锁相环两点调制的BFSK信号输出频谱。可见,在2.39GHz和2.41GHz处有两条清晰的谱线,满足最大频偏为10MHz的设计要求。

5 结语

锁相环综合实验分析了锁相环的数学模型和参数选择的依据,采用Verilog-A语言对两点调制锁相环电路模块进行了行为级建模,并对环路进行了瞬态仿真。实验表明,设计满足指标要求,为晶体管级设计和物理版图实现提供有力的设计基础。整个实验系统地涵盖了锁相环两点调制的关键知识和设计方法,对于将来从事射频集成电路设计和频率时钟电路设计的同学有较大的帮助。

参考文献

[1]张刚.CMOS集成锁相环电路设计[M].北京:清华大学出版社,2013.

[2]Ji J, Liu H, Li Q. A 1-GHz Charge Pump PLL Frequency Synthesizer for IEEE 1394b PHY [J]. Journal of Electronic Science and Technology, 2012,10(4):319-326.

[3]杨光义,闫燕莺,熊飏,等.锁相环调频发射接收系统[J].实验技术与管理,2014,(10):123-127.

[4]王延峰,郭淑婷,杜保强.基于锁相环路的教学方法[J].实验室研究与探索,2015,(3):177-180.

[5]徐妮.基于锁相环的线性相位调制器的关键技术研究[D].北京:清华大学,2014.

[6]汪大伟,岳丽娟,陈彩云,等.锁相环的相位模型与实验电路[J].大学物理,1999,(5):23-25.

[7]董在望.通信电路原理(第二版)[M].北京:高等教育出版社,2002.

[8]张涛,程耕国,邹雪城,等.CMOS锁相环频率合成器系统设计[J].武汉大学学报(自然科学版),2007,(5):533-537.

[9]马哲,蔡敏.一种精确的锁相环IP模块行为级建模[J].半导体技术,2006,(3):310-314.

[10]Accellera Systems Initiative Inc. Verilog-AMS Language Reference Manual (Version 2.4.0)[EB/OL].(2014-05).

[11]Liu L, Yang Y, Zhu Z. System Design of PLL Based on Behavioral Model Using Verilog-A [J]. Chinese Journal of Electron Devices, 2004, 27(2): 324-328.

[12]Liu L, Yang Y, Zhu Z. Design of VCO based behavioral model using Verilog-A[J]. Journal of Circuits and Systems, 2005,10(6): 25-28.