一种电离层观测雷达的数字处理系统设计

2018-01-18李涛吴琼之孙林彭程飞

李涛,吴琼之,孙林,彭程飞

(北京理工大学信息与电子学院,北京100081)

相控阵雷达技术开始应用于地球高层大气探测始于上世纪80年代[1]。经过近三十年的发展,随着理论研究的逐渐成熟,以相控阵为基础的高频相干散射雷达被广泛应用于地球高层大气及电离层等离子体特性的研究。其中具有代表性的是“超级双子极光雷达网(Super Dual Auroral Radar Network)”,该系统在对全球电离层观测过程中取得相当成就[2-5]。

用于电离层观测的相控阵雷达一般天线系统尺寸庞大,造价高昂,并且普遍架设于极端环境(高纬度极寒地区)。同时,为了科学研究的需要,雷达的工作模式和信号处理方法需要不断调整和改进。这决定了雷达的数字处理系统应具备高度集成化、高稳定性、低成本以及灵活易调试等特点。在对早期雷达数字系统充分调研的基础上,提出一种以FPGA为核心,软硬件全模块化的雷达信号处理及控制系统。

1 高频相干散射雷达系统简介

一套典型的用于电离层观测的高频相干散射雷达系统配备16套由水平极化天线组成的主天线阵列,同时配备由4套同样的天线组成的副天线阵列[6]。主副天线阵均呈均匀线阵排列。

雷达发射支路由数字系统产生携带相位信息的发射波形,经T/R组件完成功率放大后经天线发射;接收支路接收回波信号,经T/R组件直接由数字系统A/D采样,并在数字系统内部进行波束合成(DBF)处理。系统总体结构如图1所示。

图1 系统总体结构图

2 雷达数字系统

数字系统控制整套雷达系统工作。发射模式下利用DDS技术完成原始信号生成,并根据指定波束方向对原始信号幅度、相位进行校正,将校正完成的多路数字信号通过DAC器件转换为模拟电压发送至系统模拟部分。接收模式下利用高速ADC器件采样多通道回波数据,利用DDS技术完成数字正交下变频,将多路信号进行数字波束合成处理,并将处理结果打包上传至计算机。

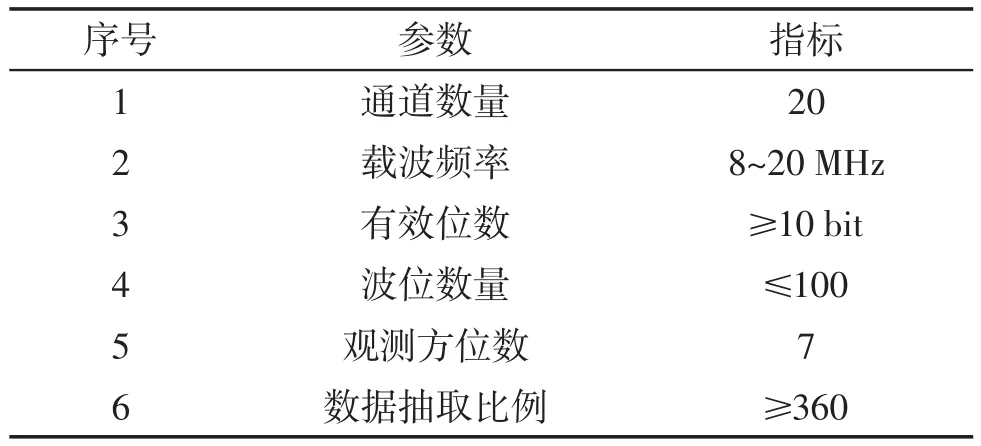

雷达数字系统关键参数指标如表1所示。

表1 雷达数字系统参数

2.1 参数分析

2.1.1 采样频率

受电离层特性影响[7],DAC器件所播放信号频率为8~20 MHz,依据奈奎斯特采样定律,采样频率至少为信号频率2倍。为保证DAC播放信号高信噪比,此处确定采样率为120 MH,精度为12 bit。

ADC器件采集信号频率范围为8~20 MHz。为保证较为简单的与DAC器件实现精确同步,确定DAC器件采样频率为60 MHz,两者采样率呈整数倍关系。

2.1.2 波束合成

20路接收信号分为主通道和辅通道两组分别进行波束合成(DBF)处理。DBF处理实质是对各通道数字正交下变频之后的复信号进行加权(复乘)求和,从而实现阵列天线波束合成[8-11]。主通道需要对16路接收信号进行并行7通道的DBF处理,7个通道按波位序列进行循环切换,最大波位数量为100。因此需要存储7组16×100的主通道加权矩阵。辅通道需要对4路接收信号进行单通道DBF处理,需要缓存1组4×100的辅通道加权矩阵。加权因子使用复数形式表示,实部虚部各占16 bit,因此总数据量为46.4 kB。FPGA片上存储资源即可满足需求。

2.1.3 数据速率

该雷达发射波形为一种被称为多脉冲序列的调制信号。目标的回波信号经AD采集后,在FPGA内部进行数字波束合成处理,处理结果送交数据打包模块上传存储。因此每个数据包的长度取决于当前多脉冲序列长度。

A/D以60MSps采样后又经过至少360倍抽取,每一路数据速率最高为166.7 kSps。该系统正常工作时每个多脉冲序列长度为88.8 ms,其中有1.2 ms处于非观测状态,处理结果为32 bit数据,可得每个多脉冲序列需要被打包的数据总量约为3.74 Mbit,平均数据速率约为42.1 Mbps。

2.2 硬件设计

数字系统的电路结构如图2所示。系统采用FPGA为控制核心。FPGA控制A/D芯片完成信号采集;控制D/A芯片完成信号播放;控制时钟分发芯片生成特定频率时钟信号供整个系统使用;通过RS422串口与T/R组件完成信息交互,并发送符合时序要求的开关量信号;接收GPS信号,提取时间信息;控制PCI桥芯片,完成FPGA与计算机的数据通信;通过Flash芯片固化FPGA程序,上电自动加载;通过DDR存储器实现数据缓存。

图2 系统电路结构图

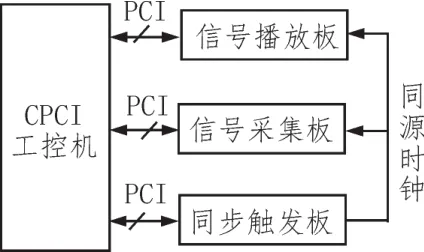

为简化设计,将上述电路划分为3块功能板卡分别实现,分别为信号播放板、信号采集板、同步触发板。每块板卡均拥有单独的FPGA控制核心。为保证在极端环境下系统可正常工作,采用具备高稳定性、高耐用性的CPCI架构整合硬件板卡。各板卡作为标准CPCI子板通过PCI总线实现与计算机通信。该设计在满足环境需求的同时还具备低成本,易扩展等优良特性。系统硬件构架模型及实物如图3、图4所示。

图3 整机板级模块组成结构

2.2.1 信号采集与播放

信号采集板卡接收20路接收机发送的模拟信号,采用10片ADI公司AD9269双通道ADC芯片完成模数转换。该芯片量化精度达到16 bit,最高采样速率可达80 Msps,这里采用60 Msps完成数据采样。为满足AD芯片差分输入需求,采用Mini-Circuits公司TC1-1T型号巴伦器件完成信号单端差分转换,后接RC低通滤波电路抑制带外干扰。

信号播放板卡需要为发射机提供20路播放信号,采用10片ADI公司AD9116双通道DAC芯片完成数模转换。为节约FPGA引脚,双通道DAC复用一组数据总线。AD9116为差分电流输出型DAC芯片,同样使用TC1-1T巴伦器件完成差分电流至单端电压的转换。为滤除DAC输出的阶梯波高频噪声,巴伦器件后接Mini-Circuits公司无源低通滤波器RLP-40+,该款芯片截止频率40 MHz,20 MHz频点处插损仅为0.6 dB。

图4 数字系统实物

2.2.2 系统同步

高频相干散射雷达作为相干系统,模拟系统与数字系统、数字系统内部各板卡之间均需严格的时钟同步。设计以低噪声锁相环芯片AD9520为核心的时钟链路。该芯片同时具备时钟分发能力,输出时钟抖动小于500 fs,满足系统对于有效位数要求[12-13]。

模拟系统提供外部时钟源输入数字系统的时钟分发芯片AD9520,该设计保证了模拟系统与数字系统之间同步;AD9520时钟分发芯片输出相位关系固定的三路时钟分别送至DAC、ADC以及FPGA处理器,该设计保证了数字系统内部的相干性。为便于调试,特地添加数字系统内部时钟源,该时钟由高精度温补晶体振荡器产生。

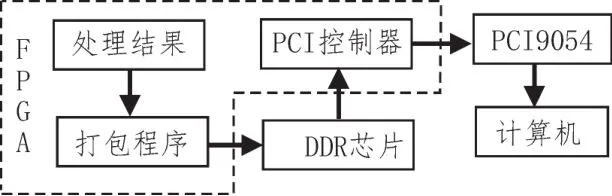

2.2.3 数据存储

FPGA与计算机之间通信通过PCI总线实现。为简化设计,采用PLX公司PCI桥芯片PCI9054进行内存地址映射,只在FPGA内控制PCI9054进行数据传输。PCI9054芯片极限传输速率为132 MB/s,满足系统最大传输带宽需求。

为增强系统稳定性,FPGA外部添加DDR芯片进行数据缓存,保证数据不会因计算机CPU异常而丢失。此处选用美光公司MT41J256M16芯片,单片容量256 MB,16 bit位宽数据总线。

数据存储链路框图5所示。DBF处理结果送入打包程序,添加特定包头包尾后送入外部DDR芯片进行数据缓存,此时若PCI总线处于空闲状态则PCI控制器立即从DDR芯片内读出数据完成数据传输。

图5 数据存储流程

2.3 FPGA软件设计

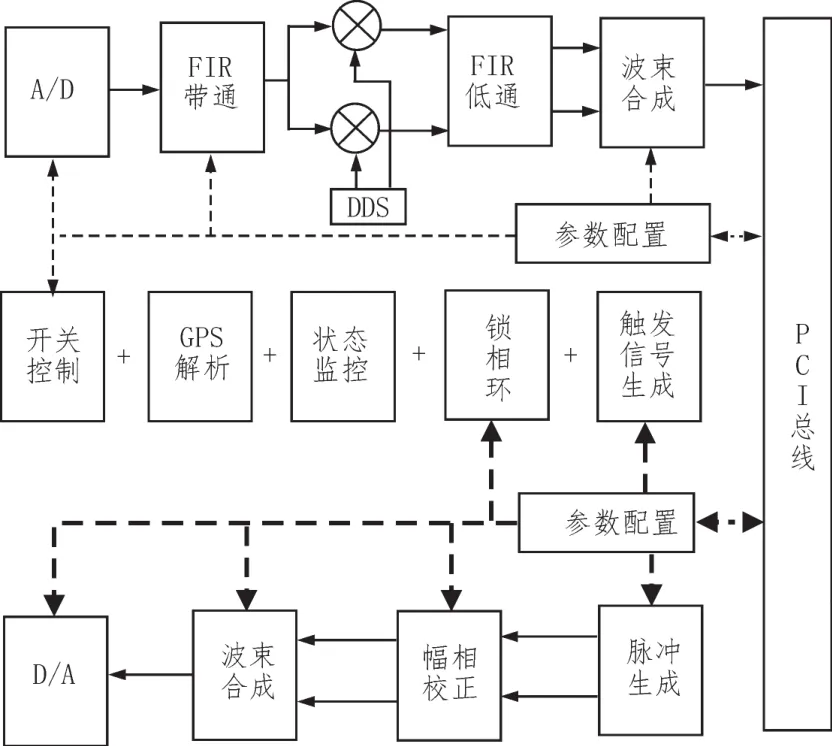

数字系统包含3块FPGA芯片,分别位于信号播放板、信号采集板以及同步触发板。主要实现如图6所示功能。

图6 FPGA软件结构图

播放板FPGA负责接收PCI配置参数,生成特定时序发射脉冲。完成一致性校正,对脉冲进行数字波束合成处理,并控制D/A芯片完成发射信号数-模转换。

采集板FPGA负责控制A/D芯片完成数据采样。对采样数据进行带通滤波、数字下变频、抽取、数字波束合成等处理,并将处理结果按照固定包格式打包上传。

同步触发板FPGA负责按照系统参数生成特定频率及相位关系的时钟作为其余板卡时钟源,并产生触发信号控制A/D与D/A的启动时刻以完成系统同步。接收GPS信号提取时间信息,控制T/R组件开启与关闭,并实时接收T/R组件工作状态。

2.3.1 参数配置

FPGA程序采用模块化设计思想,各模块拥有一定数量的寄存器,通过修改寄存器的方式满足不同应用需求。采用AXI-Lite协议完成寄存器配置。AXI-Lite协议包含32 bit地址总线与32 bit数据总线,地址总线用于寄存器选择,数据总线用于寄存器内容读写[14]。32 bit地址总线中高16 bit保留,中间8bit地址用于标识不同模块,低8 bit地址用于区分模块内不同寄存器。由此,FPGA程序最多允许256个模块,单个模块内寄存器数量可达256个。

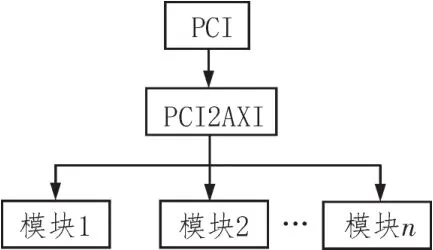

FPGA与上位机之间通过PCI通信,PCI2AXI程序完了PCI协议与AXI-Lite协议转换。由此实现上位机对FPGA内部任意寄存器的实时控制,这对系统调试及算法升级提供极大便利。如图7所示。

图7 AXI-Lite协议实现方式

2.3.2 信号播放

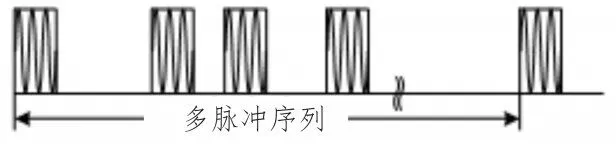

雷达发射波形为多脉冲序列,如图8所示。多脉冲序列内脉冲宽度、脉冲数量、脉冲间隔均为用户配置。多个多脉冲序列循环播放以实现不间断观测。

图8 多脉冲序列

FPGA接收PCI总线传来配置参数,使用DDS技术生成指定频率及相位的正交复信号,并根据时序进行脉冲调制。为了校正D/A及发射机各通道间幅相不一致性,在FPGA内部对原始脉冲进行数字幅相校正,由上位机实时下发校正因子。

校正后结果按照观测方位进行波束合成处理。通过合理组合各发射通道脉冲相位达到观测方向最大信噪比。最终由D/A控制程序将波束合成结果送至D/A芯片,完成数-模转换。

2.3.3 信号采集

FPGA控制10片A/D芯片按照60 Msps速率采样,得到并行20路原始数据。首先对原始数据进行带通滤波处理,抑制带外杂波。滤波器采用FIR结构[15-16],通带频率 8~20 MHz,矩形系数 0.75。该滤波器使用180 MHz时钟驱动以实现乘法器资源复用。

对带通滤波结果进行数字下变频处理,将原信号频谱搬移至零频。利用DDS技术产生与A/D采集信号同频的正交信号,乘法器完成混频处理并使用低通滤波器滤除高频分量。该低通滤波器同样采用FIR结构,滤波同时进行60倍抽取以降低数据速率。

波束合成模块接收下变频生成的20路正交复信号,其中16路为主天线阵列信号,其余为辅阵列信号,分别进行处理。主阵列实现并行7方位合成处理,观测范围3.25°;辅通道进行单方向合成处理。为实现大范围扫描,需按照用户设置的波位序列进行循环切换,不同波位对应不同观测方向。不同波位对应的波束合成因子预存于FPGA片内RAM中,工作时按照时序循环读取。

2.3.4 同步触发

同步触发板主要实现同步控制与系统状态监控。FPGA控制AD9520锁相环芯片选择适当时钟源(测试阶段为板载晶振,正常工作为外部时钟源)。通过SPI协议配置锁相环VCO频率,得到正确的时钟输出。其中发送给信号采集板的时钟频率为60 MHz,发送给信号播放板的时钟频率为120 MHz,发送给同步板自身的时钟为60 MHz,3个时钟保持固定相位关系。

为保证信号发射与采集交替进行,FPGA根据工作时序向采集板与播放板发送触发信号,两板卡根据该触发信号确定何时开始工作。为保证模拟系统与数字系统同步工作,FPGA生成开关信号控制发射机接收机开启或关闭。

FPGA通过UART协议与T/R组件进行通信,获取当前模拟系统温度、电压、电流等信息;通过UART协议与GPS芯片进行通信,获取时间信息。FPGA将获取的监控信息打包后通过SPI协议以CPCI背板为介质直接发送至信号采集板,以备上位机查询。

3 结论

该系统采用模块化思想进行软硬件设计,在实现相控阵雷达信号处理及系统控制等功能的前提下,充分考虑了随科学研究进展所带来的软硬件更新需求,具备高度的可扩展能力。系统在稳定性方面的设计使其可以正常工作于极端环境下,并具备造价低廉、调试方便等优良特性。该设计在某重点科学工程中得到应用,经验证工作稳定,满足设计要求。

[1]万卫星,徐寄遥.中国高层大气与电离层耦合研究进展[J].中国科学:地球科学,2014,44(9):1863-1883.

[2]Chisham G,Freeman M P.A reassessment of SuperDARN meteorechoes from the upper mesosphere and lower thermosphere[J].Journal of Atmospheric and Solar-Terrestrial Physics,2013(102):207-221.

[3]Fiori R A D,Boteler D H,Knudsen D,et al.Potential impact of Swarm electric field data on global 2D convection mapping in combination with SuperDARN radar data[J].Journal of Atmospheric and Solar-Terrestrial Physics,2013(93):87-99.

[4]CHEN Xiang-cai,LORENTZEN D A,MOEN J I,etal.F region ionosphere effects on the mapping accuracy of SuperDARN HF radar echoes[J].Radio Science,2016,51(5):490-506.

[5]Currie J L,Waters C L,Menk F W,et al.SuperDARN backscatter during intense geomagnetic storms[J].Radio Science,2016,51(6):814-825.

[6]Custovic E,Nguyen H Q,Devlin J C,et al.Evolution ofthe SuperDARN antenna:Twin Terminated Folded Dipole Antenna for HF systems[C]//Broadband and Biomedical Communications 20116thInternationalConference.IEEE,2012:1-5.

[7]刘二小,胡红桥,刘瑞源,等.中山站高频雷达观测结果初步分析[J].极地研究,2012,24(4):397-407.

[8]江涛,陈翼,王盛利.凝视数字多波束合成孔径雷达原理[J].现代雷达,2012,34(11):11-17.

[9]龚文斌.星载DBF多波束发射有源阵列天线[J].电子学报,2010,38(12):2904-2909.

[10]李春利.DBF体制接收系统的设计[J].现代雷达,2015,37(1):63-66.

[11]薛正辉,李伟明,任武.阵列天线分析与综合[M].北京:北京航空航天大学出版社,2011.

[12]熊文军,徐跃峰,闵康磊,等.10位高速模数转换器的超低抖动时钟设计[J].通信技术,2016,49(9):1250-1254.

[13]孙爱中,张琬珍,张斌峰.模转换系统有效位数超差分析[J].电子科技,2015,28(9):60-62.

[14]范秋香,吴琼之,孙宁霄,等.AXI标准协议在微型机载采集设备中的应用[J].电子设计工程,2014,22(3):62-65.

[15]Robert J S,Sandra L H.数字信号处理导论MATLAB实现[M].殷勤业,译.西安:西安交通大学出版社,2014.

[16]MEYER-BAESE U.数字信号处理的FPGA实现[M].刘凌,译.北京:清华大学出版社,2011.