数理统计和频谱分析的TIADC误差校正方法

2018-01-18杨扩军孔祥伟施佳丽

杨扩军,孔祥伟,施佳丽,叶 芃

(1. 电子科技大学自动化工程学院 成都 611731;2. 武汉第二船舶设计研究所 武汉 430205;3. 四川建筑职业技术学院信息工程系 成都 610399)

电子测试仪器、宽带通信和雷达等电子系统对高速数据采集系统提出了越来越高的要求。采样率作为数字示波器领域一个最核心的指标之一,直接决定了示波器的档次与应用场合。然而由于集成电路工艺的限制,在高速ADC方面国内外差距较大,这极大限制了国内以ADC为核心的高速数据采集系统的发展,从而制约了高档仪器、通信及雷达等系统的进步。因此,研究为提高实时采样率而采用的多片ADC并行时间交替结构(即TIADC结构)意义重大,对于打破国外技术封锁与垄断具有十分重要的现实意义。但是多片ADC之间失配带来的增益误差、偏置误差和时间误差却限制了TIADC系统的性能,因此对于各个误差的校正是TIADC系统中非常重要的研究内容。

关于TIADC的误差校正,大量文献对此进行了研究,并提出了若干误差估计与校正的方法。文献[1-3]提出校正误差的自适应校正方法,但是这种校正方法需要多次迭代计算,运算量大,不利于工程实现;文献[4-10]通过各种滤波器(如Farrow、Lagrange)进行校正,虽然可以达到的精度较高,但是滤波器的设计普遍复杂度较高;文献[11]利用基于正弦拟合的TIADC误差校正方法,该方法实现较简单实用性较强,但是偏置误差校正精度不高。

本文提出的数理统计误差校正方法用于TIADC的偏置误差校正,频谱分析的方法用于增益和时间误差的校正。以某个通道作为基准,对各个子ADC采样的数据进行数理统计,排除偶然因素带来的偏离很大的量化点,得到各个子ADC的偏置误差,根据误差的估计值得到相应的校正值。为了提高校正精度,提出了一种二次校正方法,使校正结果精度更高。而频谱分析的方法是利用FFT对子ADC采样数据进行频谱分析,通过对特定频点上的幅度、相位计算得到相应的增益和时间误差估计值,进而得到相应的增益、时间误差校正值,该方法实现简单,工程应用性极强,且精度高。

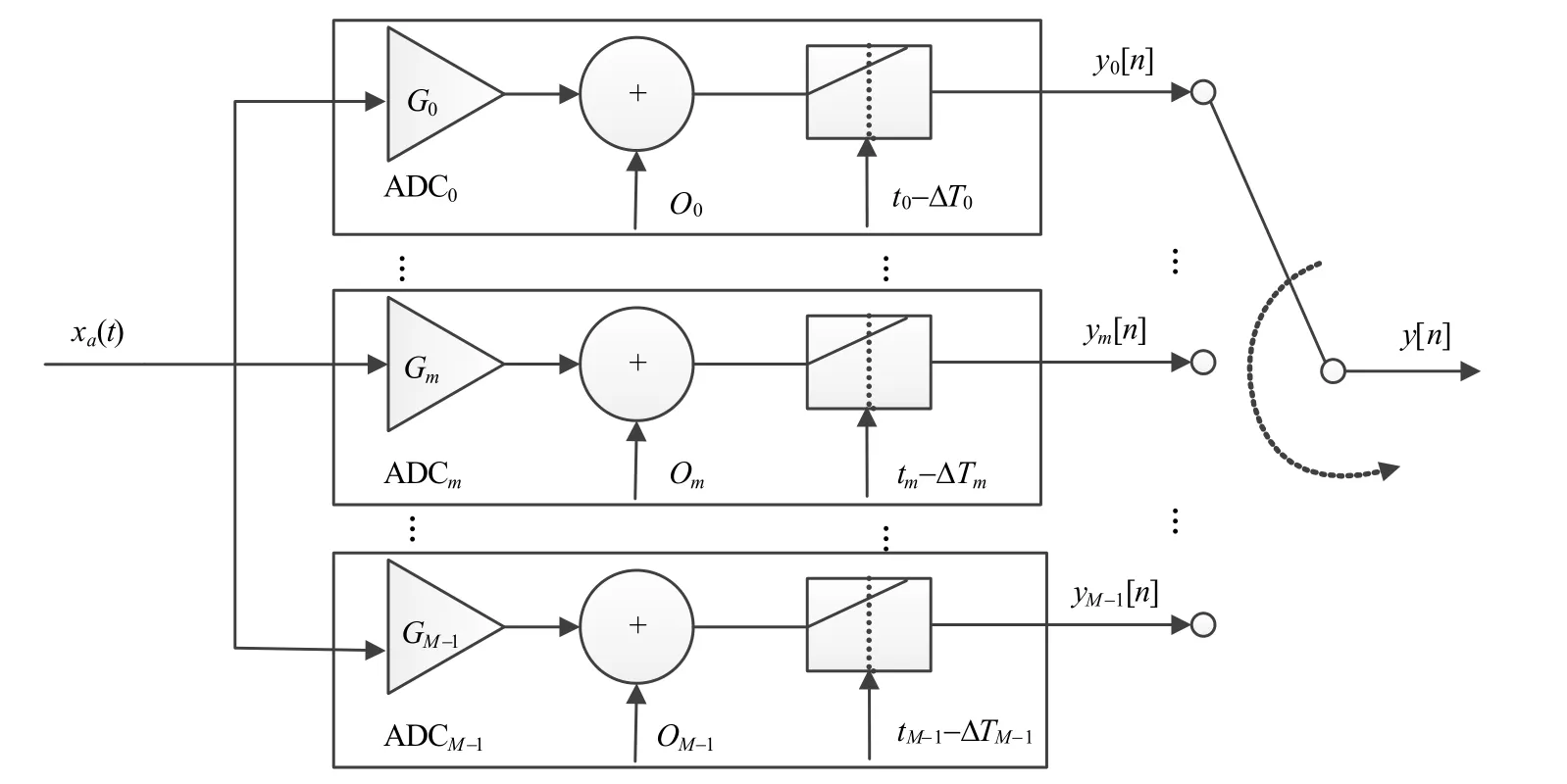

1 TIADC并行采集系统误差建模分析

图1所示为TIADC系统误差模型,图中,M为子ADC的个数,m表示通道索引号。Gm、Om分别代表ADCm的增益、偏置,如果以ADC0为参考通道,那么Gm、Om与G0、O0间的偏差就是增益与偏置误差。由时间交替采样原理可得,理想情况下ADCm的采样时刻为:

式中,Ts为整个TIADC系统的采样周期,对应的采样率为fs。考虑到存在的时间误差ΔTm(代表实际采样时刻与理想采样时刻之间的偏差),则实际的采样时刻是tm-ΔTm。

图1 TIADC系统误差模型

由式(1)及图1可得存在误差时ADCm的量化输出为:

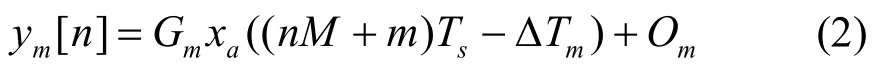

由模拟信号xa(t)与其采样序列x(n)=xa(t)|t=nTs=xa(nTs)频域之间的关系:

以及DTFT的线性性质可以得到式(2)存在误差时ADCm的量化输出的DTFT变换为:

式中,ω为对应子ADC的MTs采样周期的数字频率。即ω0=Ω0MTs,根据奈奎斯特采样定理,输入信号的最高频率为fs/2。那么Ω>|πfs|时,Xa(jΩ)=0。所以式(4)可以改写为:

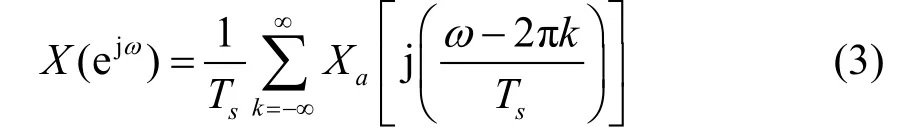

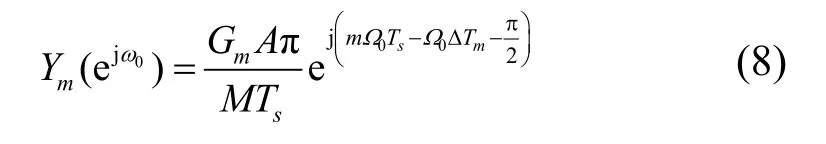

若xa(t)=Asin(Ω0t)=0,它的初相为0,则ADC0的采样点的初相也为0。把输入信号的傅里叶变换Xa(jΩ)=Aπ(δ(Ω-Ω0)-δ(Ω+Ω0))/j 带入式(5),得到ADCm在输入正弦信号时候的输出频谱为:

对式(6)令ω0=Ω0MTs,得到ω0处的带误差的输出频谱为:

如果Ω0<πfs/M,即输入信号使单个子ADC也满足奈奎斯特采样定理,则式(7)进一步化简为:

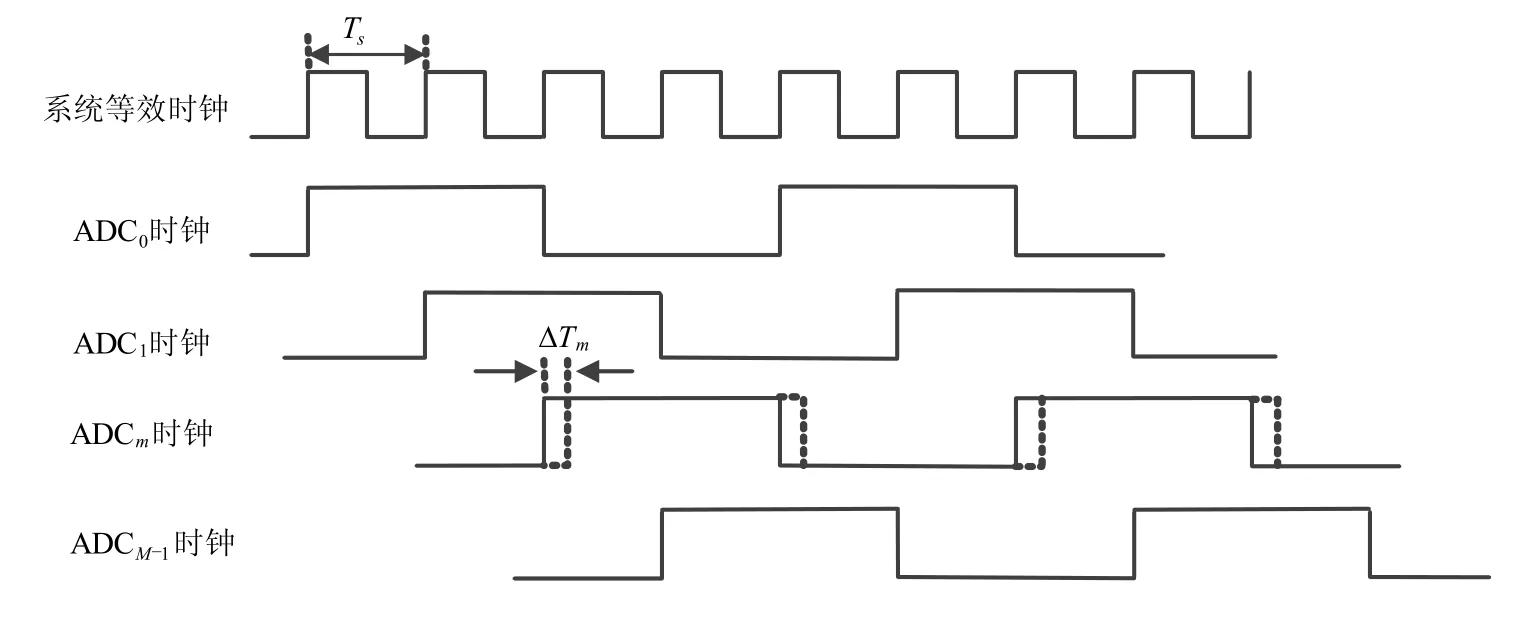

从式(8)可以得到Gm、ΔTm反应在ω0处的幅度、相位上,那么通过ω0处的幅度、相位信息可以得到ADCm的增益时间误差的估计值。TIADC系统的时间误差如图2所示。

图2 TIADC系统的时间误差

2 算法验证硬件平台简介

算法验证平台中采用M=4片采样率为1.25 GS/s的子ADC进行前端并行逐次采样,并通过后端拼合的技术使整个系统的等效采样率达到5 GS/s。子ADC有相应的偏置、增益、相位控制器用于进行相应的调整,这些控制器采用SPI串行协议通过在相应寄存器写入不同的控制字的方式来进行调节。而如何根据TIADC系统中的误差来调节偏置、增益、相位控制器是本文研究的关键。

图3 5 GS/s TIADC系统原理框图

整个5 GS/s TIADC系统的原理框图如图3所示。采用的是e2v公司的8 bit ev8aq165,该芯片内部集成的4片1.25 GS/s采样率的子ADC构成了采样率fs为5 GS/s的系统,采用ADC+FPGA+DSP的架构。在FPGA中可以方便快速的作FFT运算,迅速实时地获得频谱分析数据。它的偏置、增益、相位调节寄存器的调节范围是0~0x3ff,默认控制字Default CtrWord是0x200。偏置的调节范围是±20LSB,发送0x200(默认值)表示偏置调整量为0,大于0x200表示偏置变小,每个步进为0.039LSB,控制字变化约25才使增益变化1LSB,这也对校正方法的精度提出了很高的要求。增益的调节范围是±10%,每个步进是0.02%,发送0x200(默认值)表示增益调整量为0,大于0x200表示增益调整量变大。时间误差的调节体现在相位控制字上,相位调节寄存器的调节范围是±15ps,相应的每个步进是30 fs。发送0x200(默认值)表示相位调整量为0,大于0x200表示相位调整量变大。所有的误差都是在默认控制字DefaultCtrWord为0x200基础上校正。

3 数理统计的偏置误差校正方法

3.1 偏置误差的估计

由式(2),如果输入信号xa(t)为一定值,如xa(t)=0,则ADCm的量化输出为:

即输入为0时ADCm的量化输出是ADCm的偏置Om。以ADC0作为参考,则Om与O0之差就是偏置误差。

求Om最大的障碍是随机噪声的影响,随机噪声会使量化值在一个范围内上下波动。图4是对量化值的数理统计,可以看出,随机噪声使个别量化值偏离中心值较远,它们的频数远小于统计的总点数,工程上认为小于10倍就是远小于。本文算法的统计总点数N设置为2 000,认为频数小于N/20的点数是偶然因素的影响,这里采取直接剔除的滤波方式,图4中将量化值为124、125、130和131直接剔除。

图4 对量化值的数理统计

对于其他的点,采用加权平均的方式来消除随机噪声的影响,得到ADCm偏置的公式为:

式中,i表示ADCm的量化值;pi表示i出现的频数。

3.2 偏置误差的校正

得到ADCm的偏置Om后要对ADCm发送相应的控制字,进行偏置误差的校正。根据前面的介绍,控制是在默认控制字DefaultCtrWord为0x200的基础上调节,步进stepoffset为0.039,则校正的控制字为:

在一些特殊情况中,ADC可能没有偏置调节控制器,这时仍然利用式(10)求出各个子ADC的偏置,然后通过数字校正的方法在ADCm的量化输出值上减(Om-O0)来校正偏置误差。

3.3 偏置误差的二次校正

实际校正中发现,采用数理统计方法能较好地校正TIADC的偏置误差,但是仅仅一次校正不能将误差降为最低,一次校正后仍然存在误差,并且通过对一次校正后的量化数据作FFT,在相应的频点仍然存在偏置误差带来的误差谱,这将在后面给出详细结果。这是由于实际的ADC器件不能够做到完全的控制均匀。如同样是发送控制字的变化为85,如果当前控制器的起点不同,如一个是400,一个是800,那么实际系统中偏置的变化量不完全相等。尤其是对偏置误差本来就较大的TIADC系统这种影响更加严重。

本文提出了一种对于偏置误差的二次校正算法,即对一次校正的结果进一步进行二次校正,用以消除误差校正系统控制不均匀的问题。第二次校正方法跟一次校正方法基本相同,不同的是初始ADC控制字为第一次校正的结果。整体来看,第一次校正是一个粗校正,第二次校正是一个精校正。所以整个偏置误差的校正包括一次校正、二次校正两次校正过程,两次校正后误差校正精度非常高。

4 频谱分析的增益误差、时间误差校正方法

4.1 增益、时间误差的估计

由式(8)可知,如果输入模拟角频率为Ω0的单一正弦信号到TIADC的各个子ADC,单个ADCm在Ω0处的输出频谱与Gm成比例关系,因此通过Ω0处的频谱幅度来估算Gm的值。同时,设定ADC0的采样点对应初相为0的采样时刻,那么ADCm在Ω0处频谱的相位是mΩ0Ts-Ω0ΔTm-π/2。进而可以得到增益误差和时间误差的具体表达式为:

式中,Amplitudem、Amplitude0分别表示ADCm、ADC0在Ω0处的频谱的幅度值。

式中,phaseADCm、phaseADC0为子ADCm、ADC0输出频谱在输入频率Ω0处的相位。

由于FFT系统的精度及截断误差等的影响,对ADCm的采样数据作频谱分析时,每次得到的频谱幅度会有差异,需要进行相应的数字处理。本文采用做10次FFT,去掉两个最大、最小值求平均的方法得到最终的幅值。

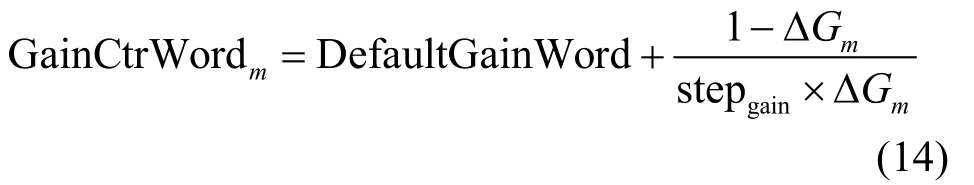

4.2 增益误差和时间误差的校正

误差的校正是发送校正控制字到ADCm,根据前面的介绍,增益的控制字步进stepgain是0.02%,则发送的增益校正控制字为:

另外,由于增益误差体现在Ω0频点的幅度上,不存在误差时,各个子ADC在Ω0频点上的幅度应相等。也可以通过连续发送控制字的方式来校正,如果发送的控制字最终使ADCm在Ω0频点上的幅度值与ADC0的相应幅度值相等,则校正完毕。

在ADC没有增益控制器的特殊情况中,利用式(12)求出增益误差,通过数字校正的方法来校正增益误差。

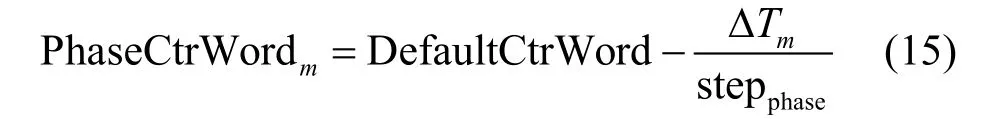

接下来要校正时间误差,为了能更准确地估计和校正时间误差,需要先保证TIADC系统已经按照前面的方法校正完偏置和增益误差。首先根据式(13)得到ADCm的时间误差估计,然后对时间误差发送相应的控制字来校正误差。一个控制字的步进stepphase是30 fs,则发送的校正控制字为:

同样,由于时间误差ΔTm为0时,ADCm与ADC0输出频谱在Ω0处的相位差为定值mΩ0Ts,也可以通过连续发送控制字的校正方式,直到ADCm与ADC0在Ω0处的相位差为定值mΩ0Ts,校正完毕。

在ADC没有相位控制器的特殊情况中,利用式(13)求出时间误差,通过数字校正的方法设计分数延迟滤波器来校正时间误差。分数延迟滤波器已有大量研究,限于篇幅和文章的重点,不再讨论。

5 实验验证及结果分析

5.1 偏置误差的验证及结果分析

将TIADC系统输入量设置为0,对TIADC系统进行校正,对校正前后的信号作FFT。由文献[12]可知,偏置误差在nfs/M处存在误差谱,而增益与时间误差在nfs/M±fin处存在误差谱,为了更清楚直观地观察到偏置误差造成的影响,在作FFT时同样对TIADC系统的输入设置为0,这样增益和时间误差的影响不会显示在频谱上,即只观察偏置误差的影响。图5为校正前的信号频谱图、偏置误差进行一次校正后的频谱图和偏置误差进行二次校正后的频谱图,图中纵坐标单位为dB,是对FFT的结果X(k),k=0,1,2,…,N-1的幅度值取对数后的值。

图5 校正前、偏置误差一次校正后、偏置误差二次校正后的频谱图

校正前的信号频谱如图5a所示,可以看到,在1.25、2.5 GHz频点上存在明显的失真,这正是由于偏置带来的误差谱。

图5b为对偏置误差进行一次校正后的频谱图,从图中可以看出通过一次校正后频谱得到了明显改善,在1.25 GHz频点上幅度由原来的73.023 6 dB下降到了52.084 5 dB,2.5 GHz频点上的幅度由64.562 9 dB下降到了28.299 5 dB。可见,一次校正取得了较好的效果。

图5c为对偏置误差进行二次校正后的频谱图,从图中可以看出经过二次校正后频谱得到了进一步的改善,1.25、2.5 GHz频点处偏置误差大大减小,没有明显的误差谱,幅度与噪底基本一致。

再来观察校正前后示波器输入为0时实际波形的变化,图6a为校正前示波器输入为0时的波形情况,可以看出波形由于4片子ADC偏置误差较大,导致波形拼合显示出来极其糟糕。

图6 校正前、一次校正后、二次校正后的信号波形

图6b为一次校正之后的信号波形,看到波形效果有了明显的改善,但是仔细观察也会发现在波形边缘仍然存在部分由于偏置带来的误差。图6c为二次校正后的信号波形,可以看出波形平整,仅出现个别随机噪声的影响,显示效果非常好。

下面将本文数理统计的偏置校正方法与文献[11]中的正弦拟合算法做一个对比。

图7是正弦拟合算法校正后的结果,通过对比发现,正弦拟合算法虽然能够较好地校正偏置误差,但是校正结果远不如本文算法,甚至比一次校正的结果还要略差。在1.25 GHz处误差谱是56.110 0 dB,2.5 GHz处的误差谱也有45.153 6 dB。可见,数理统计的偏置误差校正方法能够很好地校正偏置误差且精度高、效果非常好。

图7 正弦拟合算法校正后的结果

5.2 增益和时间误差的验证及结果分析

将输入信号设置为156.25 MHz,同时将ADC0作为参考通道,进行增益和时间误差的校正,同样通过对比校正前后频谱说明本文算法的有效性。选择156.25 MHz作为输入信号的原因是,1.25 GS/s的子ADC刚好可以在输入信号的一个周期内采集整数个点,并且作FFT时156.25 MHz是固定在FFT输出序列的特定点上,这样输入信号的能量集中在FFT的一个点上,使幅度相位信息更加准确。

由文献[12]可知,增益和时间误差在nfs/M±fin处存在误差谱,可知输入156.25 MHz的情况下在1.09、1.40、2.34 GHz频点出现误差谱。

为了清楚观察增益与时间误差,TIADC系统首先较正好偏置。图8a是校正前的误差频谱,可以看出在1.09、1.40、2.34 GHz频点均出现了明显的误差谱,这是增益和时间的误差造成的。此时系统的SNR为38.212 dB(已经对偏置误差进行校正),对应有效位数为6.05 bit。

图8b是用频谱分析的误差校正算法校正后的频谱图,可以看到误差谱得到明显改善。校正后的SNR提高到了41.019 4 dB,有效位数提高到了6.52 bit。可见,频谱分析的误差校正方法能够起到很好的作用,大大降低误差谱,提高了TIADC系统的SNR和有效位数。

同时将本文算法与文献[11]中的正弦拟合算法进行对比。为了仅对比增益与时间误差,同样将偏置误差先校正完毕,并且两种算法输入相同频率相同幅度的正弦信号进行校正。图9是用正弦拟合算法校正后的信号频谱,可以看出正弦拟合算法同样使误差频谱得到明显改善,在nfs/M±fin频点处两种校正方法结果基本一致。使用校正后系统的SNR变为40.794 4 dB,与文献[11]中的结果基本一致。

图8 增益时间误差校正前、后频谱

图9 用正弦拟合算法校正后的信号频谱

通过分析结果可看出频谱分析的增益校正方法能够很好地校正TIADC的增益和时间误差,由于可以采用FPGA的FFT IP core,实现较简单,且精度高。

6 结 束 语

本文的最大特点是从工程出发,讲究实用性。数理统计的偏置误差校正方法实现简单,精度很高,明显优于常用的的正弦拟合算法,并且它的校正不需外接信号,结合数理统计的数据分析优势能很好估计误差值。该方法可以排除控制不完全线性的二次误差校正方法,误差谱能降到与噪底一致。缺点是受ADC偏置误差控制器的精度制约,二次校正的优势在偏置控制器精度高时才能充分体现出来。频谱分析的增益和时间误差校正算法原理简单,实现较容易,校正精度达到了正弦拟合算法的精度。该算法虽然有做FFT来获取子ADC频谱信息的缺点,而FFT需要比较长的时间,这样降低了时效性,但是可以通过FPGA内部的IP核来最大限度地简化设计难度、减少运算时间,将会成为工程中实用的增益和时间误差校正方法。

[1]PAN Hui-qing, TIAN Shu-lin, YE Peng. An adaptive synthesis calibration method for time-interleaved sampling systems[J]. Metrology and Measurement Systems, 2010,17(3): 405-414.

[2]田书林, 潘卉青, 王志刚. 一种并行采样中的自适应非均匀综合校准方法[J]. 电子学报, 2009, 37(10):2298-2301.TIAN Su-lin, PAN Hui-qing, WANG Zhi-gang. An adaptive synthesis calibration method for time delay of sampling systems[J]. Acta Electronica Sinica, 2009, 37(10):2298-2301.

[3]王亚军, 李明. TIADC通道误差自适应修正方法[J]. 西安电子科技大学学报, 2013, 40(3): 27-35.WANG Ya-jun, LI Ming. Novel adaptive method based on the Taylor series to compensate channel mismatches of TIADC[J]. Journal of Xidian University, 2013, 40(3): 27-35.

[4]ZOU Y X, ZHANG S L, LIM Y C, et al. Timing mismatch compensation in time-interleaved ADCs based on multichannel lagrange polynomial interpolation[J]. IEEE Transactions on Instrumentation and Measurement, 2011:60(4): 1123-1131.

[5]EGHBALI A, JOHANSSON H, SARAMAKI T. A method for the design of Farrow-structure based variable fractionaldelay FIR filters[J]. Signal Processing, 2013, 93(5):1341-1348.

[6]SHAHMANSOORI A. Reconstruction of periodic nonuniform samples using Lagrange interpolation in time-interleaved ADCs[J]. Signal Image and Video Processing, 2015, 9(2): 471- 479.

[7]刘进军, 吕幼新, 王洪. 并行ADC采集系统的时间误差测量与校正[J]. 电子科技大学学报, 2005, 34(6): 736-739.LIU Jin-jun, LÜ You-xin, WANG Hong. Measure and calibration of time error in parallel ADC[J]. Journal of University of Electronic Science and Technology of China,2005, 34(6): 736-739.

[8]SCHMIDT CA, COUSSEAU J E, FIGUEROA J L, et al.Efficient estimation and correction of mismatch errors in time-interleaved ADCs[J]. IEEE Transactions on Instrumentation and Measurement, 2016, 65(2): 243-254.

[9]EL-CHAMMAS M, MURMANN B. A 12-GS/s 81-mW 5-bit time-interleaved flash ADC with background timing skew calibration[J]. IEEE Journal of Solid-State Circuits,2011, 46(4): 838-847.

[10]刘艳茹, 田书林, 王志刚, 等. 一种FARROW行滤波器的并行采样时间误差校正[J]. 电子测量与仪器学报,2010, 24(1): 50-54.LIU Yan-ru, TIAN Shu-lin, WANG Zhi-gang, et al. A sample-timing error calibration for time-interleaved ADC based on Farrow filter[J]. Journal of Electronic Measurement and Instrument, 2010, 24(1): 50-54.

[11]杨扩军, 田书林, 蒋俊, 等. 基于TIADC的20 GS/s高速数据采集系统[J]. 仪器仪表学报, 2014, 35(4): 841-848.YANG Kuo-jun,TIAN Shu-lin, JIANG Jun, et al. 20 GSPS high speed data acquisition system based on TIADC[J].Chinese Journal of Scientific Instrument, 2014, 35(4):841-848.

[12]VOGEL C. The impact of combined channel mismatch effects in time-interleaved ADCs[J]. IEEE Transactions on Instrumentation and Measurement, 2005, 54(1): 415-427.