宽带数字信道化接收机的FPGA实现

2018-01-11冷鹏飞徐朝阳

冷鹏飞,徐朝阳

(中国船舶重工集团公司第七二三研究所,江苏 扬州 225001)

宽带数字信道化接收机的FPGA实现

冷鹏飞,徐朝阳

(中国船舶重工集团公司第七二三研究所,江苏 扬州 225001)

宽带数字信道化接收机具有覆盖频段宽、灵敏度高、动态范围宽、截获概率高以及实时处理能力强等特点,是目前侦察接收机中较好的解决方案。论述了一种基于多相滤波的宽带数字信道化接收机结构,并通过FPGA布局布线后仿真验证其有效性及可实现性。

宽带接收机;信道化;多相滤波;现场可编程门阵列

0 引 言

电子侦察接收机是电子情报保障体系中的重要组成部分,它可以截获、分析、识别和定位作战区域内的雷达辐射源,为己方提供直接的情报支援和决策依据[1]。在实际电子战环境下,雷达信号时域分布密集且频域覆盖范围大,为实现信号的全概率测量,数字宽带接收机的信道化技术是一种实用且有效的方法[2]。本文论述了一种宽带数字信道化接收机的现场可编程门阵列(FPGA)实现方案,并通过布局布线后仿真验证了方案的物理可实现性。

1 基于多相滤波的高效信道化结构

1.1 信道化基本原理

信道化的基本原理是将输入的全带信号进行频带划分即将侦收到的信号分解成若干个不同的频段,又称为子频带或子信道,然后对各子信道分别处理。

信道的划分即窄带滤波器组的设计,本设计中该窄带滤波器组的频率响应如图1所示。各子信道通带带宽为Br=fs/K,信道带宽为B=2fs/K,中心频率为fk=fs/ (2K) +kfs/K,其中K=64,为子信道数,k=0,1,…,63,为各子信道编号。

将截止频率为fs/(2K)、阻带边界频率为fs/K的原型低通滤波器调制至各子信道中心频率处即可实现上述窄带滤波器组。由于原型低通滤波器的频率响应存在过渡带,因而各子信道在幅度损耗为-3 dB处交叠,且相邻子信道间存在50%的频谱交叠。将输入信号送入各滤波通道,完成滤波后经数字下变频至基带即可获取各子信道输入信号包络,此时各子信道输出信号带宽降至2fs/K,故可以K/2倍抽取率对各子信道输出进行抽取,以降低后续处理压力。

由于设计面向宽带实信号的处理,所以根据实信号频谱的共轭对称性,取前32信道输出为最终输出结果。

1.2 多相滤波结构

设输入信号为x(n),原型低通有限冲激响应(FIR)滤波器的单位脉冲响应为h(n),长度为N,且满足N=KP,P为正整数,抽取率M=K/2,窄带滤波器组第k个通道单位脉冲响应为hk(n),于是第k个子信道输出为:

(1)

以抽取率M对yko(n)进行抽取后输出为

(2)

在数字角频域中,第k个子信道的中心频率为:

wk=2kπ/K+π/K

(3)

将式(3)代入式(2)并化简可得:

(-1)kn(-j)nfk(n)

(4)

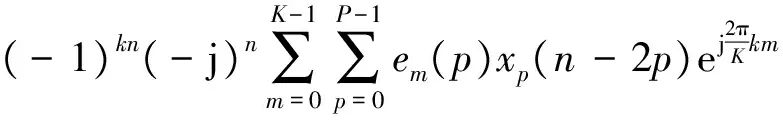

令i=pK+m,其中p=0,1,…,P-1,m=0,1,…,K-1,于是有:

(5)

令:

(6)

将式(5)、式(6)代入式(4),有:

(7)

式中:符号*为线性卷积运算;em(P/2)为序列em(p)2倍内插零的结果。

上述算法的实现结构如图2所示,x(n)按逆时针方向从信道0开始循环接通前32个信道,后32个信道的输入是前32个信道输入延迟1个时间单元的结果。从图中可以看出,各信道输入数据是对x(n)32抽取的结果,且各通道子FIR滤波器系数长度为原型滤波器的1/M,因而该结构可以降低FPGA处理数据的速度,从而节省硬件资源。此外,该结构抽取在运算模块之前,相较于运算完再抽取的方案更为高效。

1.3 Matlab仿真验证

分别将方波、余弦波、锯齿波调制至信道0、信道3、信道7的中心频率处,将其作为输入信号送入信道化接收机。由于实信号频谱共轭对称,所以信道63、信道60、信道56上信号包络分别与信道0、信道3、信道7上信号包络相同,载频不同。Matlab仿真结果如图3所示。

2 FPGA的实现

2.1 系统总框图

系统总框图如图4所示,采样后的数据经1∶8 demux后按4抽取送入各通道进行滤波,进而对滤波结果进行离散傅里叶逆变换(IDFT)运算,最后各通道乘以对应算子得到最终输出结果。

2.2 时钟分析

从图4可以看出,系统时钟为100 MHz,模/数转换器(ADC)输出数据速率为1 280 Msps,1∶8 demux模块输出数据速率为160 Msps,因而选择160 MHz时钟完成数据的按4抽取,而后续的运算模块则以200 MHz时钟完成运算。

由上述分析可知,在抽取模块与后续运算模块间进行数据传输时,存在160 MHz与200 MHz的异步时钟域同步化问题。本设计通过握手信号在抽取模块中实现同步化。

对于本设计而言,握手信号的实现主要考虑以下两方面问题:

(1) 转有效电平检测为时钟沿检测

图5描述了跨时钟域电平检测时产生的问题,由于200 M时钟频率高于160 M时钟,因而以160 M时钟域信号作为电平检测握手信号时会出现重复采集数据的情况,解决方法是通过时钟沿检测同步。

(2) 信号采集时序

图6给出了异步时钟域的同步时序,由于本设计中数据传输速率为40 Msps,而源时钟和目的时钟频率都较传输速率高出很多,因此,在时序问题上,主要需确保目的寄存器采样时输入数据稳定。图中,寄存器x_valid_r0,x_valid_r1,x_valid_r2用于实现上升沿检测,160 MHz时钟域的输出有效信号y_valid经200 MHz时钟“打两拍”存入寄存器x_valid_r1,以降低单bit数据在异步时钟域传输时出现亚稳态的概率。x_valid_r1与x_valid_r2作为200 MHz时钟域中上升沿检测电路的输入,输出为200 MHz时钟域中的x_valid,并以此信号作为电平检测信号同步异步时钟域间的数据传输。在时序上不难发现图示情况为时间余量T取最小值时波形,值为10 ns。在设计时,可以通过约束异步时钟域间最大数据传输路径延迟使设计满足时序要求,本设计中,最大路径延迟约束为160 MHz时钟周期6.25 ns。

2.3 FIR滤波器

原型滤波器为511阶FIR低通滤波器,其通带、阻带边界频率分别为π/64和π/32。各通道子FIR滤波器em(n)是对原型滤波器按64抽取并进行2倍内插零的结果。设计中主要有如下三方面考虑:

(1) 时序分析

滤波器输入输出数据速率均为40 Msps,运算处理时钟频率为200 MHz,因此可通过流水复用卷积运算模块5次以减少硬件资源的消耗。本设计中,16个卷积运算模块并行处理,每个模块由4个通道流水复用,余出1个时钟周期用于数据缓存。

图7给出了第m个卷积运算模块结构,输入数据通过并转串端口使数据流水输入卷积运算单元,输出端则通过串转并输出4个并行通道运算结果。卷积运算单元中间结果应暂存在寄存器、先进先出(FIFO)或双口随机存储器(RAM)中以确保前后运算数据通道一致,滤波器系数存在只读存储器(ROM)中,通过地址产生器同步系数与对应通道输入数据。

(2) 卷积运算单元

图8为单个通道卷积运算单元结构图,从图中可以看出,该模块由延迟单元、复乘运算单元以及流水加法运算单元组成。

该模块乘数因子em(n)是对511阶原型滤波器按64抽取并进行2倍内插零的结果,因此有效系数长度为8。输入信号xm(n)为实信号,所以2个乘法器即可实现复乘运算,于是可以算得整个滤波器模块消耗乘法器资源为16×8×2=256个。

(3) 卷积运算数据位宽的截取

卷积运算输入数据位宽为16 bits,em(n)是实虚部位宽均为16 bits的复序列,按上述结构运算输出数据位宽为35 bits。运算模块中,em(n)已知,可以求得:

(8)

于是可得该运算模块运算所得最大数据位宽为:

bmax=max{fbit[Imax],fbit[Qmax]}

(9)

式中:fbit[·]表示数据二进制表示形式的最小位数。

本设计中,bmax=27,所以可截取输出的bit26~bit11作为最终输出结果。

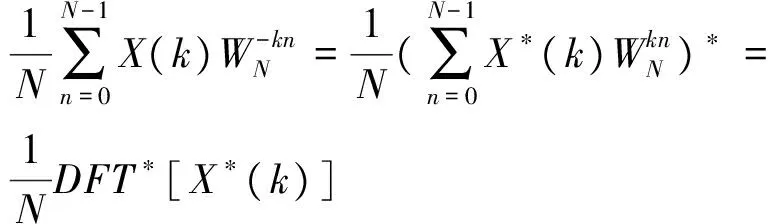

2.4 IDFT运算模块

设序列x(n)的DFT运算结果为X(k),则有[3]:

(10)

式中:符号*表示共轭。

因此,IDFT运算的实现即DFT运算的实现,本设计采用基4FFT算法实现64点DFT运算。

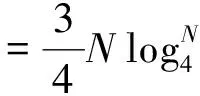

64点基4FFT算法共3层蝶形运算模块,每层蝶形运算模块有16个蝶形运算单元。每层蝶形运算模块输入数据速率为40 Msps,运算处理时钟频率为200 MHz,因此1个蝶形运算单元最多可以流水复用5次,至少需要ceil[16/5]=4个蝶形单元并行处理,其中ceil[·]表示取整。

图9给出了蝶形运算模块实现结构图。

数据缓存模块读取输入数据,并锁存数据至新数据到来。各模块间的运算协调通过状态机形成电子开关来实现。蝶形运算单元主要完成复乘加运算,理论上,每个蝶形运算单元需进行3次复乘运算,N点基4FFT复乘运算次数为:

(11)

当N=64时,CM=144。在实际应用过程中,第1层蝶形运算模块中旋转因子全为1,为减少乘法器的数目,这些旋转因子不做复乘运算。因此,FFT模块共消耗乘法器144-16×3=96个。

2.5 算子jn、(-j)n的乘法运算

算子jn、(-j)n随n呈周期变化规律,设计中用状态机实现这些乘法以减少对乘法器资源的浪费。

2.6 资源的消耗

表1给出了FPGA布局布线后资源消耗情况,芯片型号为XC7VX485T,各模块输入输出数据位宽为16 bits。结合前文分析可以看出,卷积运算消耗乘法器个数为256,FFT运算消耗乘法器个数为96,因此整个设计共消耗乘法器个数为352。

2.7 Modelsim仿真结果

Modelsim仿真结果如图10所示,图10(a)为前8个信道输出的功能仿真结果。图10(b)为布局布线后仿真结果,输出为各信道与Matlab仿真输出的误差,从图中可以看出两者之间误差很小。

表1 FPGA 布局布线后资源消耗情况

3 结束语

本文论述了一种基于多相滤波的宽带数字信道化接收机的FPGA实现方案,详细分析了FPGA设计过程中遇到的异步时钟域同步化、FIR滤波器的实现与卷积运算模块的位数截取以及64点基4FFT算法的实现等问题,给出了解决方案,最后通过布局布线后仿真验证了方案的物理可实现性。

[1] 王森.宽带数字信道化接收机FPGA实现技术研究[D].成都:电子科技大学,2008.

[2] 余锐.宽带DBF和数字信道化技术[D].西安:西安电子科技大学,2009.

[3] 丁玉美,高西全.数字信号处理[M].3版.西安:西安电子科技大学出版社,2009.

RealizationofWidebandDigitalChannelizationReceiverBasedonFPGA

LENG Peng-fei,XU Chao-yang

(The 723 Institute of CSIC,Yangzhou 225001,China)

A wideband digital channelized receiver has the characteristics of wide coverage frequency range,high sensitivity,large dynamic range,high interception probability and strong real-time processing ability,is a satisfied solution project in current reconnaissance receivers.This paper discusses a structure of wideband digital channelized receiver based on polyphase filtering technology,and validates the validity and realizability of the design through the simulation after placing and routing in field programmable gate array (FPGA).

wideband receiver;channelization;polyphase filtering;field programmable gate array

2017-05-24

TN971

A

CN32-1413(2017)06-0067-05

10.16426/j.cnki.jcdzdk.2017.06.014