基于单片机的PCM语音编码系统设计∗

2018-01-04王仲杰

王仲杰

(中国飞行试验研究院 西安 710089)

基于单片机的PCM语音编码系统设计∗

王仲杰

(中国飞行试验研究院 西安 710089)

针对传统数字处理信号方案在处理语音编码中存在性能差和成本高的问题,提出一种基于单片机技术低功耗、高性能语音编码系统。借助单片机技术的优势,同时根据传统PCM在语音编码方面的劣势,搭建以FPGA为主控芯片的语音编码控制模块,并引入ADPCM优化算法对语音编码进行处理,从而大大提高了语音编码系统的性能,减少了成本,实现了低功耗、高效的语音编码处理。最后通过仿真和硬件测试,验证了上述方案设计的可行性和合理性。

FPGA芯片;ADPCM优化算法;语音编码;硬件设计;仿真

1 引言

随着当前计算机技术和微电子技术的不断发展,数字技术也开始飞速发展,被应用在各个不同的行业和领域,并引发了数字系统设计理念的变革。当前,在数字信号处理领域之中,大部分采用的是传统的DSP处理方式,或者是一些专用的集成电力方案。虽然这些方案提高了数字信号处理的效率,但是还是存在性能差、成本高、开发周期长等缺点,制约着PCM算法的运行[1]。因此,如何借助现有的微电子技术完成大规模数字运算,并实现语音算法成为当前思考的重点。对此,本文提出一种基于FPGA的单片机语音编码系统,并注重就实现ADPCM算法的运行进行研究,从而提高当前的数字化处理效率。

2 FPGA简介

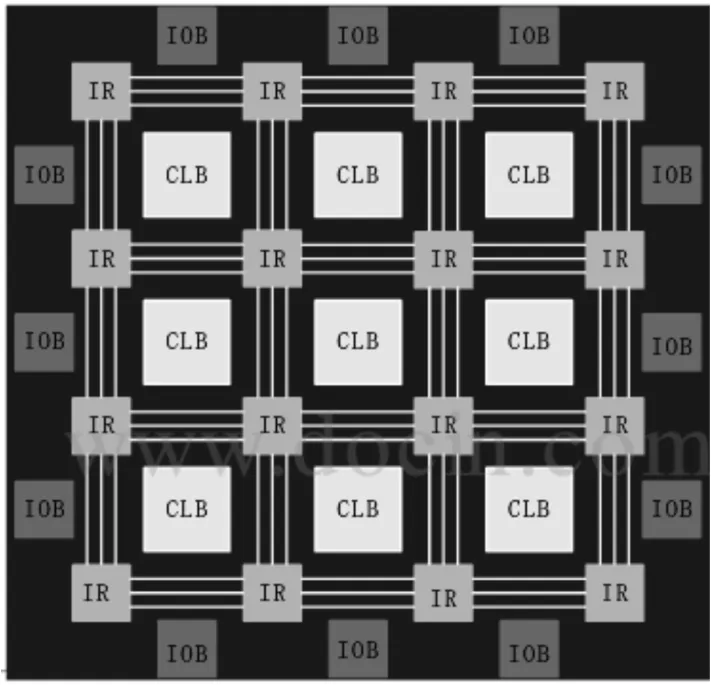

FPGA,中文全称为现场可编程门阵列,是在CPLD,EPLD,GAL,PAL等可编程逻辑器件基础上,逐步发展和演变而来的,是一种类似于掩膜可编辑门阵列的编程器件。FPGA作为一种半定制的产品,可以根据设计的数字系统要求,进行现场设置和修改。FPGA器件内部结构主要包括可编程逻辑块(CLB)、I/O可输入与输出、PIR互连资源块等构成,具体见图1所示。

对FPGA芯片的工作原理是通过查找表来实现对器件的可重复烧写。而查找表的原理在开发的数字逻辑系统中,会计算出相关的结果,然后逻辑运算的真值表被事先存入到查找表之中,它的输入则为逻辑运算的输入,而它的输出则为运算结果。当任何一个信号在输入到FPGA芯片后,都相当于是直接输入了某个具体地址来查找表,这个地址对应的计算结果就是输出结果。

图1 FPGA内部结构

而对于FPGA的开发通常都是通过硬件描述性语言Verilog HDL或者是VHDL来进行开发。这种开发语言的优点在于移植性好;电路与芯片工艺无关;输入效率高等特点。

3 ADPCM算法原理

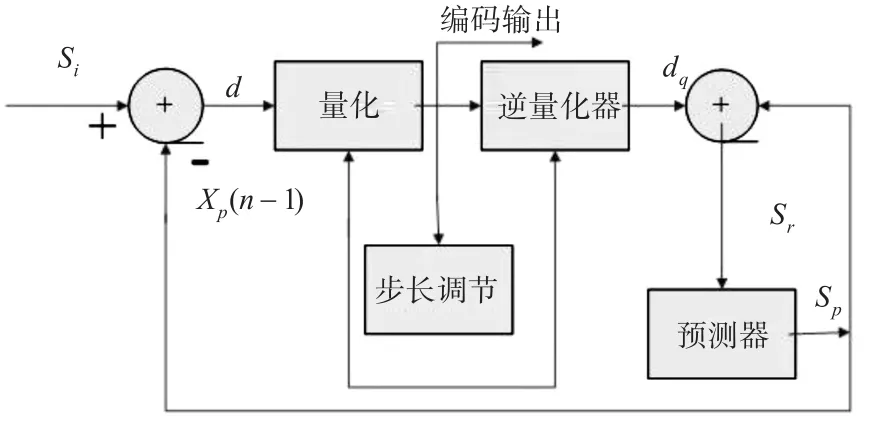

自适应差分脉冲编码调制(ADPCM),是综合了自适应脉冲编码调制(APCM)的自适应特性和差分脉冲编码调制(DPCM)的差分特性的一种波形编码算法。该算法具有延迟低、音质高等特点,从而在近些年来被广泛应用在数字语音信号处理方面。通过ADPCM算法,将传统的16bit的PCM数据直接压缩成大小为4bit的ADPCM数据,从而对数据进行传输和存储。该编码算法的核心是随着信号幅度的不断变化,通过量化间隔大小的方式进行自适应的调整;通过以前的样本值去估计接下来的抽样值,从而让接下来的抽样值与实际值更加接近。而这主要利用了信号前后存在相关性,从而可以通过自适应量化间隔的方式来实现对传统PCM数据的压缩。具体原理则如图2所示。

图2 ADPCM编码原理

其中,Si表示16bit二进制补码语音信号;Sp为预测采样值;d表示与线性输入Si之间的差值;XP(n-1)上一级的抽样值;dq表示编码输出I被逆化成的差值;Sr差值dq与预测采样Sp苏得到的解码输出值。

在图1的原理中,无论是对语音信号进行编码还是译码,都必须通过更新步长的方式,并借助其工作原理——量化步长索引调整表及其对应的值来实现步长值的更新。

4 编码系统硬件平台设计

要实现ADPCM对语音信息的优化处理,搭建有效的硬件平台是关键,也是基础。结合FPGA芯片的特点及编码系统功能需求,其硬件组成主要包括FPGA主控芯片、仿真接口JTAG、供电电源、LED显示、语音放大器、串口通信模块等,具体如图3所示。

图3 编码系统硬件平台设计

4.1 主控芯片选择

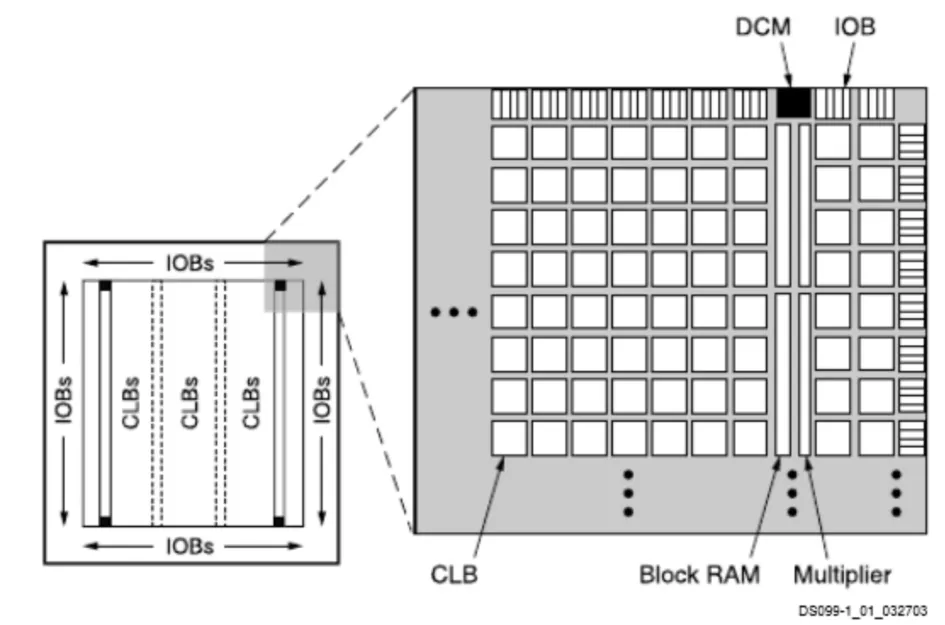

为提高该控制系统的运算处理能力,本文选择XC3S5000系列中的XC3S5000-5FGG676C型号。该系列芯片是由赛灵思推出的一款面向低端市场FPGA系列,具体结构如图4所示。

图4 XC3S5000系列芯片内部结构

该系列芯片典型的优势在于拥有104个18*18专用乘法器,同时拥有33280slice、104个RAM模块,大大提供了整体运算性能。

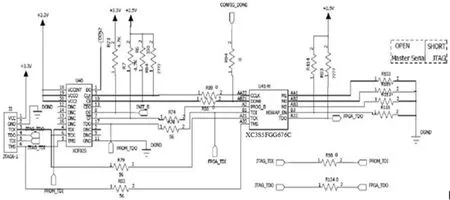

4.2 配置电路设计

在对FPGA的开发中,最为关键的一个问题就是硬件配置,必须通过专门的仿真器来实现。在配置体系中,包括仿真器、专门的编程软件和加载电路。配置模式也包括主串、从串等五种不同模式。本文则选择常用的主串模式。具体配置电路如图5所示。

图5 配置电路设计

5 ADPCM算法软件实现

根据ADPCM算法的原理,其主要是完成对语音信号的处理,即将PCM16bit信号通过压缩编码成为4bit的数据信号,然后在通过解码,得到初始的16bitPCM信号。因此,要实现ADPCM信号的处理,主要涉及三个步骤。

5.1 查找表设计

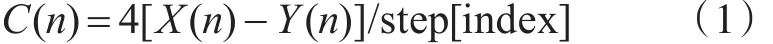

假设PCM输入值为X(n),前一时刻的预测值为Y(n-1),两者之间的差值为 D(n),编码值为C(n)。其中编码值的具体计算为

而根据公式(1)可以求解出下一次编码的量化步长值,具体计算为

同时还必须求取下一次编码的预测值,具体计算为

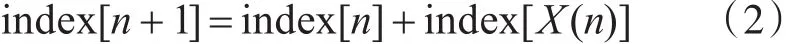

其中,∆=step[index]×C(n)/4+step[index]/8,step[index]表示量化步长表当中给出的步长值。具体索引表如表1。

表1 索引表

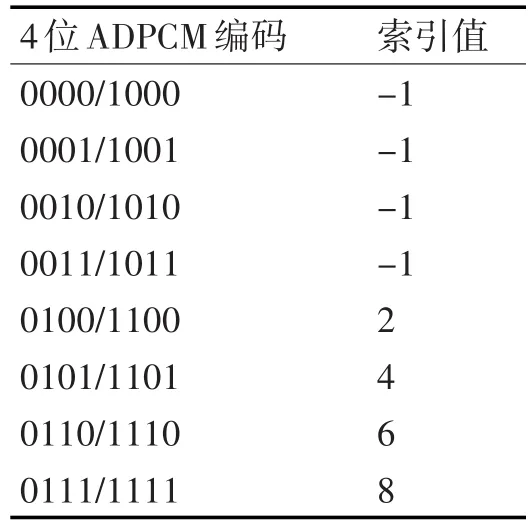

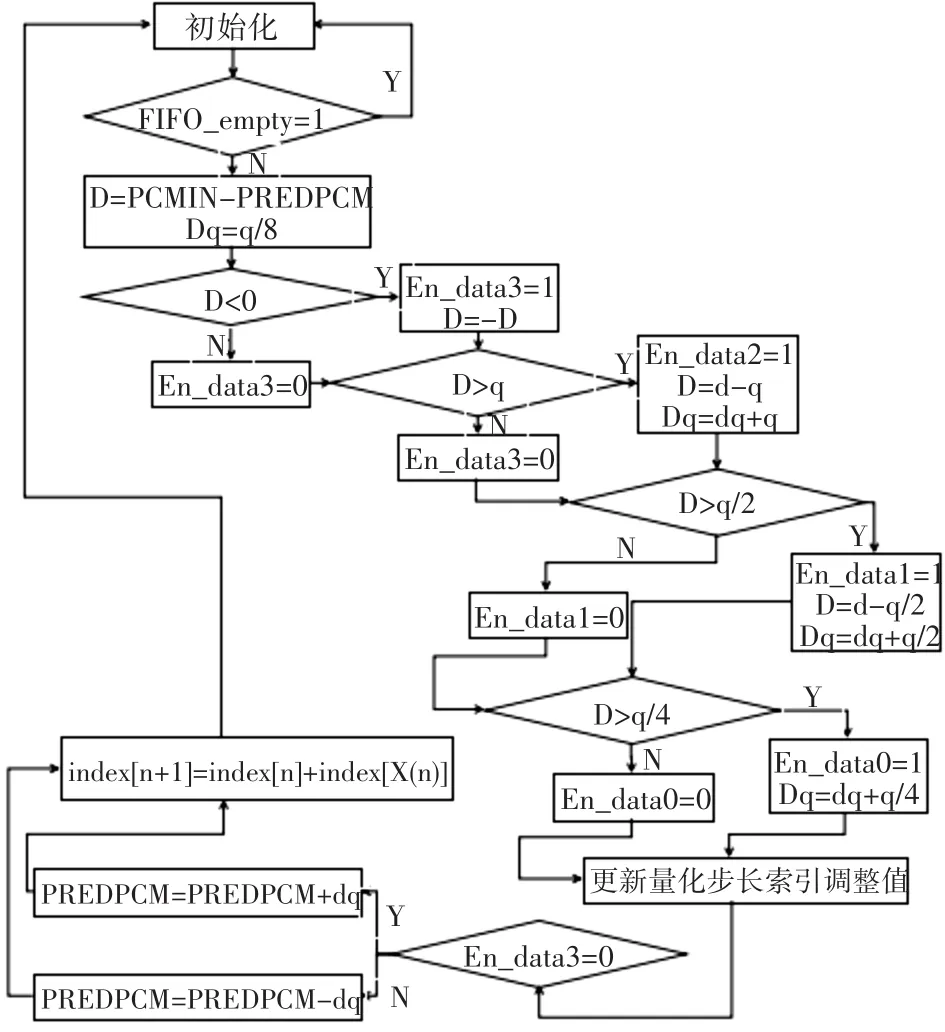

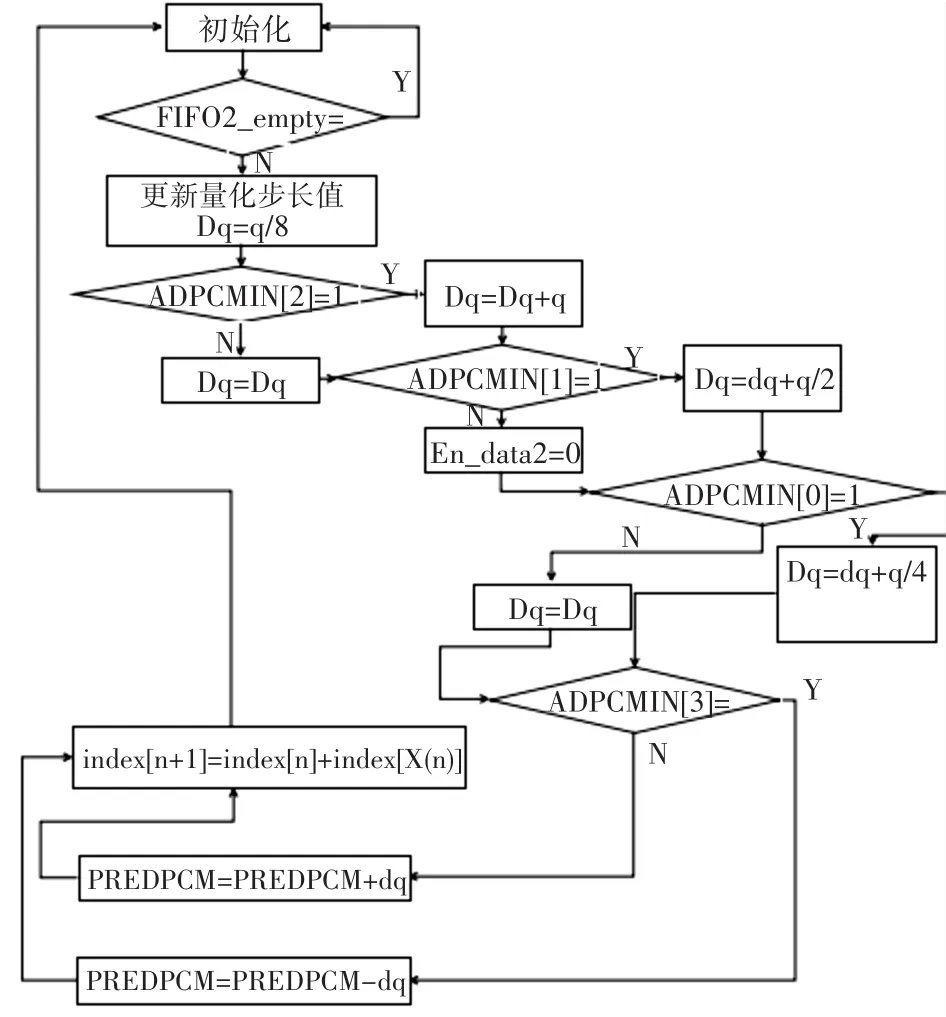

5.2 编码流程设计

在该编码流程中,需要将16bit的PCM信号转换为4bit的ADPCM语音信息,而对该模块的实现,是通过调用前面的查找表来实现的。具体流程设计则如图6所示。

图6 编码流程设计

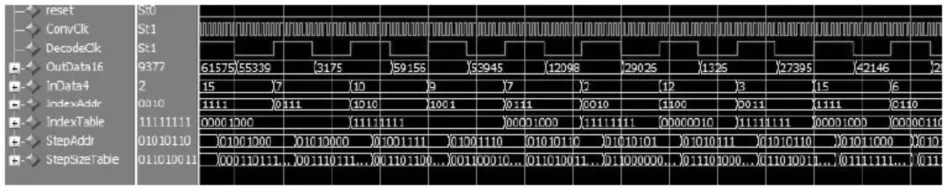

5.3 解码流程设计

解码主要是将4bit的ADPCM语音数据转换为16bit的PCM信号,并将其存入到FIFO缓存之中。

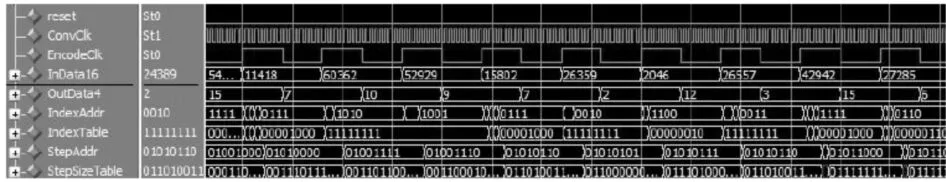

6 仿真验证

为验证上述编码和解码的正确性,采用model⁃sim对上述的流程进行验证,从而可以得到如图8和图9的结果。

图7 解码流程设计

图8 编码仿真

图9 解码仿真

通过上述的仿真可以看出,无论是编码还是解码,其产生的波形图达到了预想的功能,说明本文设计的硬件可很好地对语音信号进行预算,满足ADPCM算法对信号的处理。

7 结语

本文结合FPGA芯片和ADPCM各自的优势,实现了对语音信号的完美编码和解码,从而提高了语音信号处理的效率,也实现了一款高效和低成本的系统,为语音编码的处理提供了参考借鉴。

[1]柯俊霄.采用单片机压缩编码的数码录放系统设计[J].电子设计工程,2014,22(5):124-126.KE Junxiao.Using MCU realize speech compression cod⁃ing digital recording system design[J].International Elec⁃tronic Elements,2014,22(5):124-126.

[2]裴志兵,胡平平.基于C8051F007的ADPCM语音编码系统设计[J].信息通信,2016(1):59-61.PEI Zhibing,HU Pingping.The design of ADPCM speech coding system based on C8051F007[J].Information&Communications,2016(1):59-61.

[3]刘华.语音声码器模型及ADPCM声码器仿真[J].长春师范学院学报,2013,32(6):22-24.LIU Hua.The Model of Speech Codec and the Simulation of ADPCM's Codec[J].Journal of Changchun Teachers College,2013,32(6):22-24.

[4]程丽媛,江国栋.采用单片机压缩编码的数码录放系统设计[J].南京工业职业技术学院学报,2013,13(2):24-27.CHENG Liyuan,JIANG Guodong.Digital Recording Sys⁃tem Design of Speech Compression Coding Using MCU[J].Journal of Nanjing Institute of Industry Technology,2013,13(2):24-27.

[5]徐运武,李艳.基于单片机控制的小型程控交换系统设计[J].湖北理工学院学报,2013,29(3):8-12.XU Yunwu,LI Yan.Design of Small Exchange Experi⁃ment System Based on Single Chip Microcomputer Control[J].Journal of Huangshi Institute of Technology,2013,29(3):8-12.

[6]秦源汛,梁维谦,刘润生.低功耗高速无线传输语音采集系统的设计[J].电声技术,2012,36(1):51-54.QIN yuanxun,LIANG Weiqian,LIU Runsheng.Design on Wireless Transmission Voice Acquisition System[J].Au⁃dio Engineering,2012,36(1):51-54.

[7]张超,林孝康.基于AMBE2000和CMX7141的数字对讲机基带系统的设计[J].电声技术,2012,36(3):32-35,59.ZHANG Chao,LIN Xiaokang.Design of baseband system for digital interphone based on AMBE2000 and CMX7141[J].Audio Engineering,2012,36(3):32-35,59.

[8]王小军,赵嘎,舒平平,等.基于FPGA的IMA-ADPCM编/解码器的设计与实现[J].云南大学学报(自然科学版),2012,34(4):415-419.WANG Xiaojun,ZHAO Ga,SHU Pingping,et al.FP⁃GA-based IMA-ADPCM codec research and design[J].Journal of Yunnan University(Natural Sciences),2012,34(4):415-419.

[9]张翎影.数字对讲机中语音编码的研究与DSP实现[J].电子制作,2013(16):66.ZHANG Lingying.Voice Codec Research and DSP Imple⁃mentation in Digital Intercom[J].Practical Electronics,2013(16):66.

[10]冯金金,吴游.基于DSP的音频信号压缩通信系统的设计与实现[J].信息技术,2016,40(8):200-203.FENG Jinjin,WU You.Design and implementation of communication system of audio signal compression based on the DSP[J].Information Technology,2016,40(8):200-203.

Design of PCM Speech Coding System Based on Single Chip Microcomputer

WANG Zhongjie

(Chinese Flight Test Establishment,Xi'an 710089)

Aiming at the problem of poor performance and high cost of traditional digital signal processing in speech coding,a low power consumption and high performance speech coding system based on single chip computer is proposed.With the help of SCM technology,build the voice encoding control module with FPGA as the main chip,at the same time according to the traditional PCM in speech encoding disadvantage,ADPCM algorithm is introduced to handle voice encoding,which greatly improves the per⁃formance of speech encoding system,reducing the cost,the realization of the speech processing of low power consumption,efficient encoding.Finally,the feasibility and rationality of the above scheme design are verified by simulation and hardware testing.

FPGA chip,ADPCM optimization algorithm,speech coding,hardware design,simulation

Class Number TP391

TP391

10.3969/j.issn.1672-9722.2017.12.045

2017年6月9日,

2017年7月31日

王仲杰,男,硕士,高级工程师,研究方向:试飞测试。