高精度DDS数字IP核的设计

2017-12-26张科新

张科新,余 建

(常州信息职业技术学院电子与电气工程学院,江苏 常州 213164)

高精度DDS数字IP核的设计

张科新*,余 建

(常州信息职业技术学院电子与电气工程学院,江苏 常州 213164)

为了满足雷达系统对高精度DDS(直接数字式频率合成器)的需求,综合使用查表法、复数旋转和线性拟合3种方法,提高DDS输出信号的无杂散动态范围SFDR。当相位累加器为24bit时,使用小于1 kbyte的ROM。仿真表明所设计的DDS,输出信号的SFDR大于110 dB,等效相位截断约为2 bit。在大幅降低对ROM使用量的同时,有效降低了相位截断的bit数,同时达到了设计要求。采用TSMC 55 nm工艺进行综合后,综合结果表明运行速度高达600 MHz,满足了雷达系统对速度的需求。

直接数字式频率合成器(DDS);高精度;复数旋转;线性拟合;流水线

直接数字频率合成(DDS)为第3代频率合成技术,自发明以来得到了迅猛的发展和广泛的应用,特别是在雷达、软件无线电等系统中[1-3]。

DDS其中一个关键性能指标无杂散动态范围SFDR(Spurious Free Dynamic Range)是最受设计者关注的,所以在众多的文献中都对如何提高SFDR进行了讨论。而未从导致SFDR恶化的根本原因,相位截断角度进行考虑,多是通过在相位截断后再增加相位随机噪声、增加幅值随机噪声的角度进行[2-6],这种方法虽然可以提高SFDR,但同时也增加了输出信号的底噪水平,恶化了信噪比(SNR)。

本文通过研究,综合运用查表法、线性拟合和复数旋转3种方法,以期通过较少的ROM使用量来设计具有较高SFDR的DDS,以满足雷达系统对高精度DDS的要求。

1 DDS系统构成

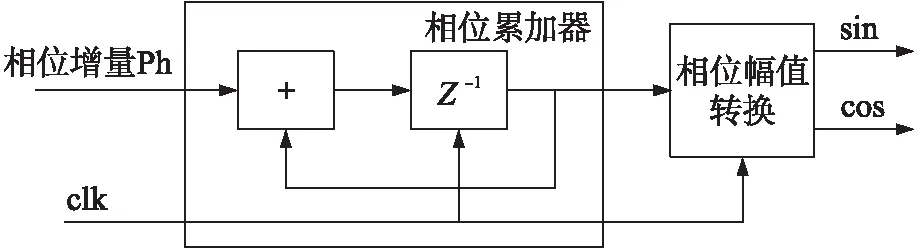

DDS数字IP核的典型结构,如图1所示[1]。

图1 DDS数字IP核典型结构图

如图1所示,DDS数字IP核主要包括相位累加器模块和相位幅值转换模块。其中相位累加器模块将输入的相位增量Ph,转换成相位信息;相位幅值转换模块则进一步地将相位信息转换成幅值信息。由文献[5-7]可知相位幅值转换模块的性能对DSS系统的性能有重大影响。

因此有大量的文献对相位幅值转换模块进行研究,目前主要集中于两种实现方法[1]:查表法和Cordic算法。

查表法如果使用相位累加器的全部输出进行查表,将导致ROM的使用量过大,如相位累加器输出为24 bit,幅值输出也为24 bit,那么需要的ROM容量将达到192 Mbyte。

如果采用CORDIC算法,由于CORDIC算法的精度和旋转的次数有关,旋转的次数越多,精度就越高,如为了达到24 bit的幅值精度,需要20次以上旋转,这使得系统在进行相位幅值转换时采用更高频的时钟或采用更深的流水线级数。更高频的时钟意味着对系统的时序提出了更高的要求,更深的流水线级数则意味着更大的延迟。

为此本文综合考虑ROM的使用量、运算的速度以及面积等多方面因素,选择使用查表法、复数旋转和线性拟合3种方法相结合的思路设计相位幅值转换模块,并充分利用三角函数对称反对称的特点进一步降低ROM的使用量。同时由于此技术没有对相位累加器的输出进行截断,所以系统的杂散较小,有效提高了系统的SFDR。

2 ROM LESS设计技术

ROM LESS设计技术是在保持DDS输出性能不下降的基础上尽量减少ROM使用量的一项关键技术[1,3]。

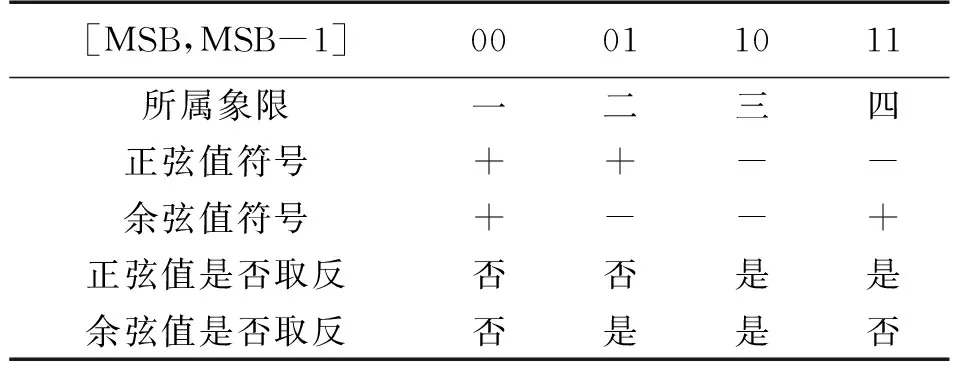

其中利用三角函数存在着的对称和反对称关系,将[0,2π)的相位转换到[0,π/2),是其中最常用的方法。对于一个N-bit的相位累加器输出,其高两位(MSB和MSB-1)便可指示该相位所属的象限,然后利用此象限内正弦和余弦的正负号,便可判断是否需要将查表得到的正弦和余弦幅值进行取反操作,如表1所示。

表1 正余弦对称性判断逻辑

通过这一步的操作,[0,2π)内的相位幅值就可由[0,π/2)内的相位幅值转换得到,即可以将ROM的使用量降低到1/4。

3 复数旋转和线性拟合技术

为了进一步降低ROM的使用量,还采用了复数旋转和线性拟合技术,这两项技术的使用不仅可以有效地降低ROM的使用量,同时还可以提高输出信号的精度,所以在下面对这两项技术进行详细介绍。

三角函数存在下面两个公式:

sin(x+y)=sinxcosy+cosxsiny

(1)

cos(x+y)=cosxcosy-sinxsiny

(2)

从式(1)、式(2)可以看出,如果要计算(x+y)的正弦、余弦值,需要知道x和y两个相位的正弦、余弦值。由此计算(x+y)的正弦、余弦幅值的方法,即被称为复数旋转法。

本文将[0,π/2)分为16份,将每一份起始相位的正弦、余弦幅值存放,进一步将[0,π/32)相位的正弦、余弦幅值进行线性拟合的方式将拟合系数存放。这样就可以快速、高精度计算得到[0,π/32)区间内任一角度的正弦、余弦值,然后再利用上面复数旋转方式,进一步计算[0,π/2)范围之内的正弦、余弦值。最后再利用三角函数对称性与反对称性原理,即可以计算得到[0,2π)内所有相位正弦、余弦值。

采用以上所示的查找表、复数旋转和线性拟合的方法,在达到相同精度的情况下,相比于查表法,仅仅以几个乘法器的代价,就可以大幅降低ROM的使用量,且可以高精度的计算出[0,2π)内所有相位的正弦、余弦幅值。

通过将VCS仿真结果和MATLAB计算结果进行对比,VCS仿真结果的最大误差为±5 bit,由此计算到的等效相位截断约为2 bit。由此表明在采用上述方法后,在达到较高精度的同时,大幅减少了ROM的使用量。

4 流水线技术

流水线技术是通用的用来提高系统运行速度的方法。为了使用流水线技术,必须识别并划分系统中串行进行且相互独立的步骤。另外增加流水级数后必然会增加芯片面积,所以还必须评估增加流水级数后是否会带来芯片面积的问题。

首先通过前面的描述可以得到相位幅值转换模块,包含下面两个关键步骤:

第1步 线性拟合计算y的正弦和余弦值;

第2步 复数旋转计算(x+y)的正弦和余弦值。

通过上面的分析可以知道上面两个步骤是相对独立的,且第1步必须在第2步之前完成,即两者是串行关系,所以完全可以采用流水线技术进行。

此时采用TSMC 55 nm工艺库进行综合后,发现其最高运行速度为125 MHz,面积约为28 579 μm2。通过分析发现,关键路径为第1步和第2步中存在的乘法-加法运算组合逻辑,为了进一步提高速度,将此乘法-加法运算的组合逻辑打断,分为乘法组合逻辑和加法组合逻辑两段,即各加入一级流水,重新使用TSMC 55 nm工艺库进行综合,综合结果显示速度已可达到600 MHz,占用面积约为42 332 μm2。此时若以125 MHz进行约束,重新综合后面积约为32 351 μm2。3次综合结果如表2所示。

从表2所示的综合结果可以发现,增加两级流水后,系统的面积是原来的1.48倍,但速度却提升到了4.8倍。若以同样的速度进行对比,则面积仅增加了13%,换取了更大的时序余量。

表2 3次综合后面积对比

5 仿真结果

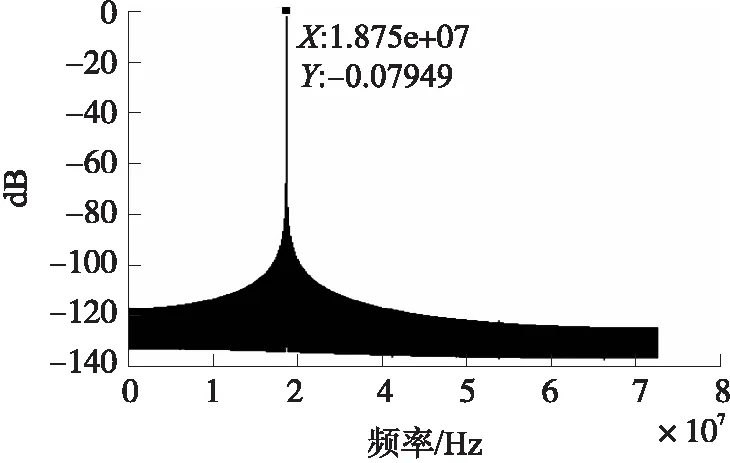

通过对上面技术进行分析,最终采用查表法、复数旋转、线性拟合相结合的方法设计了DDS的数字IP核,并进行了仿真,图2为数字IP核正交输出的时域波形图,图3为使用MATLAB对仿真得到的数据进行FFT变换得到的频域波形。

从图3可以看出,该DDS数字IP核的SFDR大于110 dB,且几乎没有杂散产生,有效提高了系统的信噪比。

图2 数字IP核输出的时域波形

图3 数字IP核的SFDR仿真

6 总结

本文通过综合运用查表法、复数旋转和线性拟合的方法设计相位幅值转换模块,大幅降低了对ROM的使用量(小于1 kbyte),有效降低了等效的相位截断bit数。仿真结果表明所设计的DDS,其输出信号的SFDR大于110 dB,达到了较高的精度。同时通过将关键路径的流水线处理,其运行时钟提高到600 MHz,满足了项目在速度方面的要求。后续若采用超前进位链加法器、乘法器单元流水线技术等可以进一步提高系统的工作速度。

[1] 张海涛. DDS杂散抑制技术研究与仿真[J]. 计算机仿真. 2011,28(2):397-401.

[2] 陈章余. 基于FPGA的DDS正弦信号发生器设计[J]. 电子技术与软件工程,2014,12:136.

[3] 潘耿峰. 一种基于DDS和倍频的频合技术[J]. 机电工程技术,2016(Z2):26-32.

[4] 张凤君,马上,汪陈浩,等. 基于RNS的低复杂度DDS的设计与实现[J]. 微电子学,2016(5):1-6.

[5] 王涛,崔少辉,刘畅,等. 基于FPGA/DDS的周期信号发生器设计[J]. 军械工程学院学报,2016(4):54-57.

[6] 张萍. 基于DDS的宽带信号发生器的设计[J]. 江南大学学报(自然科学版),2015(6):782-786.

[7] 张林行,尚小虎,赵美聪,等. 一种基于FPGA的DDS信号源实现[J]. 微型电脑应用,2015(12):16-18,4.

[8] 南楠,赵立新. DDS杂散信号分量抑制方法研究[J]. 河北北方学院学报(自然科学版),2015(6):43-47,59.

[9] 张妍,陈涛,石蕊,等. 基于DDS技术的数字移相信号发生器的设计及FPGA的实现[J]. 信息通信,2014(11):59.

[10] 毛群,王仕旭,王建国. 基于FPGA的DDS调频信号发生器设计与实现[J]. 西昌学院学报(自然科学版),2014(4):57-59.

[11] 胡杏,万书芹,陈钟鹏,等. 基于混合CORDIC算法的高速DDS设计[J]. 微电子学,2014(6):780-784.

[12] 刘平英,李红婷,梁旭东,等. 基于DDS数字直接合成技术信号发生器设计[J]. 中国科技信息,2014,24:75-76.

DesignofHighPrecisionDDSIP

ZHANGKexin*,YUJian

(Institute of Electronic and Electrical Engineering,Changzhou College of Information Technology,Changzhou Jiangsu 213164,China)

A high precision DDS(Direct Digital Synthesizer)is designed to satisfy the radar system which used loop-tap,complex multiplier,linear fitting to increase the SFDR(Spurious Free Dynamic Range). When the phase adder is 24 bit width,the used capacity of ROM is less than 1 kbyte. The simulation results show that the SFDR is greater than 110 dB,and the phase truncation is about 2 bit. So the used capacity of ROM is greatly reduced and the bit of phase truncation is also reduced,the requirement of design is achieved. After design compile using TSMC 55 nm technology,the speed can achieve 600 MHz,it also satisfies the demand of radar system.

DDS;high precision;complex multiplier;linear fitting;pipeline

10.3969/j.issn.1005-9490.2017.06.025

2016-10-31修改日期2017-01-09

TN74

A

1005-9490(2017)06-1456-03

张科新(1981-)男,汉族,江苏常州人,常州信息职业技术学院,讲师,主要从事集成电路设计、半导体物理与器件等专业方向的研究,zkxwang1006@163.com;

余建(1981-)男,汉族,重庆人,常州信息职业技术学院,讲师,主要从事集成电路设计、半导体工艺等专业方向的研究。