谐波电能计量用任意波形发生器的研究*

2017-12-18王红悦王永

王红悦,王永

(1.哈尔滨理工大学测控技术与通信工程学院,哈尔滨150080;2.大庆油田矿区服务事业部万方物业服务有限公司,黑龙江大庆163000)

0 引 言

电网中大量非线性负荷,使得电网中产生大量谐波,谐波成为电网中的一种污染源,既造成电网供电效率的降低,也给电能的准确计量造成严重影响影响电网供电的电能质量和电能计量,因此谐波环境下电能准确计量仍是值得研究的问题[1]。研究谐波电能计量对信号源就提出了新要求,即数字源应含有足够含高次谐波成分的数字元,模拟电网中的谐波环境,为谐波电能计量研究提供强有力支持[2]。

文中利用FPGA强大的硬件优势,依据国标GB/T 17215.302-2013对谐波表的的要求,以及OMIL推荐的IR 46技术要求,设计一种满足IEC 61850标准任意波形发生器,同时可满足电网中对谐波信号的要求。

1 硬件电路设计

1.1 系统的总体框图

现场可编程门阵列(FPGA)工作速度、集成度的提高以及成本的降低,使FPGA用途更加广泛。利用FPGA实现电路设计,不仅可实现特定的功能,而且编程灵活、开发周期短,有利于提高系统的整体性和可靠性[3]。

根据波形发生器性能的要求,文中选用EP4CE115F29C8的芯片,此FPGA器件以其灵活性好、便捷性强,大大提高了系统的集成度,增加了系统抗干扰性和工作的稳定性。尤其是其运行高速性,很好的解决了本系统运行速度等问题[4]。任意波形发生器系统主要由上位机、FPGA器件和TFTLCD三大部分组成(见图1)。

图1 系统设计框图Fig.1 Block diagram of system design

1.2 信号调理电路的设计

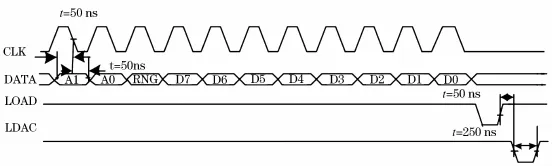

数字信号转换为模拟信号由D/A转换电路完成。主要考虑到位数和转换速度等因素,本设计选用TLC5620芯片,它是一款具有4个独立电压输出型的DAC数模转换器,每个DAC转换器都拥有一个带缓冲(高输入阻抗)的参考电压输入端口。每个DAC可以输出一倍或者两倍的参考电压与GND之间的电压值。该芯片控制信号简单,转换速度快,可使硬件设计大为简化,也减轻了系统软件设计的工作量[5]。其D/A转换电路如图2所示。根据时序图3设计驱动程序,使用仿真工具Modelsim进行功能仿真,仿真结果如图4所示。

D/A模块采用双D/A模式时,为了提高分辨率和数据速率,选用 DAC908负责提供基准电压,AD9777负责对波形数据进行数模转换,AD9777芯片是一种全新的高速、双通插值、引脚兼容的转化器,输入数据速率可以达到160 MSPS(无插值),DAC更新速率能够达到400 MSPS(8X插值),同时具有16位的高分辨率[6]。AD9777作为一种全新的转化器,能够更好的解决数据转换速率等问题。

图2 D/A转换电路Fig.2 D/A conversion circuit

图3 TLC5620数据传输时序图Fig.3 TLC5620 data transmission sequence diagram

图4 TLC5620的时序仿真图Fig.4 Timing simulation diagram of the TLC5620

2 任意波形产生原理与方法

直接数字频率合成 (Direct Digital Frequency Synthesis,DDS)[7]是近几年来快速发展起来的一种频率合成技术,它具有频率分辨率高,频率变换速度快,相位连续及可产生多种形式波形的优点,已被广泛应用于通信器材,医疗器械,教学仪器,雷达信号源等领域。DDS主要由相位累加器、波形ROM、D/A转换器和低通滤波器等4个模块构成[8]。其基本框图如图5所示。

图5 DDS的基本框图Fig.5 Basic block diagram of the DDS

由图5可知,当时钟源频率为fc时,可得输出信号f0的频率,公式如下:

式中K为频率控制字;n为相位累加器位数;fc为时钟源频率;f0为合成时钟频率。

DDS的工作流程如下:首先输入频率控制字K,将其送入相位累加器,以基准时钟fc按照K值进行累加运算[7];存储器(ROM)中已存有一个周期的波形数据,以K的累加值作为地址在ROM中进行查找相应的数据,完成了相位值到幅度值的转换;最后将生产的幅度值输送到D/A中生成模拟信号,该模拟信号经过低通滤波器的滤波就可以得到平滑的波形曲线[9]。根据奈奎斯特定律可知,理论上输出信号的频率最高小于等于fc/2。

3 基于Verilog HDL程序设计与波形发生

按现行电能表IEC标准、国家标准以及国际建议对电能表的谐波影响要求,设计一款基于FPGA的任意波形发生器,该波形发生器不仅可以输出幅频可调的正弦波形,还可输出谐波比例可调的波形信号。该波形发生器可以满足IEC 61850标准下对谐波环境的要求,使数字化电能表“溯源”方法更加有效[10]。

3.1 软件设计流程

文中软件部分在FPGA驱动接口的程序基础上进行设计,用硬件描述语言Verilog HDL完成DDS的设计,将波形数据传入D/A模块,最后将输出模拟信号显示在TFT-LCD屏幕上。软件设计主要为驱动设计和波形设计两大部分(见图6)。

图6 软件设计流程Fig.6 Software design process

3.2 波形设计

文中设计的任意波形发生器具有正弦波形输出、幅频可调、含有谐波分量的波形等工作模式,可同时显示多种不同频率和幅度的波形。

3.2.1 正弦波形

将设定好的波形数据存储到DDS的ROM中,经过系统软件的运行,可以通过示波器采集到正弦波形的实测波形,同时可在TFT-LCD液晶屏幕上显示。

3.2.2 幅频可调

在波形数据 f(t)=A sin(nωt+φ)的基础上,通过对波形数据的幅频值进行简单计算,随意调节波形的幅频值。经过优化系统软件,可以输出幅频可调的任意波形。

3.2.3 含有谐波分量的波形

任意波形发生器作为重要的仪器,在通信、检测导航等领域有着广泛应用。特别是在高压电力系统的检测领域,常常需要模拟电网谐波的标准信号源对检测设备的性能进行校验[11]。由傅里叶级数的三角函数展开式,可知周期函数f(t),在一个周期[-T/2,T/2]内由正弦及余弦函数组合而成的无穷级数,即傅里叶级数为:

式中T为周期;ω0=2π/T为基波圆频率。

将式(2)同频项合并,可得n次谐波公式:

在A0sin(ωt)的基础上加16次谐波和128次谐波,即:

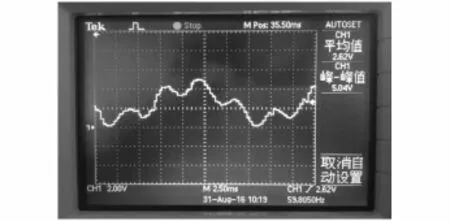

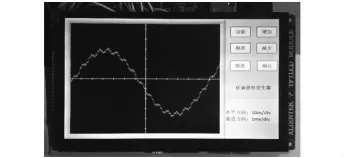

最后合成的谐波数据送入D/A转化电路后,利用示波器采集得到62.5 Hz含有谐波分量的正弦波形,如图7所示。进一步观察波形的细节,如图8所示。最终实现在TFT-LCD显示,如图9所示。

图7 合成谐波信号的整体实测波形Fig.7 Synthesis of harmonic signal measured wave as a whole

3.3 性能分析

图8 合成谐波信号的局部实测波形Fig.8 Local the measured waveform of synthesis of harmonic signal

图9 合成谐波信号的LCD显示Fig.9 LCD display of synthesis of harmonic signal

根据式(5),可计算出当N=32时,Urms=0.614;N=256时,Urms=0.643。而正弦量 f(t)=sin t的有效值:

由计算结果比较可知每个周期内的采样点数多于256个,则输出波形的准确度高于9.4%。即采样点N越大,波形越平滑且误差越小[12]

3.4 系统调试和实验结果

文中完成了系统的硬件连接和软件设计以后,通过不断优化程序代码,使系统的性能得以提高,显示状态更加稳定。由示波器采集到的波形图和TFTLCD上显示的波形图可以看出生成的波形稳定且连续,并包含丰富的彩色信息。

4 结束语

文中针对谐波电能计量所需的信号发生问题进行研究,设计一种采用 Cyclone IV、数模转换器TLC5620以及TFT-LCD实现了含谐波成分的任意波形发生器。输出的波形频率、相位、幅度、谐波比例皆可调,同时具有输出波形稳定、精度高等特点,可满足现代测试系统的要求,符合IEC 61850标准,可模拟电网中的谐波信号。