基于HEVC的CABAC硬件解码器设计

2017-12-18韩学森张德学张存生冀贞贤杜飞飞

韩学森,张德学,王 超,张存生,冀贞贤,杜飞飞

(山东科技大学 电子通信与物理学院,山东 青岛 266590)

基于HEVC的CABAC硬件解码器设计

韩学森,张德学,王 超,张存生,冀贞贤,杜飞飞

(山东科技大学 电子通信与物理学院,山东 青岛 266590)

首先分析了高效视频编码(High Efficiency Video Coding,HEVC)编码标准,对HEVC的新特性进行总结,并给出HEVC解码器整体架构。其次提出基于熵解码部分优化的硬件解码器架构,并进行仿真验证。最终通过与HM12.0软件评测结果的对比,证明所设计的上下文自适应二进制算数编码(Context Adaptive Binary Arithmatic Coding,CABAC)硬件解码器性能能够满足解码要求。

HEVC;HM12.0;CABAC;硬件解码器

0 引言

近年来,随着数字化信息的迅猛发展,视频信号对人们的生活影响逐渐增大,人们对视频质量的要求也越来越高,目前,1 080 P分辨率的视频已经非常普及,4K甚至8K超高分辨率视频也在逐渐推广开来。这对视频信号传输造成了巨大压力,对视频信号进行高效压缩是解决这个问题的有效方案。为实现这个目标,国际电信联盟和国际标准组织各自编订了一系列编码标准。截至目前,研究最热门、应用前景最广泛的视频编码标准为高效视频编码(High Efficiency Video Coding,HEVC)[1]。

本设计在对HEVC标准进行全面剖析的基础上,分析了HEVC标准的新的关键特性,并给出HEVC解码器总体架构。然后设计针对熵解码部分进行优化的硬件解码器并仿真,最终通过与官方参考软件HM12.0解码效果相比较,证实了所设计的硬件解码器性能符合要求[2]。

1 HEVC简介

1.1 HEVC标准

2010年4月,在德国德累斯顿召开了视频编码联合协作小组(Joint Collaborative Team on Video Coding,JCT-VC)第一次会议,确定了新一代视频编码标准名称为HEVC,并且建立了标准测试模型HM[3]。2013年1月,HEVC正式成为国际标准。HEVC编码标准的核心是以上一代视频编码标准H.264/AVC为基础,可对高分辨率、高保真的视频压缩效率提高一倍,即在保持相同视频图像质量的条件下,视频流的码率降低50%,但计算复杂度会提升2~4倍[4]。

1.2 HEVC新特性

与上一代编码标准H.264相比,HEVC的新特性体现在许多方面,最主要的技术特点如下:

(1)更大尺寸的编码结构:采取超大尺寸四叉树编码结构,编码单元最大可达64×64,且可以根据实际需求进一步划分;

(2)更灵活的块结构:采用自适应变换(Residual Quad-tree Transform,RQT),根据输入信号自动选择变换块大小;

(3)并行化设计:采用基于slice的并行处理方式、基于tile的并行处理方式以及波前并行处理(Wavefront Parallel Processing,WPP)多种并行处理方式,更好地满足高分辨率视频解码的实时性需求[5]。

1.3 HEVC解码器

图1给出HEVC解码器总体架构图。

2 HM12.0评测

2.1 评测环境及所用序列

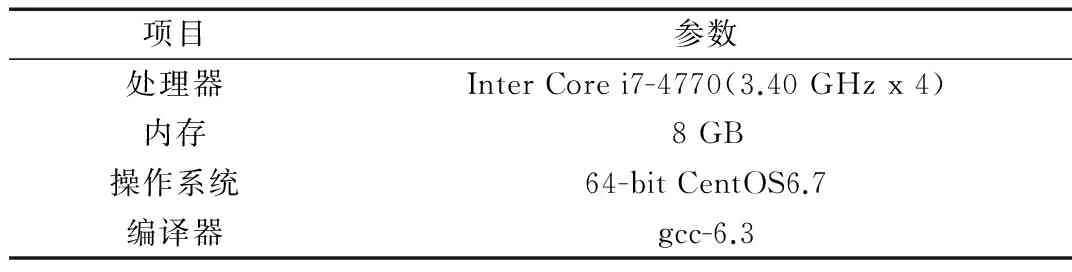

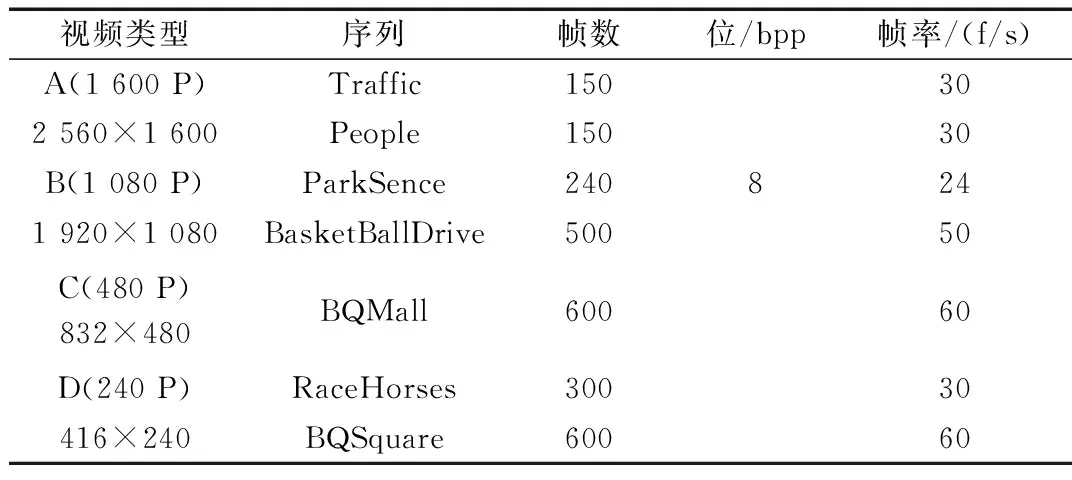

本设计使用HM12.0参考软件对HEVC标准中的解码器部分进行复杂度评测。评测环境如表1所示。序列信息如表2所示。

表1 评测环境

表2 序列信息

2.2 不同量化参数下解码时间比例变化

解码过程中量化参数对解码也会有很大影响,图2给出了在不同量化参数配置下,部分模块解码时间占整体解码时间的百分比及变化趋势。

图2 不同量化参数下各模块解码时间比例变化

观察图2可以得出,随着量化参数的增加,熵解码模块解码时间占总体时间的比例逐渐减小,但是其他模块如反变换反量化IQT、帧间预测编码、去块滤波DF等所占的时间比例将有所增加。

3 CABAC硬件解码器设计与验证

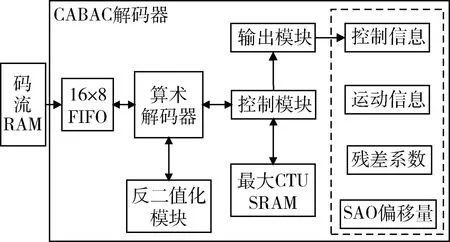

3.1 CABAC硬件解码器架构

图3给出了CABAC硬件解码器的总体架构。输入的比特流在缓存中位移,随后算术解码器对二进制值进行解码,同时对相关模型进行更新,控制模块则是控制着整个解码流程有序进行,最终解码完成结果由输出模块进行输出[6]。

图3 CABAC硬件解码器架构

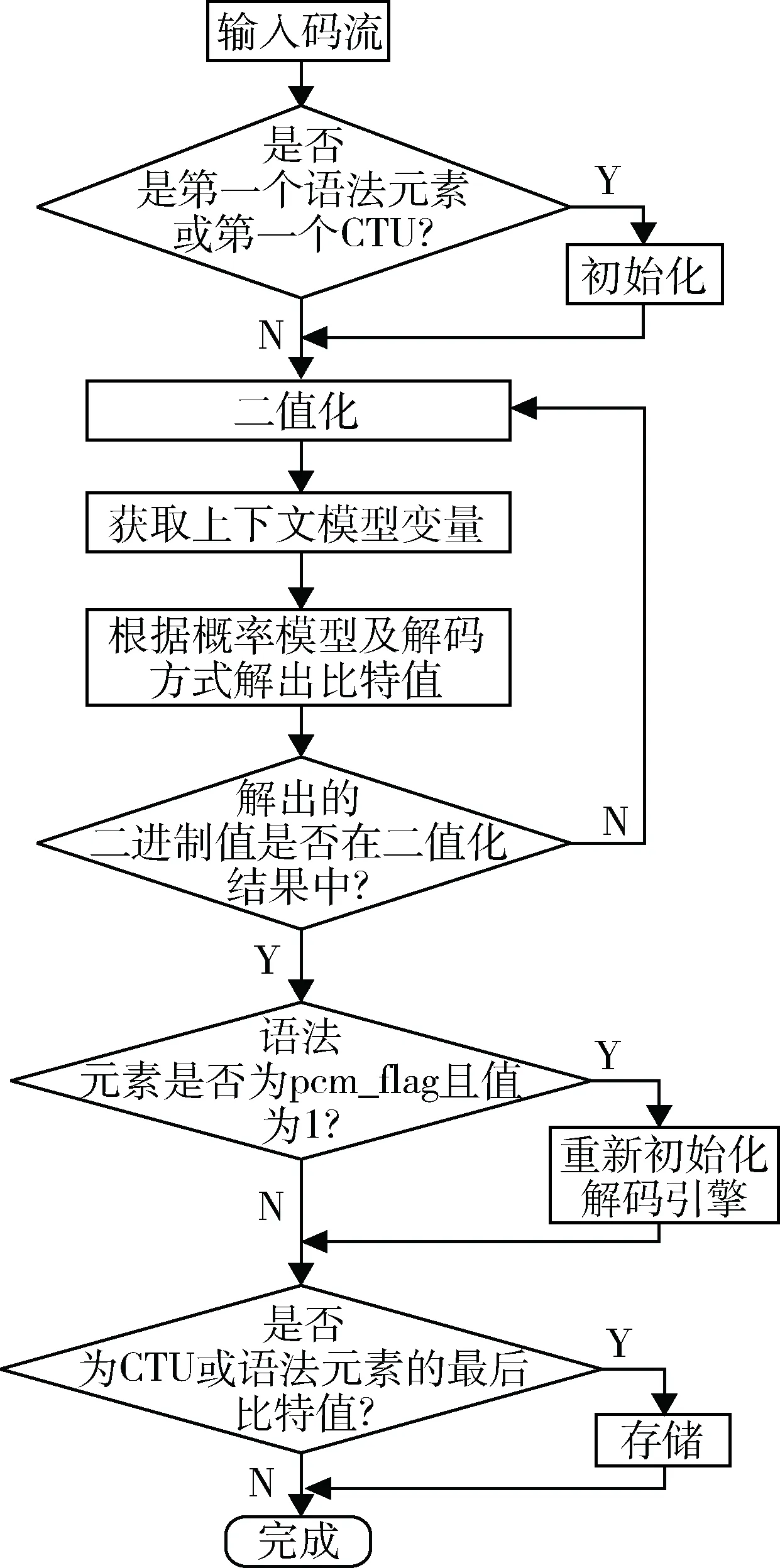

图4给出CABAC硬件解码器具体解码过程。

图4 CABAC硬件解码流程图

3.2 性能验证

本设计使用BasketballDrive(1 920×1 080,500帧) 作为测试序列对CABAC硬件解码器进行仿真测试。

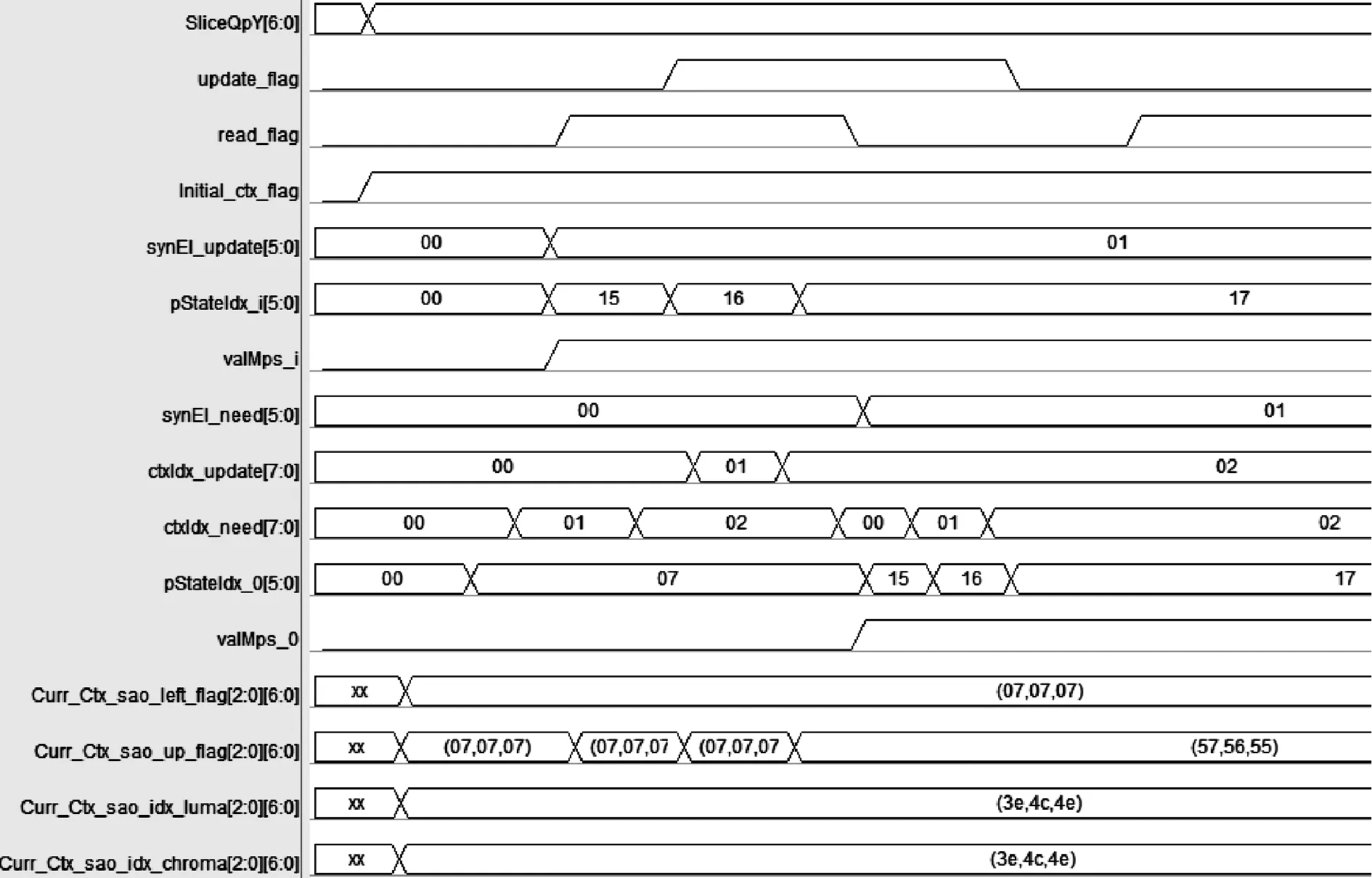

图5给出CABAC硬件解码器控制模块的仿真效果。观察波形可以发现,控制模块很好地完成了数据的读取和模型变量的更新,即解码器仿真结果与HM12.0评测结果相一致,解码性能符合要求。

4 结论

本设计首先介绍了HEVC标准发展历程及关键特性,然后在对HEVC官方参考软件HM12.0解码部分进行评

图5 控制模块仿真结果

测的基础上,设计针对熵解码部分的CABAC硬件解码器并进行仿真验证。最终与HM12.0评测结果进行对比,证实所设计的硬件解码器解码性能满足要求。

[1] 汪八零.基于H.264/AVC去块滤波器的研究及VLSI设计[D].哈尔滨:哈尔滨工业大学,2006.

[2] 石阳.H.264的实时熵解码器设计[D].哈尔滨:哈尔滨工业大学,2011.

[3] 彭金虎,岑峰. HEVC帧间运动归并技术的研究[J].微型机与应用,2013,32(1):40-41,44.

[4] 柳素华. HEVC视频编码关键技术研究与实现[D].厦门:厦门大学,2011.

[5] 徐宝凤.基于H_265的软件解码平台设计与实现[D].西安:西安电子科技大学,2013.

[6] 汪建军.HEVC视频编解码标准研究及解析模块设计[D].济南:山东大学,2014.

Design of CABAC hardware decoder based on HEVC

Han Xuesen, Zhang Dexue, Wang Chao, Zhang Cunsheng, Ji Zhenxian, Du Feifei

(College of Electronics, Communication and Physics, Shandong University of Science and Technology, Qingdao 266590, China)

In this paper, we analyzed the HEVC (High Efficiency Video Coding) coding standard firstly, summarized the new features of HEVC, and gave the overall architecture of HEVC decoder. Then put forward the design of hardware decoder aiming at entropy decoding part and carried out simulation. Finally, it was proved by the result comparison with HM12.0 that the performance of CABAC (Context Adaptive Binary Arithmatic Coding) hardware decoder can meet the decoding requirements.

HEVC; HM12.0; CABAC; hardware decoder

TN492

A

10.19358/j.issn.1674- 7720.2017.23.010

韩学森,张德学,王超,等.基于HEVC的CABAC硬件解码器设计[J].微型机与应用,2017,36(23):35-36,40.

2017-06-13)

韩学森(1992-),男,硕士研究生,主要研究方向:专用集成电路设计。

张德学(1977-),男,副教授,硕士生导师,主要研究方向:异构多核片上网络NoC建模与评估、SoC集成电路设计。

王超(1989-),男,硕士研究生,主要研究方向:专用集成电路设计。