基于PCIe2.0的Camera Link接口相机模拟系统设计

2017-12-15,,,

,,,

(1. 哈尔滨工业大学(威海) 信息与电气工程学院,山东 威海 264209;2. 威海广播电视台,山东 威海 264200)

基于PCIe2.0的Camera Link接口相机模拟系统设计

兰功盾1,赵占锋1,魏高峰2,周志权1

(1.哈尔滨工业大学(威海)信息与电气工程学院,山东威海264209;2.威海广播电视台,山东威海264200)

目前,为了进行空间科学实验,多种卫星搭载航天CCD相机以便获取图像数据;而在地面对星载图像处理系统的工业检测需要大的分辨率及更高灵敏度的CCD工业相机;Camera Link格式的视频信号接口具有传输速率快、电子噪声干扰小等优点,广泛的应用于航天CCD相机中;由于CCD工业相机的价格高昂、输出不够灵活等限制原因,需要设计一款基于PCIe2.0的Camera Link接口相机模拟系统,代替航天CCD相机,作为星载图像处理系统检的检测时的信号源;该相机模拟系统以FPGA为核心,由DDR3存储器、Camera Link驱动芯片、PCIe接口等组成,实现输出分辨率高达8 000×6 000的多种分辨率的图像数据,可以灵活的输出测试所需的特定图像,为星载图像处理系统检的检测提供稳定灵活的图像数据,以满足对星载图像处理系统检测测试的需求。

Camera Link接口;PCIe2.0;航天CCD相机;FPGA

0 引言

随着我国空间技术的发展,进行了大量的空间科学实验,其中图像数据是空间科学实验的一个重要部分。目前技术成熟、应用广泛的CCD图像传感器则是获得图像数据的主要手段[1]。在空间科学实验中,需要对CCD图像传感器得到的图像进行图像采集、处理。而为了对星载图像采集处理系统进行测试评估,需要CCD图像传感器对星载图像采集处理系统输出特定的图像,以便进行功能的检测及图像处理能力的测试。随着星载图像采集处理系统的不断发展,对星载图像采集处理系统的检测则要求的图像内容越来越丰富灵活,数据量越来越大[2]。但是,CCD图像传感器的价格昂贵,在测试的过程中易损坏,造成高昂的成本,且难以做到灵活的输出某些特定的图像数据,实现不同分辨率及帧频的图像输出。因此,在对图像处理器的测试过程中,设计一款相机模拟系统来代替CCD图像传感器则变得尤为重要。

目前市面上的相机模拟系统较为常见,且种类繁多功能强大各具优势,但是普遍使用标准格式的视频信号接口,在高分辨率,大数据量的图像数据输出时,此类接口的视频信号发生器则在传输速度上无法满足。在高分辨率,大数据量的图像数据输出时,此类接口的视频信号发生器则在传输速度上无法满足实际的需求。非标准格式的视频信号接口Camera Link 技术有很多的优点, 算是目前图像传输速率最快的一种接口,同时,它使用低压摆幅差分电流模式驱动,降低了电子噪声干扰,因此在航天上有很广泛的应用。因此,本文设计了一款基于PCIE - Camera Link的相机模拟系统可以弥补上述的不足,在实际的工程应用中就要重要的意义。

本文设计一款基于PCIe2.0的Camera Link接口相机模拟系统,代替CCD图像传感器,实现向图像处理系统输出大数据量的图像数据,完成对图像处理系统的检测测试,可以灵活的输出测试所需的特定图像,实现不同分辨率以及帧频的图像输出,并且可以减小CCD图像传感器易损坏的高成本的风险,具有广阔的应用前景。

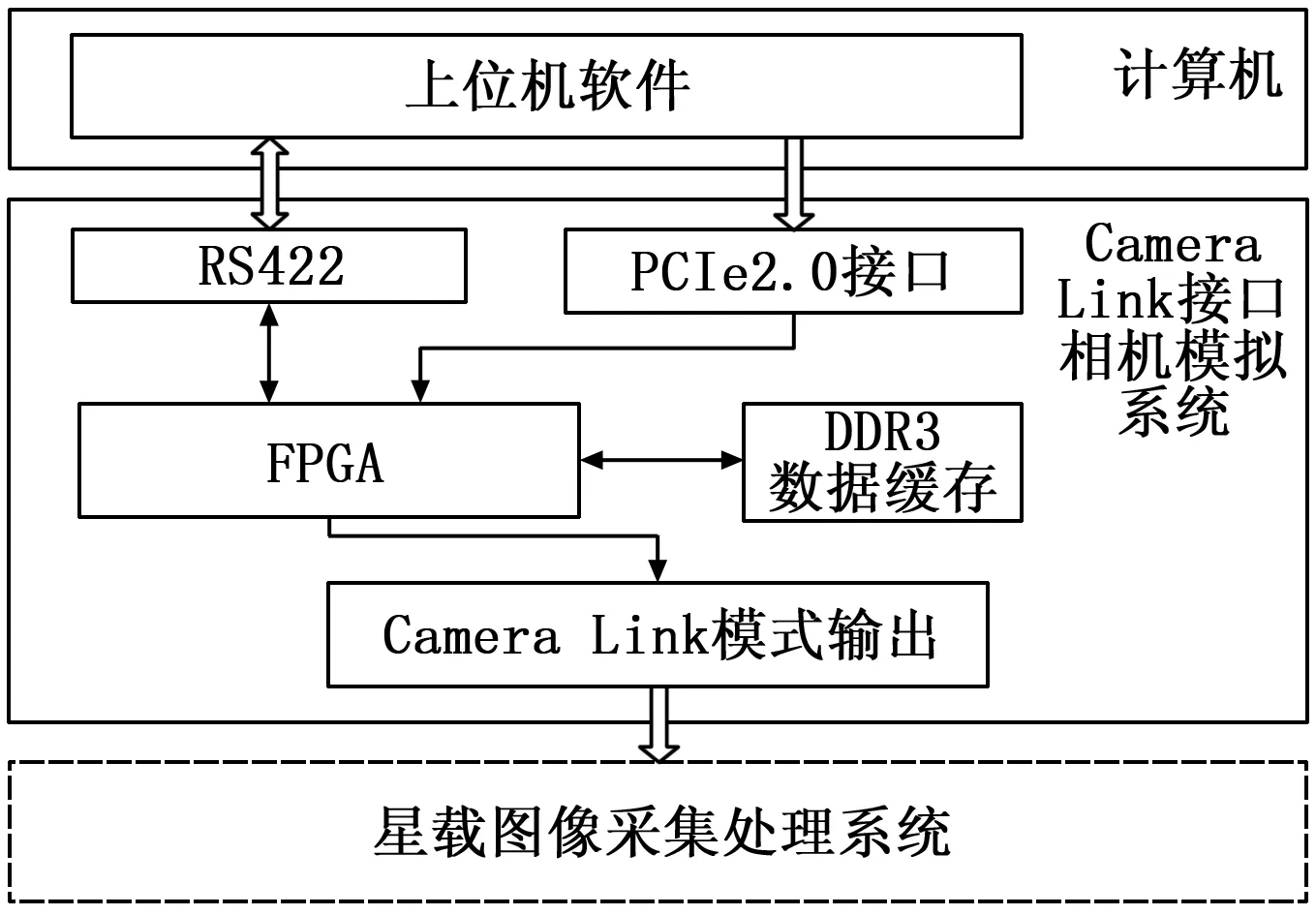

1 硬件总体设计

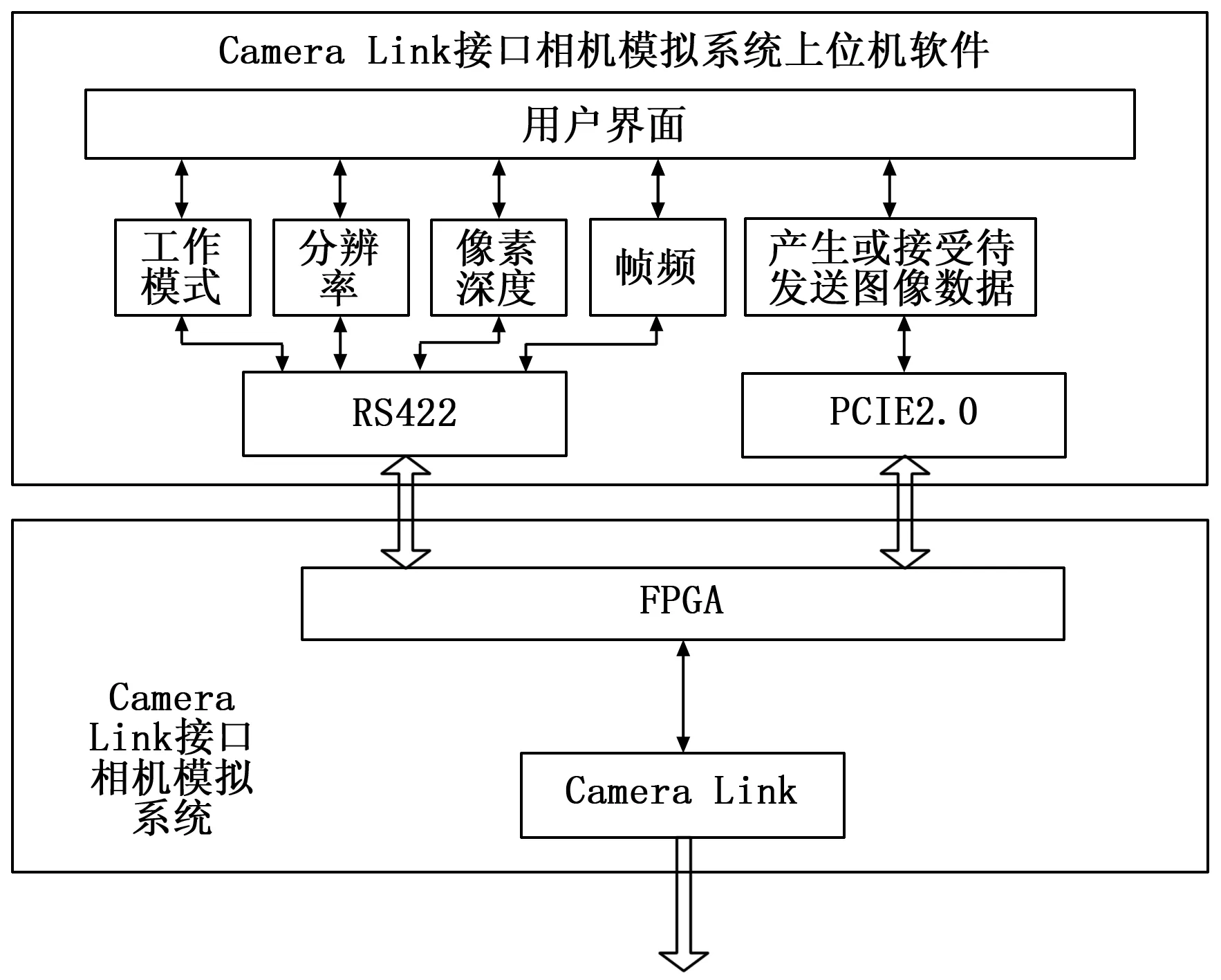

本文设计一款基于PCIe2.0的Camera Link接口相机模拟系统,实现上位机通过PCIE2.0,将产生或接收的标准视频图像数据下传给模拟系统,模拟源系统将图像数据以 Camera Link标准的低压查分信号(LVDS)输出,以达到模拟Camera Link接口工业相机的目的。上位机通过RS422与模拟系统进行通信,对其发送起始指令以及控制模拟系统实现Base、Medium、Full三种不同的模式配置,以及不同分辨率及帧频的视频图像信号输出,同时,信号模拟系统也通过RS422向上位机反馈其工作模式及状态。该相机模拟系统由FPGA、DDR3存储器、Camera Link驱动芯片组成。FPGA是整个系统的核心,所有的接口都是由它控制的,完成整个系统不同工作模式的配置与数据高速存储、传输。系统基本框图如图1所示。

图1 相机模拟系统基本框图

课题设计的模拟源系统需要满足以下的功能需求:

(1)用户可以通过PCIe接口向模拟源系统灵活的导入图像,以实现输出所需的特定图像;

(2)模拟源系统可是保证高分辨图像输出的实时性;

(3)模拟源系统可以实现高分辨的的图像数据输出,最高分辨率可达到8000×6000,帧频为12.5 Hz;

(4)模拟源系统可以实现Base、Medium、Full三种不同配置模式的Camera Link格式输出。

1.1 Camera Link接口模块

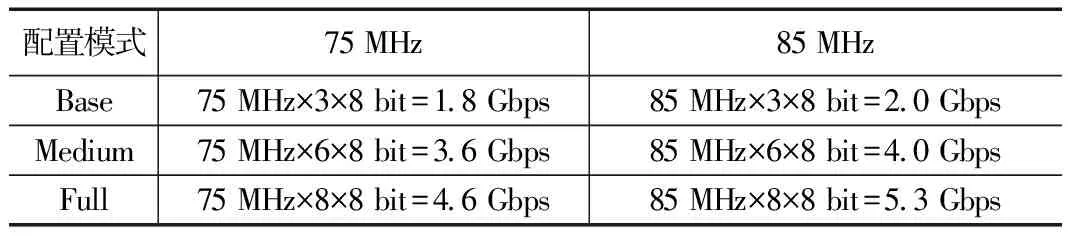

本次设计的相机模拟系统采用Camera Link驱动芯片以实现Camera Link格式的图像数据输出。并且,针对相机模拟系统的功能需求,在对星载图像采集处理单元进行地面检测时,相机模拟系统需要可以实现Base、Medium、Full三种不同配置模式的Camera Link格式的视频信号输出。其中,每个Camera Link驱动芯片中包含3个端口。Camera Link格式图像输出时,采用标准的MDR26连接器。3种不同Camera Link配置模式所需要的驱动芯片个数及连接器个数如表1所示。

表1 3种配置模式的端口分配

Camera link 是一个工业高速串行数据的连接协议, Camera Link 收发转换芯片是由 National Semiconductor 公司制造的 28 位 Camera Link 芯片组来完成。目前,用于 Camera Link 模式图像输出的主流驱动芯片始终速度有75 MHz和85 MHz,则两种驱动芯片不同模式下的输出速率如表2所示。

表2 不同时钟速度的输出速率

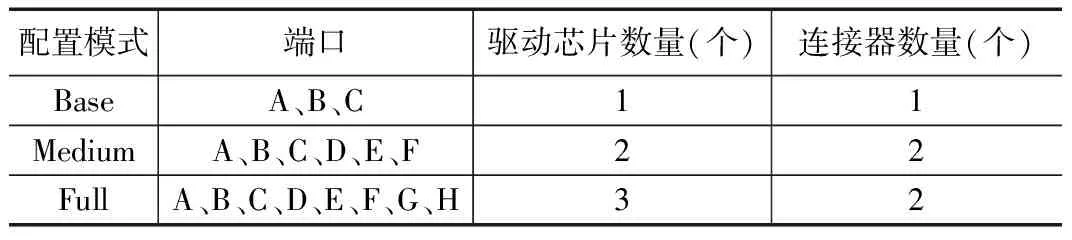

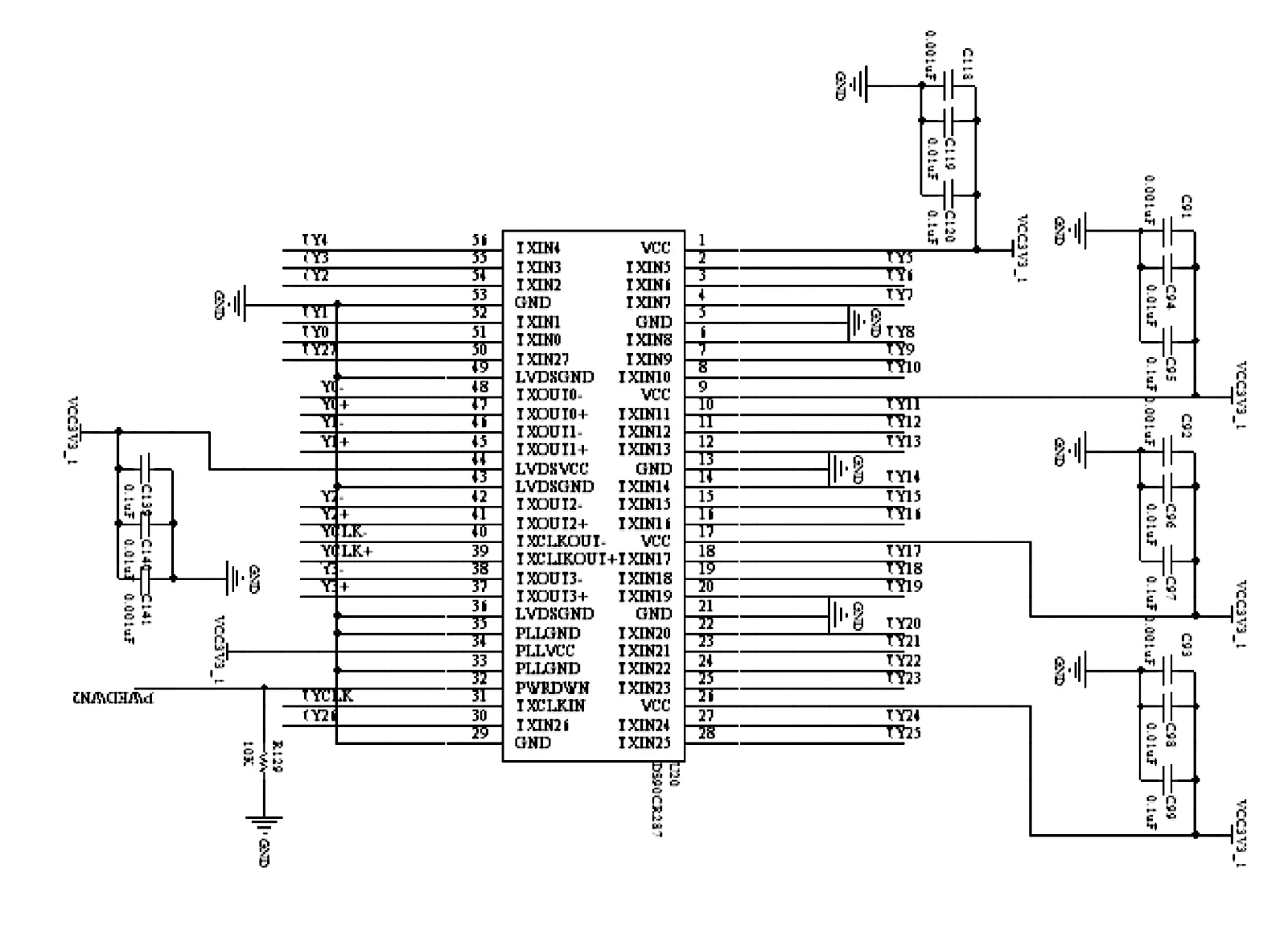

视频图像信号模拟源系统的功能需求中提出,实现最大分辨率达到8 000×6 000,帧频为12.5 Hz的Camera Link格式图像数据输出。此时Camera Link 接口图像数据输出速率达到4 800 Mbps,因此需要采用85 MHz的Camera Link 驱动芯片,并以Full 模式工作。综上所述,Camera Link视频信号输出板将采用三片85 MHz的Camera Link 驱动芯片DS90CR287以及两个MDR26连接器实现Camera Link格式图像数据输出,以满足模拟源系统的功能需求。

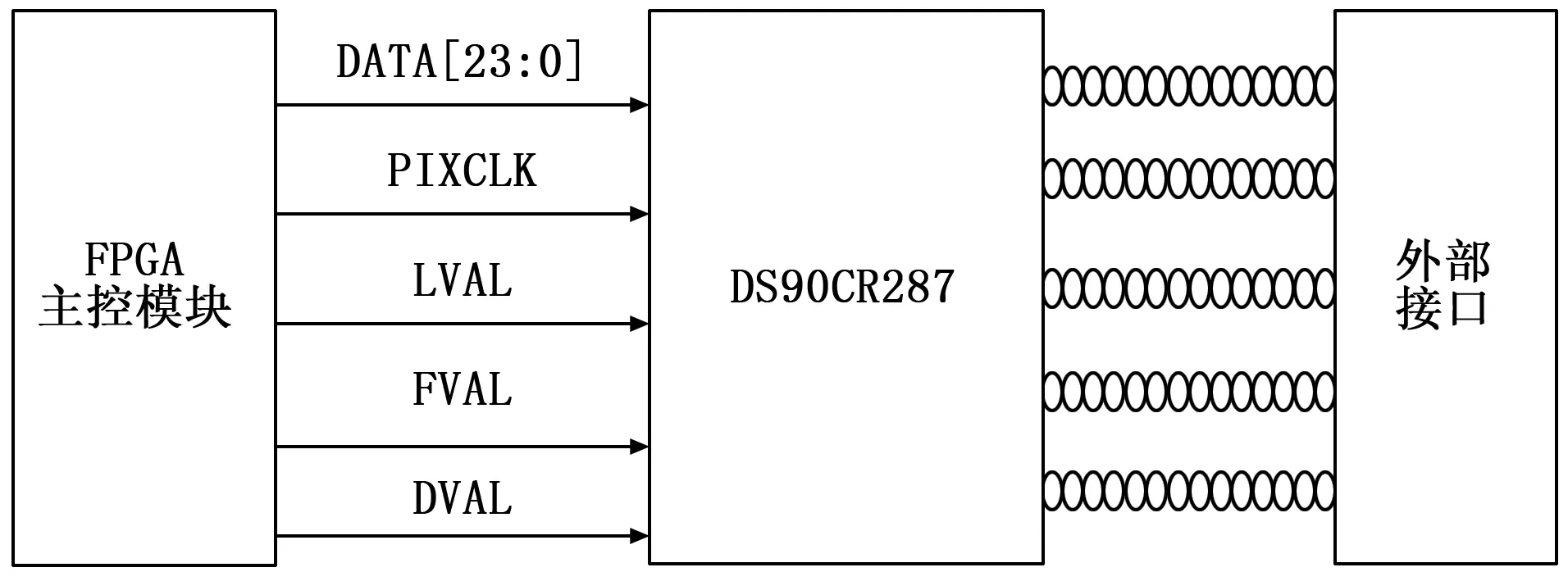

DS90CR287芯片的电路如图2所示。

图2 DS90CR287芯片电路

Camera Link接口标准的数字相机中,分别有一个相机到采集设备和采集设备到相机的串行通信信号:SerTFG和SerTC,以及4组低压差分的相机控制信号CCl-CC4。因此,在本课题设计的相机系统中也加入这几个信号。为了保证较远距离通信情况下系统得可靠性,这两个信号也是采用LVDS技术进行传输。因此同样需要串/并转化和电平转换。本文将分别采用DS90LV019芯片及DS90LV032ATM作为相机模拟系统和FPGA之间的转换芯片。其电路图分别如图3及4所示。

图3 DS90LV019芯片电路

图4 DS90LV032ATM芯片电路

1.2 FPGA主控模块

Xilinx公司的Kintex-7 系列是一种新型 FPGA,能以不到 Virtex-6 系列一半的价格实现与其相当性能,性价比提高了一倍,功耗降低了一半,具备支持PCIE2.0、DDR3 SDRAM 以及多全局时钟和丰富的布线资源等特点,能较好满足模拟器设计过程中对资源的需求。因此,本次设计选用Xilinx公司的Kintex-7 系列的XC7K325T,该FPGA支持具有PCIE硬核,支持PCIE 2.0,最高可达×8个通道。图5为Camera Link接口芯片与FPGA的连接示意图。

图5 FPGA与协议芯片的连接示意图

1.3 PCIe接口模块

本设计中,相机模拟系统采用通过PCIe2.0接口的方式,接收上位机高速下传的图像数据。理论上,采用PCIe2.0接口×4通道,有效传输速率可达16Gbps。本次设计中,相机模拟系统实际工作中PCIe2.0×4接口接收上位机下传数据时的传输速率可以达到接近11Gbps,要远大于Camera Link接口full模式工作时的最大传输速率。因此本设计中,采用的PCIe2.0×4接口来接收图像数据,可以满足Camera Link接口实时输出的速率要求。

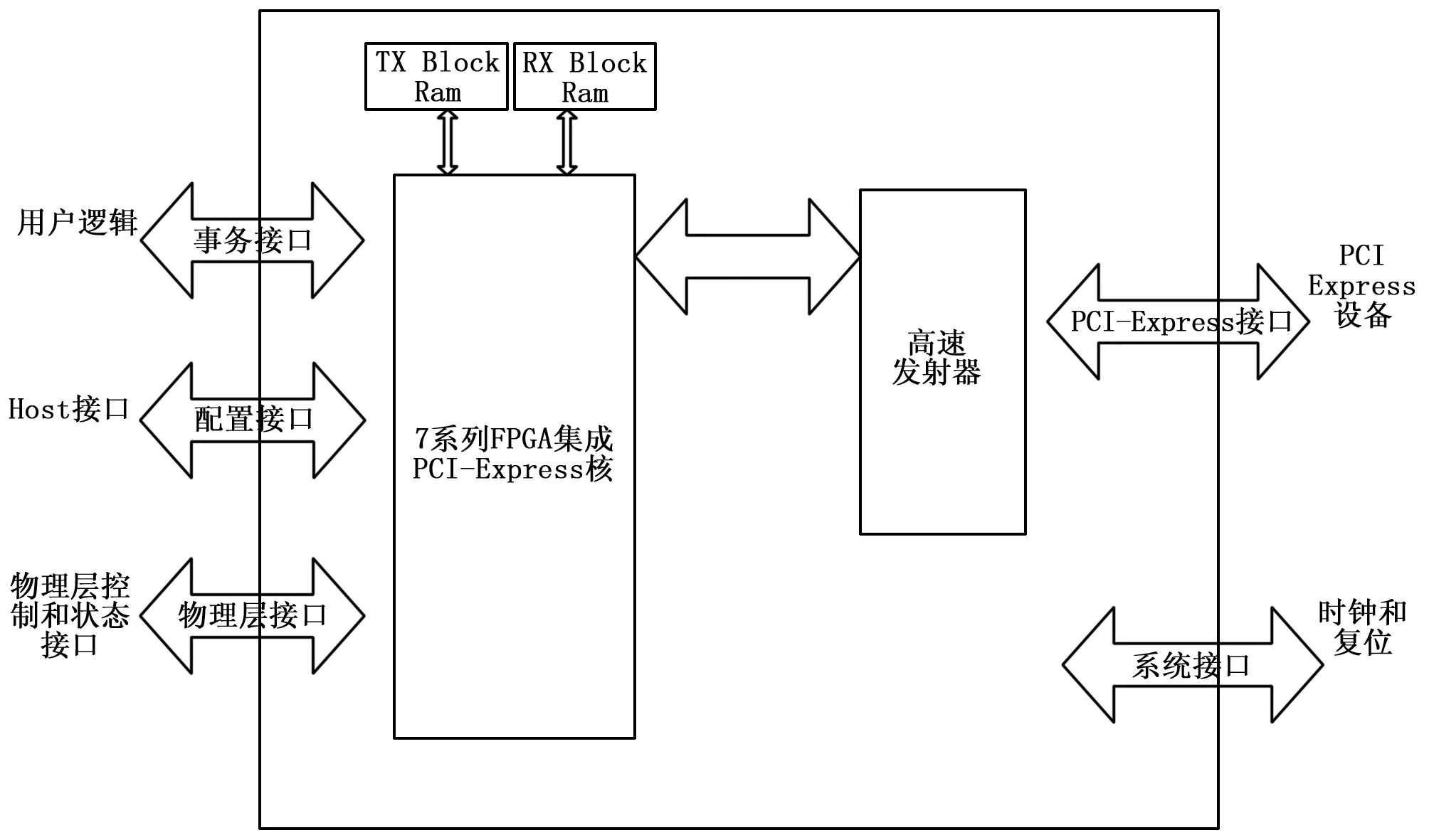

PCIE协议由事务层、数据链路层和物理层组成。它的结构图如图6所示。其中事务层具有完整的协议,处理不同的命令和事务层的处理需求;数据链路层负责连接事务层和物理层,起到一个桥梁的作用,解析事务层下发的数据包并将结构传给物理层。接收物理层的数据,打包传给事务层;物理层传输逻辑控制数据从电气接口上完成数据传输。

图6 PCIE协议结构

在本次设计中,使用Xilinx公司Kintex7系列FPGA提供的PCI-Express的IP核完成PCIE2.0接口的数据下传功能。

PCIE核集成了PCIE的事务层、数据链路层、物理层和配置管理层。相当于将PCIE桥接芯片集成到FPGA中,用户只需要在开发FPGA程序时,调出PCIE硬核,做简单的设置,在事务层上提交事务层TLP包的接收和发送,就能完成PCIE功能。硬核的结构图如图7所示。

图7 Kintex7中核接口结构图

针对课题设计的相机模拟系统的功能需求,PCIe接口需要高速的接收下传的图像数据,传输速率需高于5.3Gbps。因此,在PCIe数据下传单元中采取PCIe DMA的方式进行数据接收,采用DMA 方式的优点是可以不需要CPU的干预,可以极大的发挥PCIe的数据传输速率。

1.4 SDRAM存储器模块

相机模拟系统工作时,需要通过PCIe接口接收上位机下传的大量图像数据,同时以Camera Link格式输出图像数据,由于PCIe接口与Camera Link接口的传输速率不同,则会出现不同时钟域的数据传输问题。此外,Windows不是实时操作系统,在下传图像数据时,无法对模拟源系统的发出的中断请求做及时的处理。为了解决这两个问题,设计中在相机模拟系统中设计了一个数据缓存单元。模拟源系统的功能需求中指出,需要完成高分辨的视频图像信号输出,因此数据缓存单元将会对大量的图像数据进行缓存处理,仅使用FPGA的片上资源难以满足需求,所以课题中采用FIFO加DDR3两级缓存的方式对下传至模拟源系统的大量图像数据进行缓存组织。

设计中在相机模拟系统中设计一个缓冲区作为DDR3数据缓存单元,该缓存单元由两片镁光公司生产的MT41J256M16HA-107型号DDR3存储芯片组成。每片DDR3存储芯片具有15位地址线以及16位数据线,容量达到512 MB。由于模拟源系统内部的数据传输多为32 bit,若采用16 bit数据总线的DDR3存储芯片,则在FPGA软件设计中将会出现数据位拆分及合并问题,增加了FPGA软件设计的难度。因此DDR3数据缓存单元的硬件设计中,采用两片DDR3存储芯片作为一个缓冲区,共用15位地址线,数据线扩展为32位,容量扩展至1 GB。

MT41J256M16HA-107型号DDR3存储芯片采用了ODT技术,所以设计中芯片的DQ、DS、DM信号不需要串入终端电阻,其余的A[14:0]、BA[2:0]、RAS#、CAS#、WE#、CS#信号均需要串接一个22欧姆的终端电阻上拉到0.75 V的参考电压上。0.75 V的参考电源的电源芯片采用TI公司的LDO芯片TPS51200DRCT,该芯片较为广泛的应用于DDR3的供电模块中。

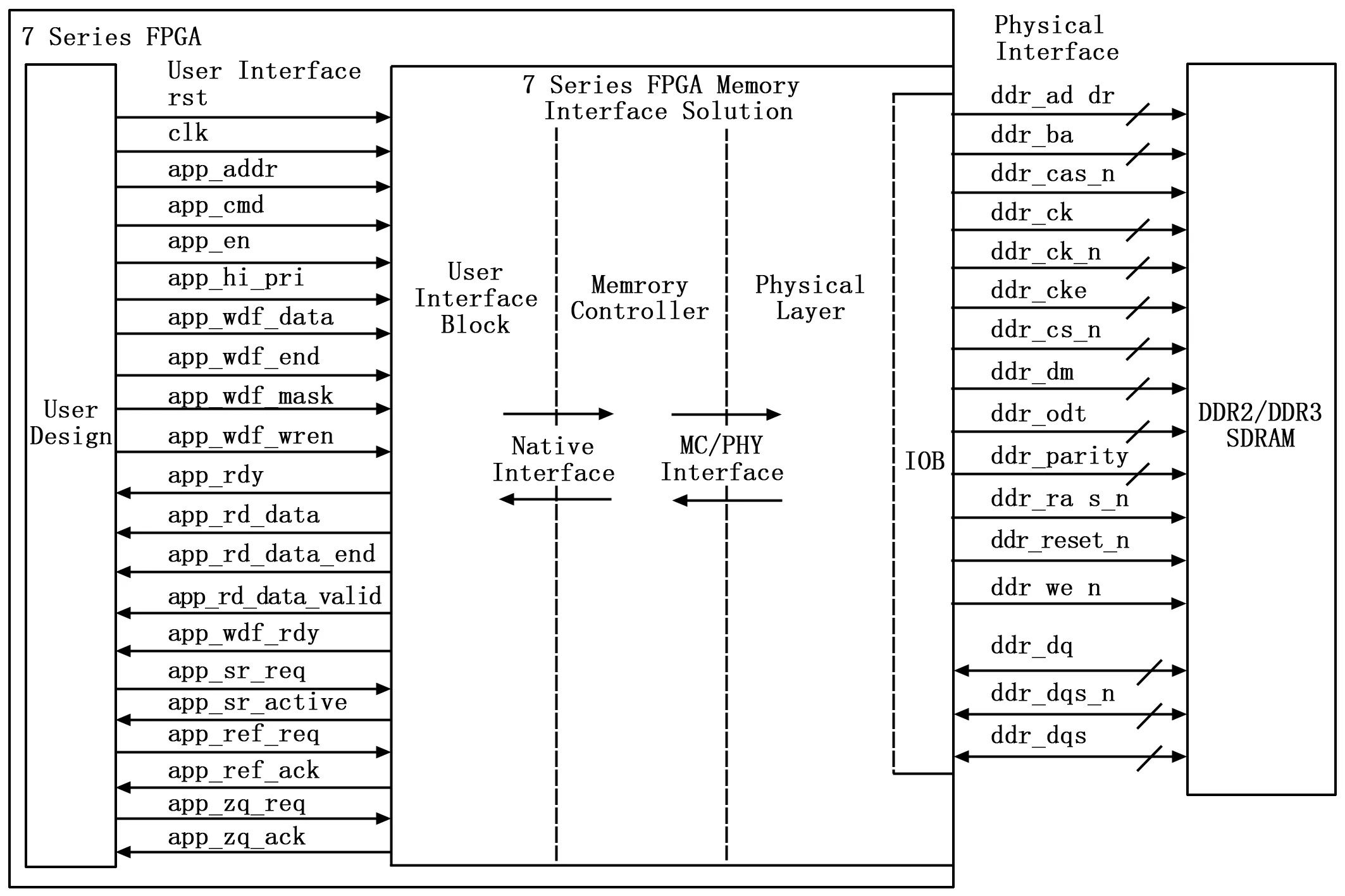

设计中,在对DDR3进行数据读写操作时,需要使用Kintex7系列FPGA中集成的存储器接口生成器(MIG),以便设计DDR3的接口控制器。因此DDR3数据缓存单元的两片DDR3存储芯片需要接到FPGA中特别的BANK中。在对DDR3 SDRAM数据缓存模块的软件程序编写中,由于采用了Xilinx ISE工具CORE Generator里的存储器接口产生器MIG(Memory Interface Generator),用户只需在FPGA器件中通过用户接口(User Interface)提供相应的时序,就可以对DDR3进行读写操作。 DDR3 SDRAM存储器接口的解决方案逻辑框图如图8所示。

图8 K7 FPGA存储器接口的解决方案逻辑框图

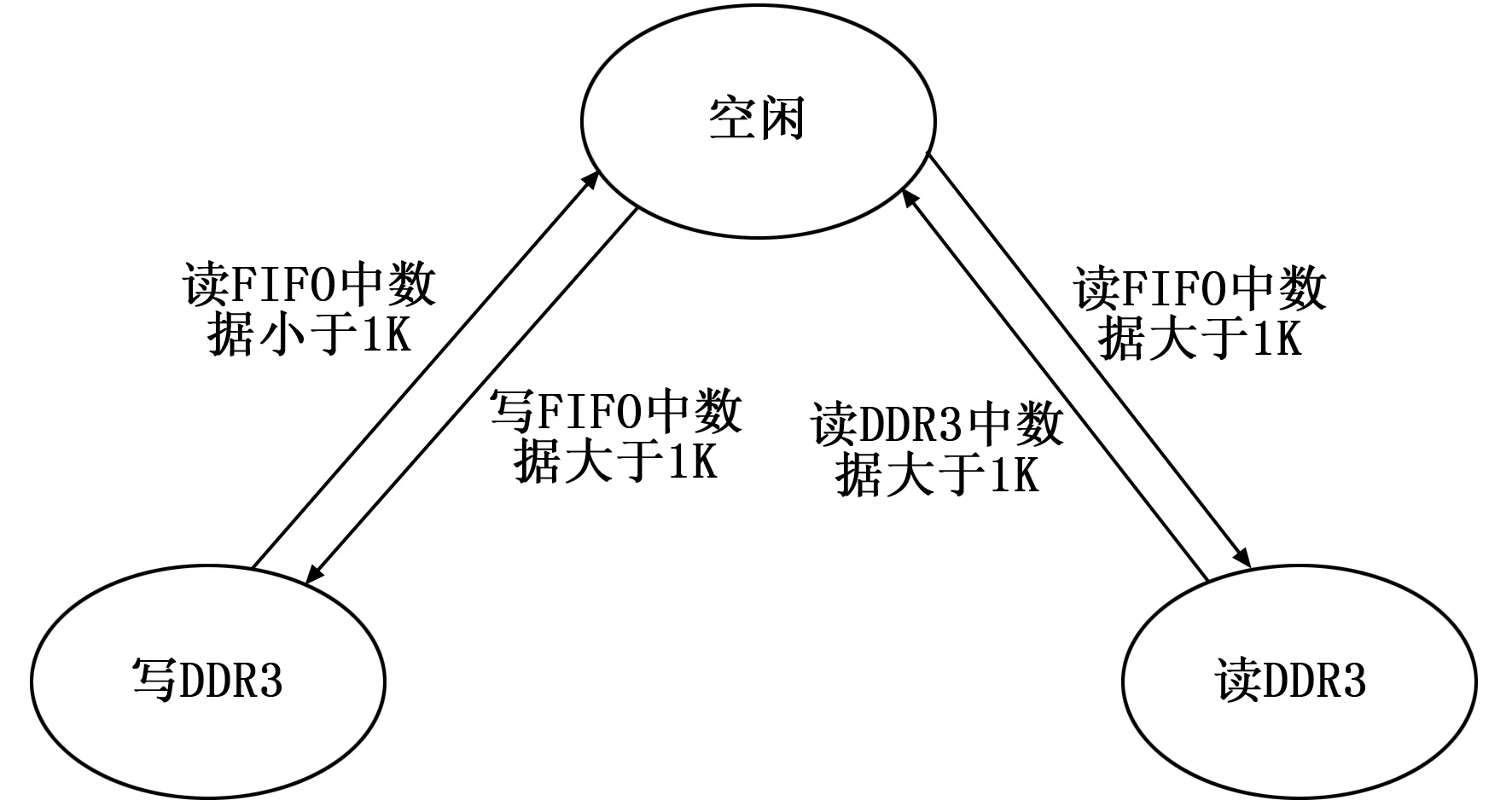

在本次设计中,Camera Link接口输出时,视频信号的数据流要保持恒定的速率不间断输出,因此系统实现中加入了一个内部缓存控制模块,控制DDR3进行分时工作,其工作的状态图如图9所示。

图9 DDR3分时工作状态图

在内部缓存控制模块中加入两个fifo分别作写fifo与读fifo,在Camera Link、接口输出数据时,要判断读fifo中的数据是否低于设定的阈值,若不低于,则继续将fifo中的数据读出,发送到Camera Link接口模块,DDR3保持空闲;若低于该阈值,则DDR3进行读操作,同时读fifo保持数据读出给Camera Link接口模块。对于写fifo同样设定一个阈值,判断写fifo中的数据是否多于设定的阈值,若多于该阈值,则DDR3进行写操作,则将写fifo中的数据写入DDR3,否则DDR3保持空闲。并且DDR3的读命令优先级高于写命令。

在课题中,对相机模拟系统的DDR3 SDRAM进行读写操作调试,向DDR3 SDRAM写入一段数据再读出,不断重复,比较读出的数据是否正确。通过Xilinx ISE工具Chip scope进行波形抓取,实际结果如图10所示。

图10 读写操作的实际时序图

2 上位机软件设计

整个Camera Link相机模拟系统能够完成复杂的数据传输,上位机控制它完成所有的功能。用户可以操作上位机产生或者接收标准的图像数据并下传给模拟系统,发送操作命令并显示当前的状态;并控制系统工作在不同Camera Link的模式配置下,显示当前的模式配置;按照需要输出的图像的分辨率及图像深度,向模拟系统发送相应的指令,完成不同分辨率、帧频以及图像深度的图像数据的输出。上位机用MFC开发,产生或接收标准的视频图像数据,并控制Camera Link接口相机模拟系统,实现数据传输及工作模式的设置,它的设计方案如图11所示。

图11 上位机软件设计方案示意图

3 结论

本文设计的Camera Link相机模拟系统可以实现通过上位机将图像数据经由PCIe2.0接口高速下传给相机模拟,数据下传速率不低于10 Gbps。计算机驱动PCIe2.0接口下传数据的传输速率测试如图12所示。由测试结果可以看出PCIe DMA方式下传数据速率达到1 400 MB/s以上,远高于课题的需求。

图12 PCIe2.0传输速率测试结果

在对本次设计的相机模拟系统进行测试中,使用实验室已具备的Camera Link采集卡对相机模拟系统输出的图像数据进行,采集结果如图13所示。由测试结果可以看出,本课题设计相机模拟系统可以很好的模拟出Camera Link格式图像数据输出。

图13 相机模拟系统数据结果

因此,相机模拟系统可以实现Camera Link接口的Full模式数据的实时输出,完成分辨率为8 000×6 000、像素深度为8 bit的图像的输出,图像输出帧频可达12.5 Hz。本文设计的Camera Link相机模拟系统可以在对星载图像采集处理系统进行检测时,代替高分辨的航天CCD相机,灵活的输出高分辨的特定的测试图像数据。

[1]韦 韧.星载科学试验用CCD相机设计与实现[D].北京:中国科学院空间科学与应用研究中心,2010.

[2]张 坤. 国外星用CCD图像传感器的研制现状[J]. 中国电子科学研究院学报,2007(3):324-328.

[3]吴 川,郝志成.基于FPGA的视频信号发生器设计[J]. 电子技术,2011(3):30-31.

[4]刘 杰,牛燕雄,董 伟,等. 基于FPGA的视频信号发生器设计与应用研究[J]. 仪器仪表学报,2008(3):654-657.

[5]熊 川,李天赞. 基于存储技术的数字视频信号产生器[J]. 桂林航天工业高等专科学校学报,2006(4):6-7.

[6]Wang Mingfu, Yang Shihong, Wu Qinzhang. Design of large-arragy CCD real-time display system [J]. Optics and Precision Engineering, 2010, 18(9): 2053-2059.

[7]He Zhongxiang, Yang Shihong, Wu Qinzhang. Design of a real-time display system based on cameral link[A]. Proceedings of 2009 4th International Conference on Computer Science and Education[C]. Nanning: IEEE, 2009: 431-434.

[8]邬静阳.基于CAMERA LINK接口的虚拟数字相机的研究[D].长春:长春理工大学,2013.

[9]王小艳,张会新,孙永生,等.Camera Link协议和FPGA的数字图像信号源设计[J].国外电子元器件,2008,16(7):59-61.

[10]Wang Minghao, Chen Tao, Wu Xiaoxia. High frame rate digital image acquisition and display system based on camera link interface [J]. Microelectronics & Computer, 2011, 28(3):149-153.

[11]魏 明.基于Camera Link接口的CMOS数字相机技术研究[D].长春:长春理工大学,2005.

DesignofCameraSimulationSystemBasedonPCIe2.0CameraLinkInterface

Lan Gongdun1,Zhao Zhanfeng1,Wei Gaofeng2,Zhou Zhiquan1

(1. School of Information and Electrical Engineering, Harbin Institute of Technology (Weihai), Weihai 264209, China; 2. Weihai Radio and Television Station, Weihai 264200, China)

Currently, a variety of satellites equipped with aerospace CCD cameras to acquire image data. The industrial detection of aerospace image processing system requires the CCD industrial camera with large resolution and higher sensitivity. The video signal interface on camera link is widely used in aerospace CCD camera because of the advantages of high transmission speed and low electronic noise interference. Because of the high price of aerospace CCD industrial camera, and the inflexible output, a camera link interface camera simulation system based on PCIe2.0 is designed to replace the aerospace CCD industrial camera, as the signal source on the detection of aerospace image processing system. The camera simulation system is composed of the FPGA, DDR3 memory, Camera Link driver chip, PCIe interface and other components ,and FPGA is the core .The camera simulation system can realize that the output image resolution is up to 8000×6000, and output specific images required by the industrial detection. Therefore, the camera simulation system can provide stable and flexible high resolution image data to meet the demand by industrial detection of aerospace image processing system.

Camera Link interface; PCIe 2.0; aerospace CCD cameras; FPGA

2017-04-24;

2017-05-15。

兰功盾(1993-),男,辽宁大连人,硕士研究生,主要从事信号处理理论与技术方向的研究。

赵占锋(1980-),男,博士,副教授,主要从事信号处理理论与技术方向的研究。

周志权(1973-),男,博士,教授,主要从事信号处理理论与技术方向的研究。

魏高峰(1967-),男,主要从事信号处理理论与技术方向的研究。

1671-4598(2017)11-0150-04

10.16526/j.cnki.11-4762/tp.2017.11.038

TN911

A