ARINC429总线控制器HI-3582接口设计

2017-12-14许波强袁维力赵亚军陕西凌云电器集团有限公司

许波强 袁维力 赵亚军/ 陕西凌云电器集团有限公司

ARINC429总线控制器HI-3582接口设计

许波强 袁维力 赵亚军/ 陕西凌云电器集团有限公司

本文简要介绍了ARINC429总线和HI-3582总线控制器的特点,结合工程实际,给出了基于FPGA的ARINC429总线控制器HI-3582接口设计思路和方法。

ARINC429总线;FPGA;状态机

引言

ARINC429总线是美国航空无线电公司制定的民用航空数字总线传输标准,它规定了使用该总线的航空电子设备的信息流向和基本数据字的格式。ARINC429总线为单向传输总线,信息只能从通信设备的发送口输出,经传输总线传至与它相连的需要该信息的其他设备的接收口。在需要两个通信设备间双向传输时,则在每个方向各用一根独立的传输总线。ARINC429通信采用双极性归零制的三态码调制方式,具有接口方便、数据传输可靠的特点,目前已广泛应用于导航定位系统、通信系统等机载电子设备中。本文结合工程实际,介绍了HOLT公司推出的ARINC429总线控制器芯片HI-3582的特点,并给出了基于FPGA的接口设计思路和方法。

1.HI-3582总线控制器简介

HOLT INTEGRATED CIRCUITS公司生产的HI-3582是一款性能价格比较高的ARINC429协议芯片。该器件的主要特点有:

● 符合ARINC429总线协议;

● 3.3V逻辑电平工作,可直接与LVTTL电平接口;

● 具有独立的双向接收器和发送器接口;

● 无需驱动,可直接连接ARINC429总线;

● 可编程识别标牌,每个接收器具有16个标牌存储单元;

● 对接收的数据可进行奇偶状态校验;并可对发送数据奇偶状态进行设置;

2.FPGA与HI-3582的接口设计

2.1 接口原理介绍

目前实现与HI-3582的接口通用的方案是采用单片机或DSP直接控制接收和发送数据。该方案的缺点是:由于HI-3582的离散控制信号较多,需要占用大量通用I/O端口,这在系统通用IO资源紧张的情况下,实现较为复杂;并且当数据量较大、发送及双接收通道同时工作时占用系统处理时间较长,影响系统工作效率,且容易造成数据丢失。为此本文提出了采用FPGA与HI-3582进行接口设计,利用FPGA丰富的I/O接口,将HI-3582芯片上所有和FPGA有关的接口管脚都以IO的形式直接连接,在FPGA内建立状态控制机制,实现对HI-3582芯片的数据收发控制处理。该设计能极大减少对单片机或DSP的I/O资源占用,提高了单片机/DSP的工作效率;同时提高了对HI-3582芯片中断请求的响应速度。

2.2 软件设计及实现

2.2.1 软件整体设计。

本设计中ARINC429总线传输速率采用12.5k低速率,数据的更新由DSP通过地址线、数据线完成。

设计采用在FPGA内部建立一个发送FIFO缓存和一个接收FIFO缓存,分别用来存储DSP传来的待发送数据和两路ARINC429总线接收到的数据。在发送FIFO不为空时启动数据的发送,产生HI-3582的发送时序。接收数据时,FPGA依次根据HI-3582的接收状态标志D/R1、D/R2判断并读取数据,当D/R1或D/R2为低电平时启动数据接收,产生HI-3582的接收时序读取HI-3582相应接收缓冲器中的数据,再将读取到的数写入接收FIFO。当FIFO缓冲器中的存储数据量达到编程设置的触发深度时,产生DSP中断信号通知DSP读取数据。

2.2.2 数据读写状态机的设计。

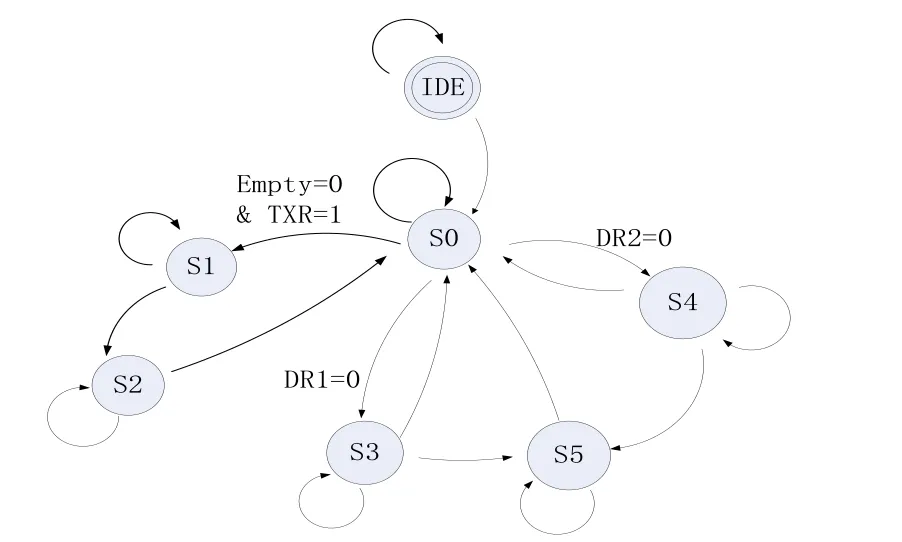

由于对HI-3582的读写操作具有严格的逻辑顺序和时序关系,非常适合采用状态机来描述;所以本设计采用有限状态机来实现读写HI-3582数据。图2为读写HI-3582数据的状态转移图。

IDE:初始化控制寄存器。当系统上电或复位时首先进入写控制寄存器状态,通过产生CWSTR控制时序对HI-3582控制寄存器进行初始化;

S0:收发控制。检测HI-3582发送空闲标志TXR及发送FIFO数据标志empty,如果TXR为高电平说明HI-3582发送处于空闲状态,发送FIFO标志empty为低电平,说明有数据要发送,进入读数据操作状态,否则检测HI-3582接收状态标志D/R1、D/R2,如果D/R1为低电平,进入读取接收通道1数据状态,如果D/R2为低电平,进入读取接收通道2数据状态;

S1:读取发送数据。产生一个FIFO读信号,读取一个待发送的429数据字,进入发送数据时序;

S2:发送控制。依次控制PL1、PL2、ENTX产生HI-3582所需的发送控制时序,将数据发送出去。发送结束后返回收发控制状态;

S3:接收控制1。依次控制SEL、EN1产生HI-3582所需的接收控制时序,读取接收通道1一个接收数据字,进入缓存接收数据状态;

S4:接收控制2。依次控制SEL、EN2产生HI-3582所需的接收控制时序,读取接收通道2一个接收数据字,进入缓存接收数据状态;

S5:缓存接收数据。产生一个FIFO写信号,将读取的429数据字写入接收FIFO,并检测FIFO中存储数据量是否达到编程设置的触发深度,当满足编程设置的触发深度时,产生中断信号,通知DSP读取数据。结束后返回收发控制状态。

图1 发送和接收ARINC429数据的状态转移图

2.2.3 收发控制时序设计。

对HI-3582进行读操作时,由于本设计中ARINC429总线采用12.5k低速率,在FPGA中用1MHz时钟同步一个计数器,在第一个时钟上升沿置SEL为低,HI-3582数据线为高阻;在第二个时钟上升沿置EN1为低,并将HI-3582数据线上的值赋给32位临时寄存器低16位;在第三个时钟上升沿置SEL、EN1为高,HI-3582数据线为高阻;在第四个时钟上升沿置EN1为低,并将HI-3582数据线上的值赋给32位临时寄存器高16位;在第五个时钟的上升沿置EN1为高;到第六个时钟的上升沿FIFO的写信号置低,产生一个FIFO写脉冲将临时寄存器值写入FIFO。这样读取一个ARINC429数据字的有效时间为6个时钟周期(6us),完全满足其读时序的要求。

同样,对HI-3582进行写操作时,按照上述方法产生PL1,PL2、ENTX时序启动发送操作,并检测TXR为高时继续发送下一个ARINC429数据字。

3.结论

按照本文介绍的方法,在Xilinx公司Virtex™-4 系列FPGA芯片XC4VLX40-FFG668的基础上已成功实现与HI-3582的ARINC429航空总线接口设计,并已应用到实际设备中,满足系统要求。

[1]SZ-01数字信息传输系统,HB6096-86,中华人民共和国航空工业部标准.

[2]HI-3582,ARINC 429 System on a Chip,HOLT INTEGRATED CIRCUITS.

[3]Virtex-4 User Guide,UG070 (v2.3) August 10,2007.

[4]VHDL:Programming by Example,Douglas L.Perry,Fourth Edition.