传统电压源型驱动电路与谐振驱动电路对比

2017-12-13雷鹏娟陈颖超王旭升

雷鹏娟,陈颖超,王旭升,刘 剑

(承德石油高等专科学校 a.电气与电子工程系;b.石油工程系,河北 承德 067000)

传统电压源型驱动电路与谐振驱动电路对比

雷鹏娟a,陈颖超b,王旭升a,刘 剑a

(承德石油高等专科学校 a.电气与电子工程系;b.石油工程系,河北 承德 067000)

基于传统电压源型驱动(Voltage Source Driver,VSD)电路驱动过程中产生的损耗大、dv/dt问题引起的开关误导通等问题,对传统VSD电路和电流源型驱动(Current Source Drivers,CSD)电路的驱动过程进行了分析对比。首先对MOSFET的相关知识进行了介绍,接着对以MOSFET为原型的传统VSD电路工作过程进行了分析,在此基础上,分析了电感电流连续的CSD电路工作过程,并与传统VSD驱动电路进行了优缺点对比。最后用Pspice仿真软件进行了仿真验证。仿真结果显示, CSD电路较VSD电路而言,可以大大的减小驱动损耗。验证了CSD驱动方案的正确性和可行性。

VSD电路;驱动损耗;CSD电路;电感电流连续

近年来,随着半导体技术和微电子技术的飞速发展[1-3],诸如高速CPU、FPGA等越来越多的高速数字集成芯片被应用于通信系统中,因此,对这些给芯片供电的小功率电源的要求也越来越高[4],这使得功率变换器开始向着高频化、小型化、高功率密度、高可靠性方向发展。目前,对于功率变换器的驱动更多采用的是电压源型门极驱动(Voltage Source Drivers,VSD)方式,这种驱动方式的驱动损耗会随着开关损耗成比例的增加[5],这样不仅降低了功率变换器的效率,也降低了变换器的可靠性。文献[6]分析了传统VSD电路产生的各部分损耗所占的比例,结果显示,功率开关管Q的门极驱动损耗(CV2)所占比例最大。文献[7]中介绍了一种双通道脉冲谐振门极驱动电路,可以用在推挽电路中。文献[8]对谐振门极驱动电路进行了建模分析,分析了寄生电感对谐振驱动电路的影响。本文首先介绍了MOSFET的相关知识,接着对传统VSD电路工作过程进行了理论分析和仿真验证,针对其工作过程中的问题分析了VSD电路驱动的缺点。在此基础上,重点分析了电感电流连续的电流源型驱动电路(Current Source Drivers,CSD)的工作过程,并进行了优点分析和仿真验证。仿真结果显示,与VSD电路相比,可以大大的减小驱动损耗。验证了该驱动方案的正确性和可行性。

1 传统VSD驱动电路

1.1MOSFET的实际模型

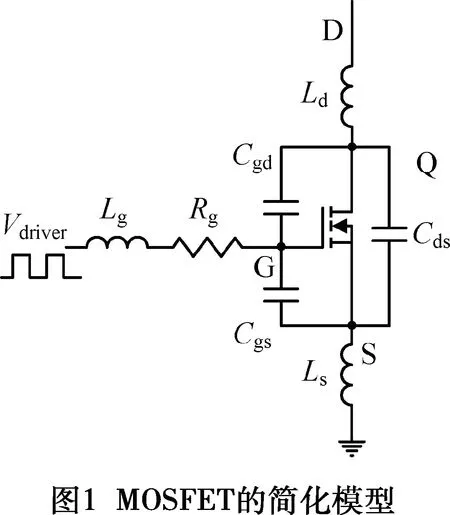

实际应用中,MOSFET存在着一定的寄生参数,并不是理想器件。图1所示为实际的MOSFET模型。其中,寄生参数有:栅极寄生电感Lg,源极寄生电感Ls,漏极寄生电感Ld,栅极电阻Rg,栅源极电容Cgs,漏源极电容Cds和栅漏极电容Cgd。

由于这些寄生参数的存在,使得功率开关管Q的开关过程受到了一定的影响。文献[9]的分析显示,Ld会加重Q的漏源极电压振荡,Ls会使得Q的开关时间增大,此外,功率开关管Q的极间电容与Q的开关损耗相关

1.2VSD电路的工作原理

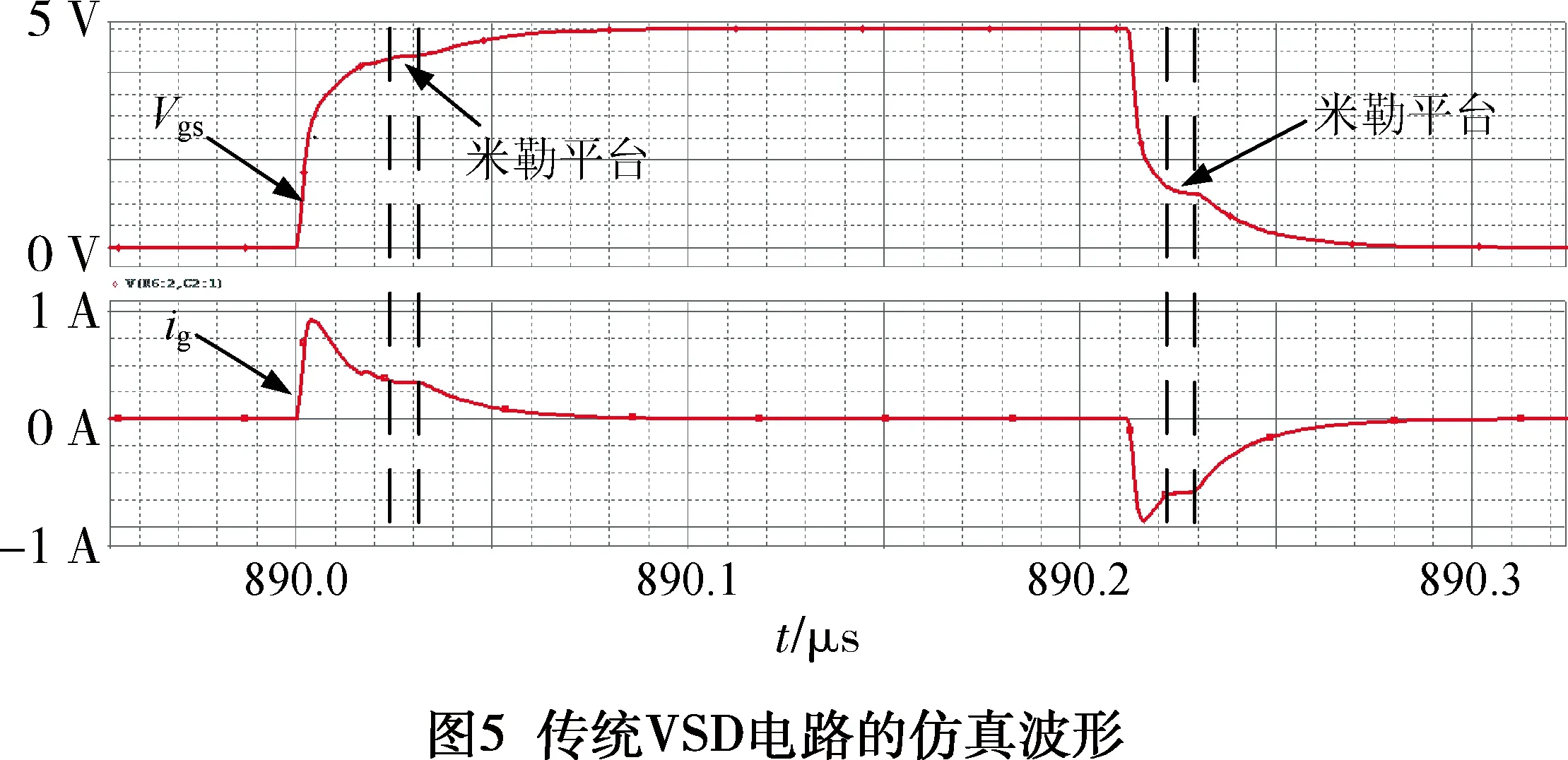

根据对MOSFET元件寄生参数的分析,本文给出了传统的VSD电路及其工作过程所对应的波形,如图2所示,该波形考虑了米勒电容(Cgd)对工作过程的影响。电路结构中,Req为充放电回路的寄生电阻之和,Ci为MOSFET Q的等效输入电容,Vgs为Ci两端的电压,ig为驱动电流。通过对工作过程的分析可知:在驱动开关管MOSFET开通和关断瞬间,驱动电流会迅速升高到最大值然后下降,这使得有效的驱动电流大大减小,减慢了开关速度,也增大开关损耗。

2 谐振型门极驱动

基于传统VSD电路的缺点,为了解决在驱动过程中存在的问题,人们提出了谐振型门极驱动电路。

2.1谐振驱动电路的工作原理

谐振驱动电路的工作原理在于,在原有电路基础上,增加一个谐振电感L,在开关管关断期间,利用与输入电容C发生谐振,使电容中的能量转移到电感L中,以此来快速驱动开关管工作,并达到减小驱动损耗和开关损耗的目的。

2.2电感电流连续的电流源型驱动电路(CSD)

根据电感电流状态,可把谐振驱动电路分为电感电流连续型和断续型两大类。这两类驱动电路各有优劣。本文主要对电感电流连续型驱动电路进行研究和分析。

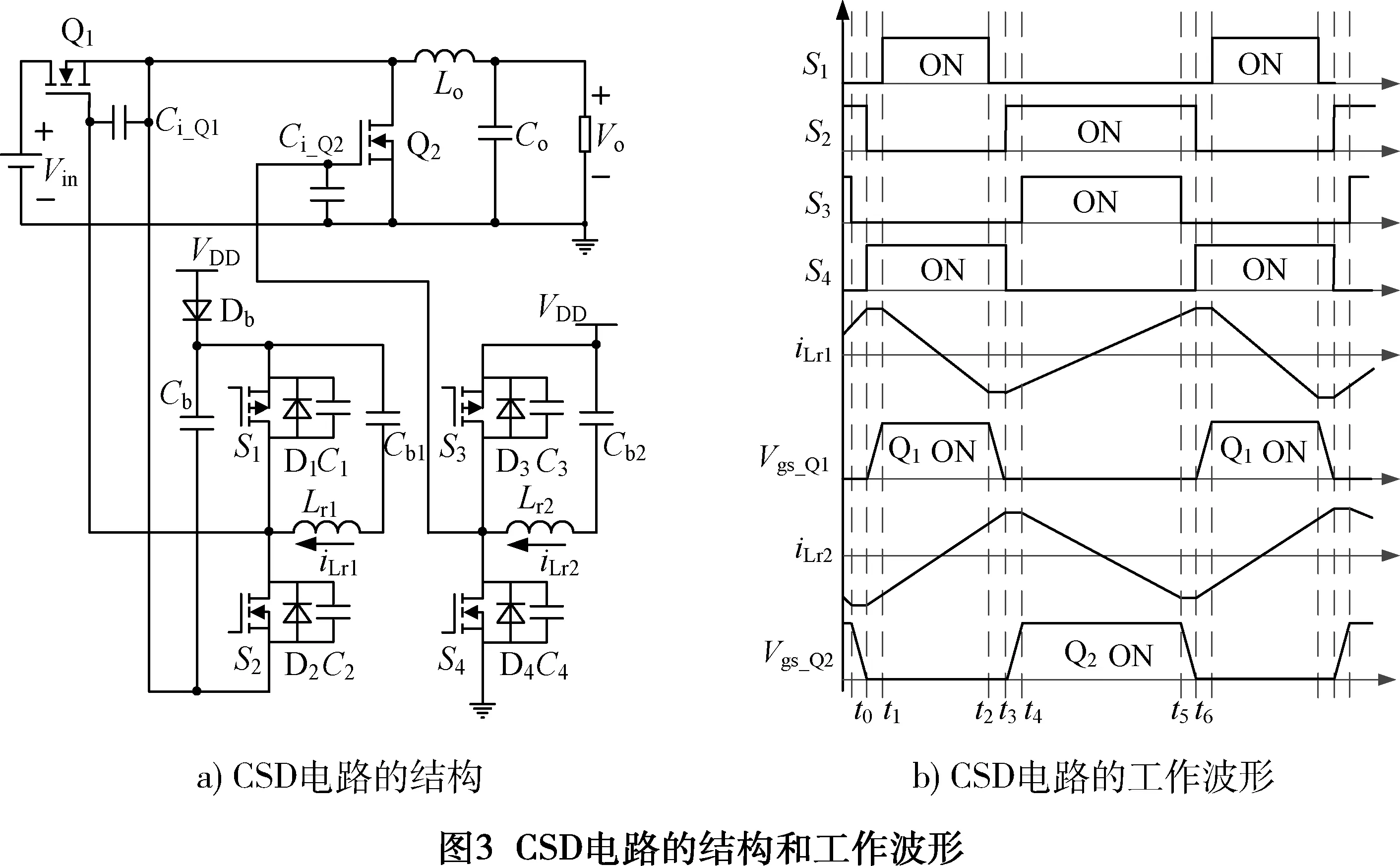

本文所用的谐振门极驱动电路如图3a)所示。CSD电路由四个开关管S1~S4,两个谐振电感Lr1、Lr2,以及两个隔直电容Cb1、Cb2组成。S1和S2、S3和S4的驱动脉冲互补,Ci_Q1和Ci_Q2分别为MOSFET Q1和Q2的等效输入电容。图3b)为CSD电路的主要工作波形,其中,iLr1、iLr2分别为谐振电感Lr1、Lr2中的电流,Vgs_Q1、Vgs_Q2分别为Q1和Q2的栅源极电压。

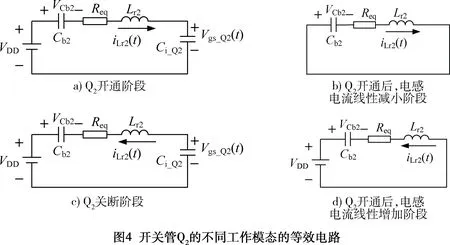

经过分析CSD电路的工作过程,将一个周期分为了6个工作模态,这6个工作模态的等效电路可以总结为如图4所示四种。图4中:Req为驱动回路的寄生电阻之和;Lr2为Q2的驱动电路谐振电感和寄生电感之和;ILr20为电感电流的初始值,Vgs_Q20为电容电压的初始值,VCb2为隔直电容Cb2两端电压。下面将对四种阶段分别进行分析。

根据谐振电感伏秒积平衡可得:

VCb2=DVDD

(1)

式中,D表示S4的占空比,VDD表示CSD1电路的供电电压源。

a)Q2开通阶段

在Q2开通阶段,电压Vgs_Q2(t)和电感电流iLr2(t)分别为:

(2)

(3)

b)Q2开通后,电感电流线性减小阶段

在这个阶段,电感电流iLr2(t)为:

(4)

c)Q2关断阶段

在这个阶段,电压Vgs_Q2(t)和电感电流iLr2(t) 分别为:

(5)

(6)

d)Q2开通后,电感电流线性增加阶段

在此阶段,电感电流iLr2(t)为:

(7)

2.3CSD电路的优点

相比于传统的VSD电路,CSD电路的优点主要表现为以下几个方面:

1)提前给谐振电感Lr1、Lr2充电,可以快速驱动功率开关管开通和关断,减小开关损耗;2)辅助开关管均可实现零电压开关(Zero Voltage Switching,ZVS),减小了辅助开关管的开关损耗;3)该电路可以回收利用开关管导通时的能量;4)快速驱动开关管开通关断,可以减小Q1和Q2驱动脉冲之间的死区时间,从而减小Q2体二极管的导通损耗;5)该电路可以提供一个低阻抗路径,提高了电路的抗干扰能力。

3 仿真分析

3.1传统VSD电路仿真

以图2所示传统VSD电路为模型,用Pspice仿真软件进行了仿真,仿真结果如图5所示。仿真结果显示,在驱动开关管Q的过程中,ig会首先达到最大值然后迅速下降,使得开关过程变慢。此外,在Q开关过程中,Vgs会出现一个“米勒平台”,使得开关损耗增加。由此可见,仿真结果与理论分析一致。

3.2电流连续型CSD电路仿真

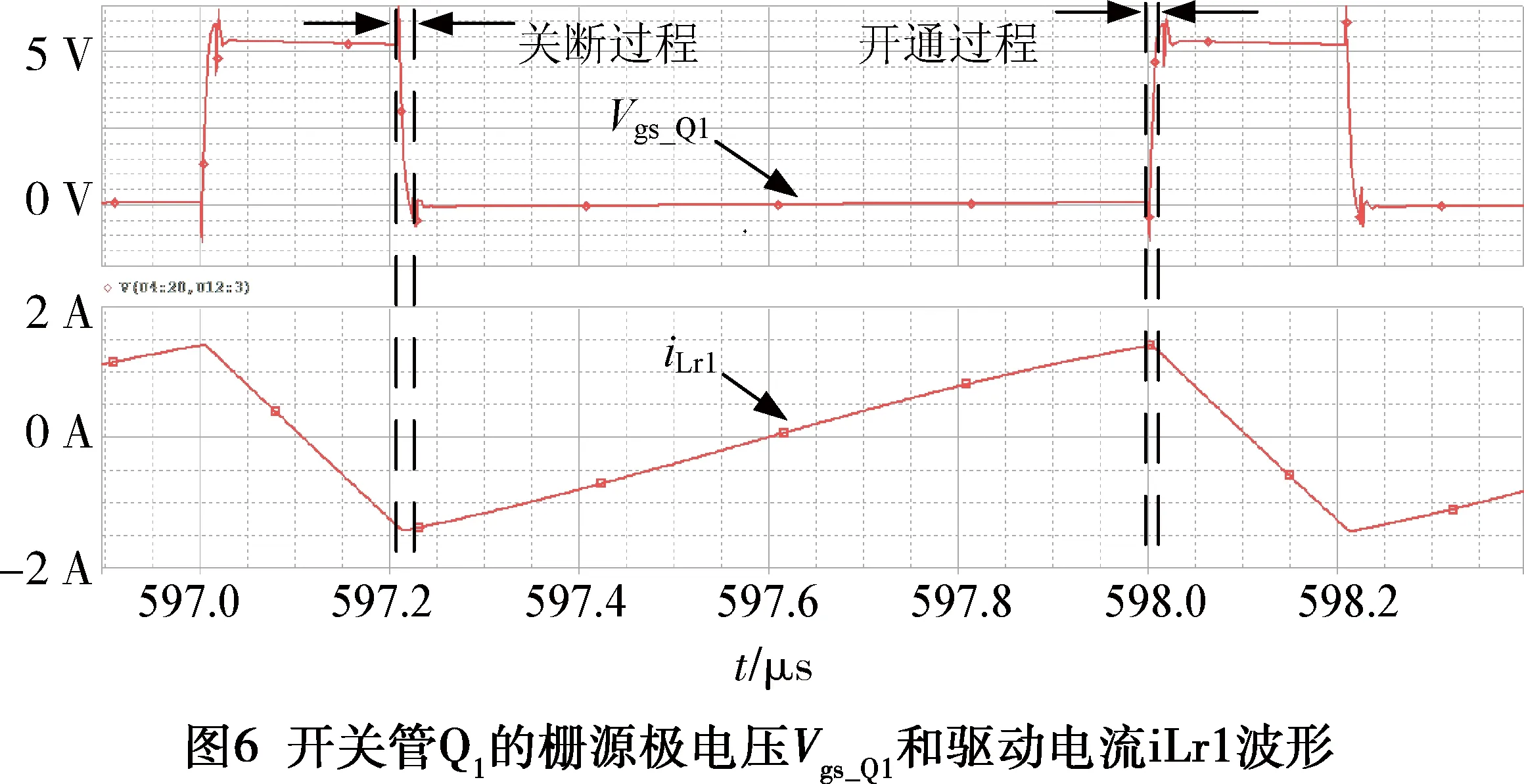

为了验证CSD电路理论上的可行性,用Pspice仿真软件进行了仿真验证。仿真参数为:输入电压Vin=12 V,输出电压Vo=2.5 V,输出电流Io=15 A。驱动电压VDD=5 V。图6和图7所示分别为开关管Q1、Q2的驱动信号和谐振电感Lr1、Lr2中的电流。由图可知,电感电流连续且在电流最大时驱动功率管Q1、Q2快速地开通和关断,辅助开关管均工作在ZVS状态,仿真结果与理论分析保持一致。

图8所示为开关管Q、Q2的栅源极电压和驱动电流的仿真波形,从图8可知,适当的控制驱动时序,就可大大地减小死区时间,减小Q2的体二极管导通产生的损耗。

4 结论

基于传统VSD电路驱动过程中产生的损耗大、dv/dt问题引起的开关误导通等问题,本文对传统VSD电路和CSD电路的驱动过程进行了分析对比。首先介绍了MOSFET的相关知识,接着对传统VSD电路工作过程进行了理论分析,针对其工作过程中的问题分析了VSD电路驱动的缺点。在此基础上,分析了电感电流连续的电流源型驱动电路(CSD)的工作过程。最后用Pspice仿真软件进行了仿真验证。仿真结果显示,与VSD电路相比,CSD电路可以大大的减小驱动损耗。验证了CSD驱动方案的正确性和可行性。

[1] 杨立功, 于晓权, 李晓红,等. 半导体可靠性技术现状与展望[J]. 微电子学,2015(3):391-394.

[2] 黄庆红. 国际半导体技术发展路线图(ITRS)2013版综述(1)[J]. 中国集成电路, 2014, 23(9):13-28.

[3] 赵正平. GaN高频开关电力电子学的新进展[J]. 半导体技术, 2016(1):2-9.

[4] 赵亚光,李静.基于单片机的直流电子负载的设计[J]. 承德石油高等专科学校学报,2015(4):30-34.

[5] 赵辉, 徐红波. MOSFET开关损耗分析[J]. 电子设计工程, 2015, 23(23):138-140.

[6] Lopez T, Sauerlaender G, Duerbaum T, et al. A detailed analysis of a resonant gate driver for PWM applications[C].Applied Power Electronics Conference and Exposition, 2003. APEC’03. Eighteenth Annual IEEE. IEEE, 2003:873-878 vol.2.

[7] Ma Y, Liu L, Xie X, et al. Dual Channel Pulse Resonant Gate Driver[C]//Industrial Electronics and Applications, 2007. ICIEA 2007. 2nd IEEE Conference on. IEEE, 2007:2317-2321.

[8] Zhang Z, Fu J, Liu Y F, et al. Switching loss analysis considering parasitic loop inductance with current source drivers for buck converters[J]. Power Electronics IEEE Transactions on, 2010, 26(7):1815-1819.

[9] Xiao Y, Shah H, Chow T P, et al. Analytical modeling and experimental evaluation of interconnect parasitic inductance on MOSFET switching characteristics[C].Applied Power Electronics Conference and Exposition, 2004. APEC ’04. Nineteenth Annual IEEE. IEEE, 2004:516-521 Vol.1.

ContrastiveAnalysisBetweenTraditionalVoltageSourceDriveCircuitandResonantDriveCircuit

LEI Peng-juana, CHEN Ying-chaob, WANG Xu-shenga, LIU Jiana

(a.Department of Electrical and Electronic Engineering;b.Department of Petroleum Engineering, Chengde Petroleum College, Chengde 067000, Hebei, China)

Based on the problem of the power loss occurring in the process of driving circuit and dv/dtproblem caused by the problem such as switches misleading in the traditional Voltage Source drive (Voltage Source Driver, the VSD), contrastive analysis of the driving process has been worked between the traditional VSD circuit and Current Source Driver (CSD) in this paper. First, the knowledge of MOSFET is introduced, and then the working process of the traditional MOSFET as the prototype of the VSD circuit is analyzed. On this basis, the continuous current mode working process of the CSD circuit is analyzed, and the advantages and disadvantages are compared with traditional VSD drive circuit. Finally the simulation with Pspice software is validated. Compared with the VSD circuit, the simulation results show that the CSD circuit can greatly reduce the power loss, and it verified the correctness and feasibility of the CSD drive scheme.

VSD circuit; drive loss; CSD circuit; continuous current mode

TM464

A

1008-9446(2017)05-0044-05

2016-12-06

雷鹏娟(1986-),女,山西汾阳人,讲师,硕士,主要从事直流微电网方面的研究,E-mail:664865836@qq.com。