基于DDWS的波形产生器的设计与实现

2017-11-16王海松陈曾平

王海松,张 月,陈曾平

(国防科学技术大学 ATR重点实验室,湖南 长沙 410073)

基于DDWS的波形产生器的设计与实现

王海松,张 月,陈曾平

(国防科学技术大学 ATR重点实验室,湖南 长沙 410073)

针对数字化、软件化雷达波形产生的需要,文中提出了一种以软件无线电平台为基础、基于直接数字波形合成(DDWS)技术的实现方案。该方案采用一种免混频方法和多相内插滤波器相结合的高效方法来实现DDWS技术,通过大容量高速FPGA+DAC的硬件设计,以及上位机实现任意频率的选择,构成一个完整的波形产生器。经过对系统的性能分析和测试表明,该系统具有波形输出稳定,精度高等优点,而且可以输出射频、窄带以及宽带信号。

直接数字波形合成;多相内插滤波器;波形产生;Virtex6-XC6VLX240T;EV12DS130A

直接数字合成(Direct Digital Synthesis,DDS)相比传统的信号源器件,具有体积小和功耗低等特点,因此DDS技术是新一代信号源发展的标志[1-3]。DDS分为直接数字频率合成(DDFS)和直接数字波形合成(DDWS)两种[4],其中DDFS已有大量集成芯片,二次开发方便,缺点是电路设计完成后很难根据需求产生不同带宽、载频的波形。而DDWS通过合理选择FPGA和DAC进行搭配实现复杂波形的产生,最重要的是具备用户自定义和编程功能[5],弥补了DDFS性能上的不足。但是存储的波形数据长度受到高速存储器的存储容量的限制,而且由于数字器件工作频率的限制,信号输出带宽有限[6,7]。本文提出了一种将FPGA与DAC结合代替传统 DDS芯片的方案[8],通过优化的上变频(Digital Up Converter,DUC)结构有效解决了波形产生过程中存储器容量和硬件资源限制的问题,实现多种波形的产生。

1 DDWS和DUC原理

1.1 DDWS的组成及原理

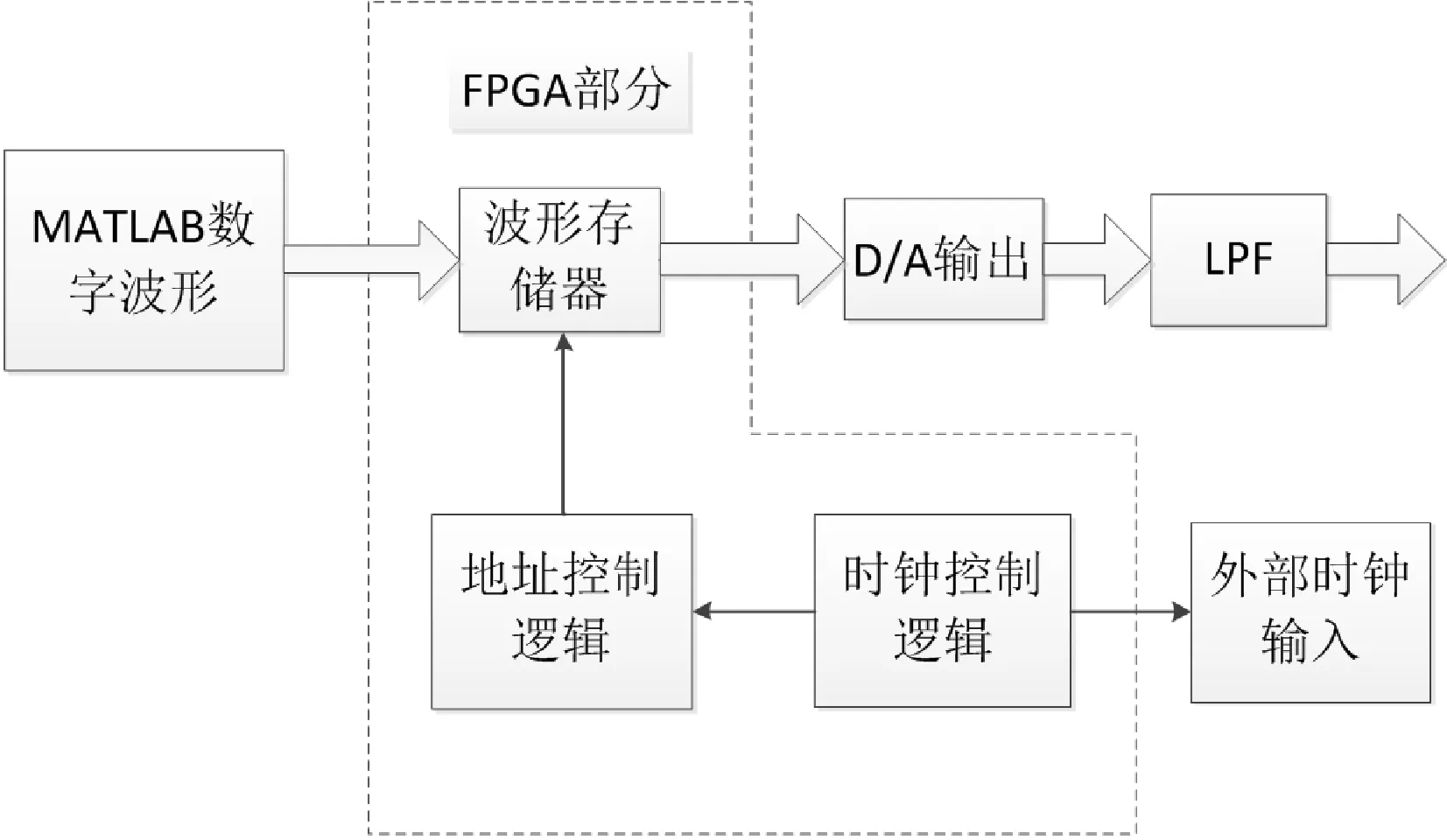

DDWS一般采用“FPGA + RAM + DAC”的方式来实现。其基本原理为:根据预定的采样频率,及所需基带信号的带宽、脉宽等参数,根据信号的数学表达式由Matlab计算出波形信号各点采样值,按照采样先后顺序保存成文件预先存储在高速内存中或上位机再通过PCI Express下发到高速存储器中。通过对采样时钟计数产生高速地址并寻址内存,依次读出采样数据进行转换,再经由D/A产生所需模拟信号[9-10]。DDWS组成原理如图1所示。

图1 DDWS系统框图

1.2 DUC实现原理

DUC的作用是将基带信号变频到载波频率上,是软件无线电发射机中的核心技术之一。其工作原理是:基带信号经过内插滤波器提高采样率,并滤除由于信号内插产生的镜像分量,再与数控振荡器(NCO)产生的正交本振信号进行数字混频,得到中频或射频信号,典型结构如图2所示。

图2 DUC的典型实现结构

这种DUC结构的运算资源量和处理速度难以满足高数据率要求。本文设计的基于大容量高速FPGA+DAC结构的硬件平台,采用多相内插FIR滤波器的高速DUC实现结构,极大减少了FPGA的存储空间和乘法器的使用量。其中FPGA板卡上支持FMC(FPGA Mezzanine Card)接口。因此为了提高模块化水平,将DAC子卡设计成FMC子卡形式。因为DAC的数据、时钟输入以及控制信号都来自FMC插座,所以DAC子卡必须依赖于FPGA板卡结构。

高速DUC的基本特点是内插倍数大,内插后的数据率高。由于内插倍数大,低通滤波器的过渡带变小,为获得较好的带外抑制性能,滤波器阶数会相应地增大,意味着实现低通滤波所使用的乘法器将增多。用FPGA实现高速DUC时,需要设计、采用合适的滤波器结构以减少乘法器的使用量。

2 基于多相内插滤波器的DUC

2.1 二次混频的DUC实现结构

从窄带信号出发来设计波形产生系统,根据实际要求,输出窄带信号载频为1 200~1 400 MHz,脉内信噪比>60 dB,考虑到最佳采样频率fs和中心频率f0之间的关系[11]

fs=4f0/(2m0-1)

(1)

为满足中心频率f0在1 200~1 400 MHz范围之内,取m0=3,此时采样频率fs为1 040 MHz。为满足设计需求采用“二次混频”的方法[12-13]来实现窄带的DUC,从而达到带宽变化范围为200 MHz。改进的系统设计结构如图3所示。

图3 DUC的优化结构

基本思路是将5 MHz的基频信号进行两次2倍插值,再进行一次13倍插值,将基带信号采样率提高到260 MHz,然后利用DDS结构实现第一次混频,因为系统采样率1 040 MHz,所以通过免混频结构将260 MHz提高至1 040 MHz,同时将复信号转化为实信号。这种实现方法的优点是先利用DDS产生本振信号进行第一次混频,由于DDS输出频率可以软件控制,兼顾了速度和灵活性;然后利用免混频的结构进行“二次混频”,解决了高数据率下的DUC问题。

2.2 基于多相滤波的结构优化

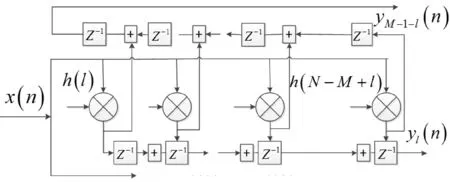

为节省乘法器资源和存储资源,采用多相内插滤波器的结构,这种结构由“内插”和“低通滤波”两部分组成,在实现高速DUC时经常采用这种结构,如图4所示[14]。

图4 多相内插滤波器的结构

图4中第m个分支滤波器定义如下

(2)

其中,n=0,1,M-1,hm(n)是低通滤波器的系数;M是内插倍数;N是低通滤波器的阶数。假设多相滤波后y(n)的数据率是D,那么多相滤波器的单个工作频率为D/M,所以多相滤波器的基本结构需要N个乘法器,寻找节省乘法器的方法可以优化多相滤波结构。由式(2)得,第M-1-m个滤波器的表达式为

(3)

在多相内插滤波器中,由式(2)和式(3)得Rm(z)和RM-1-m(z)直接实现结构如图5所示。

图5 多相滤波器分支结构

其中ym(n)是Rm(z)的输出,由式(3)得

(4)

线性相位FIR滤波器系数满足如下条件:h(n)=h(N-1-n),其中n=0,1,N-1。所以在多相滤波器结构中,Rm(z)的第n个系数和RM-1-m(z)的第N/M-1-n个系数相等。即

rm(n)=fliplr(rM-1-m(n))

(5)

其中n=0,1,N/M-1,fliplr代表时间反褶,rm(n)是分支滤波器Rm(z)的冲激单位响应。所以多相滤波器的分支结构可以简化为如图6所示的结构。

图6 多相滤波器分支简化结构

可以看出这种线性相位FIR滤波器结构使得多相内插滤波器消耗的乘法器减少一半,而且不会增加工作频率。

2.3 免混频结构的实现

由图2结构可知,实信号x(n)是由插值滤波后的I(n)和Q(n)分别与两个正交本振cos(w0n)和sin(w0n)相乘(混频)得到的。即

(6)

由式 (6)以及图3和图4可知,当n=0、1、2、3时,本振cos(πn/2)值为1,0,-1,0;sin(πn/2)值为0,1,0,-1;所以

DA_0=I‴(4m)×cos(2mπ)+

Q‴(4m)×sin(2mπ)=I(4m)

DA_1=I‴(4m+1)×cos(πm/2)+

Q‴(4m+1)×sin(πm/2)=Q(4m+1)

DA_2=I‴(4m+2)×cos(mπ)+

Q‴(4m+1)×sin(mπ)-I(4m+2)

DA_3=I‴(4m+3)×cos(3πm/2)

Q‴(4m+3)×sin(3πm/2)=-Q(4m+3)

(7)

即多相滤波过程简化为如图7所示的结构。

图7 多相内插滤波优化

在这种多相滤波器优化结构中,本振信号的输出只有1,0,-1,0共4个特殊值,因此无需进行混频,因此也称为“免混频”结构[15]。这种结构降低了DUC的实现难度,提高了滤波器运算精度。

3 基于硬件平台的DDWS技术

3.1 FPAG和DAC器件选择

本文所采用FPGA+DAC结构实物如图8所示。

图8 FPGA+DAC结构

其中FPGA采用Xilinx公司推出的Virtex6系列高性能芯片XC6VLX240T实现DDWS技术。该芯片在运算速率和传输性能等方面都具有良好的性能,选用第2代PCI Express通信,支持4×和8×位宽模式,系统采用4×模式,理论速率和实际速率分别为2 Gbit·s-1和1.5 Gbit·s-1。

为满足对信号带宽和频段的要求,选用E2V公司的EV12DS130A的DAC器件,该芯片具有高采样率、大输出带宽且具有较高分辨率,分辨率为12 bit,采样率高达3 GSample·s-1,模拟输出带宽为6 GHz,功耗仅1.3 W。

歌舞声中,金樽奖的十周年系列活动落幕。但站在今年所取得的成绩上,也让我们开始去思考金樽奖下一个十年应该要走的路。我很认同颁奖典礼上,David Allen MW所说的一句话:“获奖酒款都是裁判们秉持不偏不倚的态度选出来的。按照我们的评选结果,即便毫无经验的消费者也能够完全放心地尝试和购买自己未尝试过的、不同风格的葡萄酒。在葡萄酒世界里,这样组织有方的葡萄酒比赛会让所有人都能受益。”金樽奖所秉承的理念中,应该是成为一项能让大众受益的标准,而金樽奖下一个十年也将继续为爱好葡萄酒的你们一同分享与美酒有关的美好生活。

3.2 基于FPGA+DAC的数字DUC实现

FPGA实现数字DUC的基本步骤如下:

步骤1使用Matlab生成基频信号的I、Q两路信号,存储在上位机中。数字波形量化位数为12 bit满足信号输出幅度要求;

步骤2根据相关指标,使用Matlab工具箱Fdatool设计滤波器,对其系数进行量化,生成相应的系数文件;

步骤3在集成开发环境ISE中,使用IP 核生成器Core Generator生成FIR Compiler,将系数文件添加到IP Core中,并对其进行相关的设置,生成符合条件的FIR滤波器。生成DDS Compiler和Clocking Wizard模块并完成DUC主模块程序编写。

4 DAC性能分析和系统测试结果

4.1 DAC性能分析

为适应不同需求,该DAC芯片有4种工作模式,分别是NRZ(Non Return to Zero)、NRTZ(Narrow Return To Zero)、RTZ(Return to Zero)和RF输出模式。对该芯片的主要性能进行测试,其中输出幅频特性和无杂散动态范围(Spurious Free Dynamic rang,SFDR)特性测试结果如下。

图9 幅频特性

图10 SFDR特性

从以上测试结果可以看出,针对该系统的应用要求,选择RF输出模式以达到最大的信号输出功率和最高的SFDR性能。下图是该系统输出2.9 GHz点频信号和1.8~2.4 GHz宽带信号的频谱测试结果。

图11 点频信号测试结果

图12 宽带信号测试结果

4.2 系统仿真结果

本设计中FPGA+DAC主要包含4个模块:PCI Express模块、DUC主模块、DAC配置模块、DAC输出模块。PCI Express模块用来实现基频信号数据和控制指令传输;DUC主模块实现DUC和混频功能;DAC配置模块设置DAC输出模式、时钟分频因子等。DAC输出模块产生读写BRAM地址、信号转化及波形输出。DUC主模块经过Modelsim仿真,功能正确。仿真结果如下,图13中8路波形分别是基频信号、第一次2倍插值滤波、第二次2倍插值滤波后以及13倍插值滤波之后的I、Q路时域波形。

图13 多次插值结果

经过插值之后对260 MHz采样率下的信号进行第一次混频处理,混频频率29.83 MHz,如图14所示。

图14 第一次混频

在第一次混频的基础上进行4倍插值,然后通过免混频将信号从29.83 MHz搬移到1 329.83 MHz。结果如图15所示。

图15 多相滤波+二次混频

4.3 工程实践结果

工程实测平台选用安捷伦公司的N9010A频谱仪,如图16(a)所示,从信号的频谱特性来看,信号在输出带宽内的镜频干扰被很好地抑制,频谱非常干净,幅值达到-16 dB。经过实测检验成功将基频信号搬移到了1329.83 MHz处,且有效的抑制了信号的杂散(脉内信噪比>60 dB),如图16(b)所示。满足了设计要求,也满足了发射机对发射信号的要求。

图16 信号频谱

5 结束语

本文从“节省存储空间和乘法器资源”和“针对高数据率”两个角度出发设计了一种用FPGA+DAC结构实现DDWS技术产生复杂波形的方法。针对多相内插滤波器,利用线性FIR滤波器系数的对称性及多相滤波器系数的分配特点设计了一种可节省乘法器资源的高效DUC实现结构;采用免混频的思想,基于二次混频的结构实现高数据率的要求。该系统大幅减少了FPGA的存储空间和乘法器的使用量,解决了在复杂波形产生时遇到的器件存储空间有限和运算量大的问题。最后给出DAC性能分析和系统测试结果,验证了该系统的可行性和有效性,是较为理想的雷达波形产生系统。

[1] Daniels D Caliglia,Alessandro De Gloria. Design and construction an arbitrary waveform generator[J].IEEE Transactions on Information and Measurement,1983,32(3): 398-403.

[2] 杨峰,文枰.基于FPGA 的正交信号发生器设计[J].四川文理学院学报,2015,25(5): 47-49.

[3] 张铮,胡婷.基于AD9854的多功能高精度DDS信号源设计[J].电子科技,2017,30(3): 182-184.

[4] 顾赵宇,王平,傅其详.一种基于DDS的信号源的设计与实现[J].现代电子技术,2015,38(5):51-53.

[5] 任艳玲. 基于AD9850的多功能信号源设计[J].电子科技,2015,28(6):179-184.

[6] 齐恒.高性能DDWS雷达信号发生器的设计与实现[D].杭州:浙江大学,2005.

[7] 赵志勇,常文革.DDWS系统误差补偿方法研究[J].现代雷达,2014,36(1):19-24.

[8] 杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001.

[9] 贺军义,蒋坚,李男男.基于FPGA的DDS信号发生器设计[J].计算机测量与控制,2017,25(2):231-233.

[10] 杨峰,文枰.基于FPGA的正交信号发生器设计[J].四川文理学院学报,2015,25(5):47-49.

[11] Kohlenberg A.Exact interpolation of band-limited functions[J].Journal of Applied Physics,1953,24(12): 1432-1436.

[12] John L,Brown J R.First-order sampling of bandpass signals-a new approach[J].IEEE Transactions on Information Theory,1980,26(5):613-615.

[13] 王国庆.大带宽雷达数字I/Q 信号获取技术研究[D].长沙:国防科学技术大学,2009.

[14] 胡广书.现代信号处理教程[M].北京:清华大学出版社,2004.

[15] 王飞雪.直接序列扩频信号的全数字式快速捕获[D].长沙:国防科学技术大学,1998.

Design and Implementation of Waveform Generation Based on DDWS

WANG Haisong,ZHANG Yue,CHEN Zengping

(Key Laboratory of Automatic Target Recognition,National University of Defense Technology,Changsha 410073,China)

This paper aims at the requirement of digital and software radar waveform generation,an implementation scheme is presented based on software radio and DDWS techniques.In this scheme,an efficient implementation scheme is proposed,which combines the free mixing frequency method with the structure of poly-phase interpolation filter.Through the hardware design of large capacity high-speed FPGA+DAC structure,and the upper machine realizing the choice of arbitrary frequency to form a complete waveform generator.After the performance analysis and the final test of the system shows that,the system has good stability,high accuracy,and the capability output of RF signals,narrowband signals and wideband signals.

direct digital wave synthesis;ploy-phase interpolation filter;waveform generation;Virtex6-XC6VLX240T;EV12DS130A

TN911.34

A

1007-7820(2017)11-016-05

2017- 01- 07

国家自然科学基金(61571449)

王海松(1991-),男,硕士研究生。研究方向:雷达系统波形产生和雷达信号处理。张月(1980-),男,博士,讲师。研究方向:高速数据采集和雷达信号处理。陈曾平(1967-),男,博士,教授,博士生导师。研究方向:雷达信号处理等。

10.16180/j.cnki.issn1007-7820.2017.11.005