测试过程与管脚结构的相互作用

2017-11-10李兴鸿赵俊萍方测宝

李兴鸿,赵俊萍,王 勇,方测宝,黄 鑫

(北京微电子技术研究所,北京 100076)

测试过程与管脚结构的相互作用

李兴鸿,赵俊萍,王 勇,方测宝,黄 鑫

(北京微电子技术研究所,北京 100076)

本文从数字CMOS集成电路的I/O结构、全ESD防护结构、自动测试设备的PMU、恒压源恒流源的原理出发,综合分析了功能测试及PMU测试过程中加压测流和加流测压与IC输入、输出、三态及双向管脚的相互作用,给出了一些测试过程对IC造成影响的可能性,以及对IC管脚性能影响的规避措施。

CMOS IC;精密测量单元;测试过程;管脚;相互作用

前言

集成电路(IC)由外围输入输出管脚电路及内部核心电路构成。管脚(Pin)电路结构及功能多种多样。如输入(IN)、输出(OUT)、输入输出双向(I/O)、电源和地管脚等。而由于接口标准、制造工艺、电源电压的差别或要求不同,导致各种管脚模块的具体功能和参数差别很大。集成电路要进行各种测试,重要的就是用自动测试设备(ATE)测试管脚的漏电、电平、驱动能力等性能参数。

在测试标准中大部分参数都有明确的测试方法,但也存在一些未描述或含混的地方。在测试向量长及测试设备复杂情况下,有些与设备相关的测试细节还要靠人去调整。因此会出现不同的测试实施方式。测试通过(Pass)时一般不会关注实施细节,未通过(Fail)时难于辨别关键因素。有鉴于此,本文就从集成电路管脚电路结构、测试过程、测试模块等几方面进行探讨,力图说明其相互影响,避免对器件的误判和漏判。

1 CMOS数字IC管脚相互关系

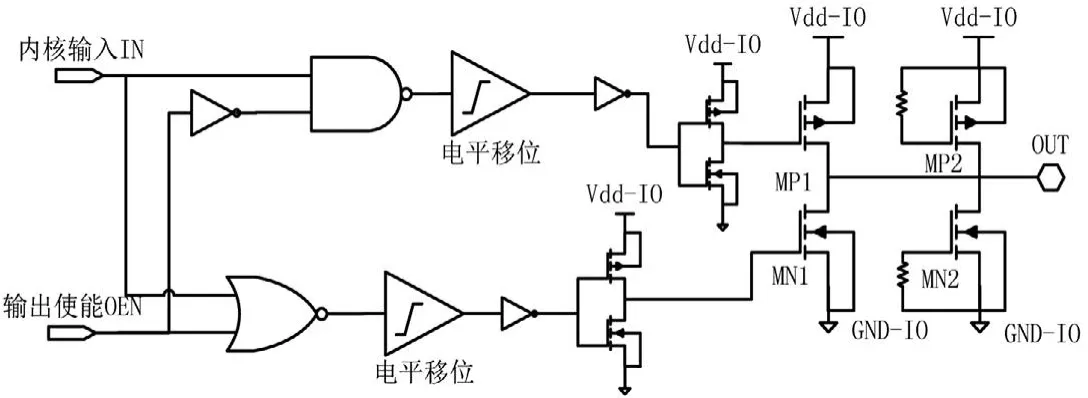

图1为内核低电平输入与外围高电平输出同相的三态输出管脚原理图[1]。其中,MN1 、MP1为输出级,MN2、MP2及电阻为静电放电(ESD)防护结构, CMOS反相器为MN1 、MP1的预驱动级。

图1 三态输出管脚(左)及低到高电平移位(右)原理图

双向I/O的输出与图1类似,而输入可为斯密特输入或普通CMOS输入,但要加输入使能IE、初级和次级的ESD保护结构等结构。

从ESD保护来看,一个完整的多电源多地全芯片ESD保护网络应由I/O ESD保护电路、电源箝位ESD保护电路和电源(地)间ESD保护电路组成[2]。也就是任何管脚间均有一定方式的ESD保护结构,在小直流电压下,管脚间均可用二极管或二极管串来进行等效。

2 精密测量单元的输出

精密测量单元(PMU)是ATE的重要组成部分。PMU是源和测量的有机整体,具有施电压测量电流(FVMI)、施加电流测量电压(FIMV)等功能,原理图如图2所示[3]。PMU结构中采用了高精度大倍数放大器输入端的“虚短虚断”原理进行电流电压参数的设置及测量。PMU结构中还具有优质缓冲器、精密电阻,并使用开尔文接法。构成的反馈回路获得了稳定的电压值或电流值,构成的测量回路得到了精确的测量值。测试过程中,通过高精度DA转换器产生激励源,再通过高精度AD转换器检测响应,最后对比分析响应结果和预期结果来评判集成电路的性能参数。PMU功能模块有高低不同的多种电压档位和电流档位。

给器件施加电压或电流的缓冲器由MOS或双极大功率构成,缓冲器输出端通过量程电阻与负载相接,负载的另一端接地。采样控制的是调整管的栅压或基极电流。从晶体管输出特性可见,PMU稳压或恒流在负载上产生的电压不会超过与PMU档位对应电源电压。

3 管脚直流电参数测试时电流路径

对于以CMOS为主的数字集成电路,直流参数测试主要包括输入高低电平电流(Iih/Iil)、输出高/低电平(Voh/Vol)和静态电源电流。具有高阻态输出的管脚,还要测试高阻态时管脚的高低电平漏电流(Iozh/Iozl)。

对于普通输入管脚,在电路上电后直接测试。对于输出、双向I/O管脚、三态输出管脚,则要在集成电路上电后使测试向量运行到规定的管脚状态下再进行测试。测电压的方法是加流测压,测电流的方法是加压测流。功能测试时有时用电子动态负载(就是电流负载)进行阈值对比测试判断好坏[3]。精确测量时仍要用PMU测试的。不管是动态负载还是PMU测试,器件都将通过档位电阻接缓冲放大器。

图2 PMU原理框图

3.1 加压测流电流路径

加压测流就是给管脚与地之间加规定的电压同时测量通过这两端的电流,主要发生在输入管脚,三态高阻漏电流的测试方法也是加压测流。

3.1.1 纯输入端加压测流

加高电平时主要测量的是输入对地管子结构(包括ESD保护结构)的漏电流特性。

加低电平时主要测量的是输入对电源管子结构(包括ESD保护结构)的漏电流特性。

有上下拉电阻时可根据电阻值预知其值,无上下拉电阻时趋于很小。测试结果为在测试精度范围外给出一些不确定的、量值很小的数值,如pA,nA量值。

一般规定电流流入DUT为正,流出为负。正常情况下Iih应为正, Iil为负。若符号不对,一般不是ATE输入电平与电源电压设置不匹配,就是器件出现了电阻型漏电通路。

3.1.2 双向端及三态输出高阻态加压测流

对于I/O双向端及三态输出高阻态,要待输出变为稳定的高阻态时再加压测流,以免出现大电流。多管脚并行测试时要仔细检查定时关系,否则大电流脉冲在芯片电源和地线上产生的感生电压有可能激发闩锁而烧毁局部电路。其余与纯输入时加压测量情况一样。

三态高阻输出时管脚对电源及对地都是高阻。电位与管脚版图、前一时刻的状态等有关系,不好确定。管脚节点电容很小,充放电很快。所以对于高阻态管脚,可以认为接触什么电位就是什么电位,犹如孤立导体。这正是总线的需求。可见,高阻态时直接施电压测量电流就行了。

3.1.3 加压测流时电压源与待测器件的关系

加压时恒压的产生和保持为稳压器原理。待测两端管脚开路时的电压即为所加的恒压。恒压下电流最大值Imax由稳压模块的耗散功率、电压变化系数等确定。

将Imax对应的最小负载电阻称为Rmin。负载可为开路~Rmin~短接。在Rmin~短接区间,过流保护机构起作用,无电流输出,ATE安全。但负载在开路~Rmin之间产生的电流有可能使器件过流。

正常情况下,加压测流的电压电流都在已知范围,宽泛的电流箝位设限不会有问题。但对于不熟悉的器件或失效件要特别注意设限,以免出现测试损坏或损坏加剧情况。在怀疑ATE箝位响应时,建议在测试适配器上也采取限制措施。

3.2 加流测压电流路径

3.2.1 普通管脚加流测压电流路径

加流测压就是给管脚与地或管脚与电源之间加规定的电流来测量这两端的电压。主要用于输入管脚的连通性测试、箝位电压测试以及输出管脚的高低电平(Voh、Vol)测试。管脚间在相应的电流流向时是低阻状态。如连通和箝位电压测试时测的是管脚与电源地之间的等效二极管的正向电压,是小电阻,在Voh、Vol测试时管脚对电源、对地分别是MOS管的开通小电阻。即加流测压其实是给低阻两端管脚加电流测其电压。

若要恒流则要有合适的条件。普通有低阻通路的输入输出管脚没问题。但若是高阻或截止态就不一样了。

3.2.2 高阻管脚加流测压电流路径

下面从器件及测试设备两方面分析在高阻状态下加流测压会出现什么情况。

器件层面,高阻情况的出现有主要有两种情况:

1)有电阻网络的接口,管脚对地、对电源有几K到几十K欧姆的电阻;

2)三态输出管脚的高阻态,上电偏置后,管脚对电源及地均为高阻。

其它情况属于误用如:二极管用成了反向、开路损坏管脚当正常管脚等。

加流测压时DUT的状态可用图3所示的压控电流源说明[4]。图2中,在控制输入Vin确定后,负载(DUT)电阻在一定范围变化时,可保持恒流。在饱和区,调整管MP2(缓冲器)内阻变化范围较宽,所以负载电阻在一定范围变化时可恒流。而在线性区,调整管内阻变化很小,最大电流由晶体管饱和压降及外部负载而定,不能恒流了。

大电阻或开路负载上的最大电压接近调整管外接电压,即接近电源电压V+。这可用串联电阻分压来解释,也可用晶体管饱和压降来解释。

在ATE用动态电子负载作为DUT高阻输出态的负载时,因为动态电子负载也是恒流源控制结构,所以情况与PMU类似,即有可能给高阻输出端加了一个接近电源电压的高电压。

图3 一种压控电流源原理图

可见在FIMV方式测试集成电路高阻状态时,电流基本为0,不管设置的电流有多少都是无意义的,而管脚有可能要承受高过器件电源Vdd-IO至PMU电源电压之间的电压。ATE设置的保护电压是否能及时启动及有效保护就成为了关键问题。但一般都没有明确答案。虽然ATE用的是高速电子部件,但从ATE限压反馈路径复杂考虑,反馈控制仍然需要一定时间。在此短时间段内,待测电路可能已经受到了一个比箝位电压高的电压脉冲的冲击。电流源提供的电流越大,DUT管脚升压时间越短或越陡,在同样时间内达到的电压脉冲会更高。可见,如设置的电压限高则器件将肯定会受到测试高压的冲击,如设的电压限低,则器件有可能也会受到测试高压脉冲的冲击。如果这些脉冲电压小于PN结反向击穿电压、MOS管的穿通电压或栅击穿电压,则对器件没影响,如超过这些电压则效应累积后应有影响。

3.2.3 高阻管脚电压传播

如果是图1所示结构,有正向二极管与电源相连。加流测压时,此高阻态管脚的高压会传递到电源Vdd-IO,从而对与Vdd-IO直接相连的外围结构构成影响。考虑到布线及其它结构的阻容分布参数,从传输路径来说,最靠近三态高阻输出的结构的瞬态电位最高,最容易受到影响。因此MP1和MN1的驱动级CMOS最容易受到影响,也就是此位置其瞬态电位最高。尤其是MN1驱动级CMOS的PMOS由于截止且路径最短最容易受漏源击穿影响。击穿机理应为PN结击穿、源漏穿通或其次级效应导致的界面陷阱或表面态的增加中的一种或其组合。而累积效应都可产生MOS管导通通路形成电阻。

如果驱动级PMOS管漏源之间的栅区由于光刻版原因变窄或有凹陷,则会造成PMOS栅局部沟道变窄并产生低压穿通、局部电场集中、界面陷阱或表面态的增加等次级效应而形成电阻。故栅有瑕疵的驱动级PMOS更容易受到高电压冲击的影响。

由于漏电测试是周期性的动态测试,单次作用持续时间有限。如果激励的次数很多,效应的不断积累,一定次数后将引起薄弱环节的率先磨损失效,这符合半导体器件的失效分布规律[5]。所以器件还能承受若干次的冲击,并不会开始就失效。

我们可以推论,如果与Vdd-IO相连的其它MOS结构或其它结构有缺陷,可能也会及早暴露。如果缺陷不明显,在相同的应力下,应能持续很长时间才会失效,提高应力则失效时间缩短。后一种结果已得到了试验验证。

4 小结

本文从I/O输出结构解释了高阻输出态,从全芯片ESD防护需求解释了集成电路管脚间为等效二极管关系。从测试设备的PMU出发,说明在集成电路测试过程中,如果防护设置不当或考虑不周密,加压测流有可能引起过电流损坏,加流测压有可能引起过电压损坏。

最好不要进行大电阻或高阻态的加流测试,或施加动态电子负载,因为有可能给器件加了高应力。只要出现过电应力,即使单次应力很小、时间很短,累积效应仍可导致失效。

按器件规范去使用、测试,按器件规范去检查各种未表现在规范上的值但可容易推算的值,则试验应该不会出问题。

[1] 刘艳艳,耿卫东,代永平,等. CMOS数字集成电路I/O单元设计分析[J].南开大学学报(自然科学版), 2008.41(1).

[2] A.Amerasekera, C.Duvvury. ESD in Silicon Integrated Circuits,(2nd edition) [M]. England: John Wiley & Sons, Ltd., 2002.

[3]时万春.现代集成电路测试技术[M].北京:化学工业出版社,2005.12.

[4] 王凌伟,王永国,秦冲.高精度宽范围数控电流源模块设计[J].信息通信, 2016,(4):102-103.

[5] JEP 122G, Failure Mechanisms and Models for Semiconductor Devices [S].

Interaction of Test Process and Pin Structure

LI Xing-hong, ZHAO Jun-ping, WANG Yomg, FANG Ce-bao, HUANG Xin

(Beijing Microelectronics Technology Institute ,Beijing 100076)

Based on the I / O structure of digital CMOS integrated circuit, the whole ESD protection structure, the PMU of automatic test equipment, and the principle of constant current source of constant voltage source, this paper comprehensively analyzed the interaction between the pressure flow measurement and the flow pressure measurement and the IC input, output, triplet and bidirectional pins in the process of function and PMU test process.

CMOS IC; PMU; test process; pin; interaction

TN43.2

A

1004-7204(2017)05-0058-04

李兴鸿,研究员,航天大规模和超大规模集成电路检测和失效分析中心副主任,北京微电子技术研究所封装测试中心总工程师,毕业于华南理工大学半导体物理与器件专业。