基于74LS160的可控多进制计数系统设计与仿真

2017-11-08季丽琴

摘要:本文在普通计数器设计原理的基础上,利用集成同步加法计数器74LS160设计出一个可控的多进制计数系统。利用拨码控制电路,该系统可以分别实现7进制、9进制和79进制计数功能,从而体现出该系统的可控性、灵活性和实用性。本文借助Multisim10平台进行了仿真测试,验证了该系统的可行性。

关键词: 74LS160; 计数器; Multisim

中图分类号: TP391

文献标志码: A

文章编号: 2095-2163(2017)05-0133-05

Abstract: In this paper, a controllable multilevel counting system is designed by 74LS160, which is based on the design principle of the common counter. By using the code control circuit, this system can realize the functions of level 7, 9 and 79, respectively. Thus, this system is controlled, flexible and practical. This paper uses the Multisim10 platform to realize the simulation and test, and the result shows that the system is feasible.

Keywords: 74LS160; counter; Multisim

0引言

74LS160[1-2]为集成同步十进制加法计数器,设计上具有同步置数控制端LOAD〖TX-〗、异步置零控制端CLR〖TX-〗、1个时钟脉冲输入端CLK〖TX-〗、2个计数控制端ENT和ENP、4个并行数据输入端A~D(D为输入最高位,A为输入最低位)、4个输出端QDQCQBQA(QD为输出最高位,QA为输出最低位)及1个进位输出端RCO。利用其同步置数控制端和异步置零控制端,可以实现不同进制的加法计数器。

基于74LS160的计数特性,本文研发提出了一个可控的多进制加法计数器系统。该系统采用同步置数法分别设计得到7进制、9进制、79进制加法计数器,再利用拨码控制电路,建立了不同进制计数器之间的灵活切换,从而有效保证了本系统的可控性、灵活性和实用性。为了验证该计数系统的可行性,本文利用Multisim 10[3-9]软件平台定制展开了仿真测试。实验结果表明,该系统运行稳定、正常。

1可控多进制计数系统的设计方案

1.1功能要求

1)用开关自由切换3种进制的计数状态:7进制、9进制、79进制。

2)数码管显示计数状态。

3)计数脉冲由外部提供。

1.2系统原理图

系统原理呈现如图1所示。由图1中可以看出,拨码控制电路能实现对7、9、79进制计数电路的切换,并通过数码显示电路可直观验证计数的正确性。综上可知,拨码控制电路的运行与控制对整个计数系统的部署实现具有至关重要的意义与作用。

[PS季丽琴1.EPS;S*2;X*2,BP#]

[ST6HZ][WT6HZ][JZ]图1系统设计原理图

[JZ]Fig. 1The design schematic diagram of the system

[HT5”SS][ST5”BZ][WT5”BZ]

2可控多进制计数系统的设计及仿真

2.17进制计数电路

7进制计数电路的计数状态为0~6,因此,利用同步置数法求出S6的代码为0110,又因该4位代码从左至右分别对应74LS160的4位输出端QD、QC、QB、QA,从代码可知QD、QA的电平为低,QC、QB的电平为高,所以得到反馈置数函数为LOAD〖TX-〗=QC·QB〖TX-〗,进而可得主控连接线路如图2所示。

因反馈置数函数为二输入与非门,对此,研究中选用了74LS00(内含4组二输入与非门)来生成反馈。时钟脉冲源选择的是100 Hz、5 V的方波信号,数据输入端A~D均接地(GND),数码显示电路选择DCD_HEX。仿真结果表明,该7进制计数电路运行正常。

2.29进制计数电路

9进制计数电路的计数状态为0~8,与7进制计数电路设计原理、方法类似,唯一的区别在于,S8的代码为1 000,即使得反馈置数函数为LOAD〖TX-〗=QD〖TX-〗。由此,本文采用74LS04(单输入非门)来获得反馈,最终的电路接线则如图3所示。

2.379进制计数电路

79进制计数电路的计数状态为0~78。该电路采用级联法完成,就是将2片74LS160进行级联,利用同步置数法求出反馈置数函数为LOAD〖TX-〗=QC′QB′QA′QD〖TX-〗,其中QC′、QB′、QA′分别为高位片74LS160的输出端(高位片用来显示十位上的数字),QD为低位片74LS160的输出端之一(低位片用来显示个位上的数字)。因反馈函数为4输入与非,具体到本文将采用4输入与非门74LS20来实现反馈。该计数电路连接即如图4所示。[FL)]

2.4可控的7、9、79进制计数系统

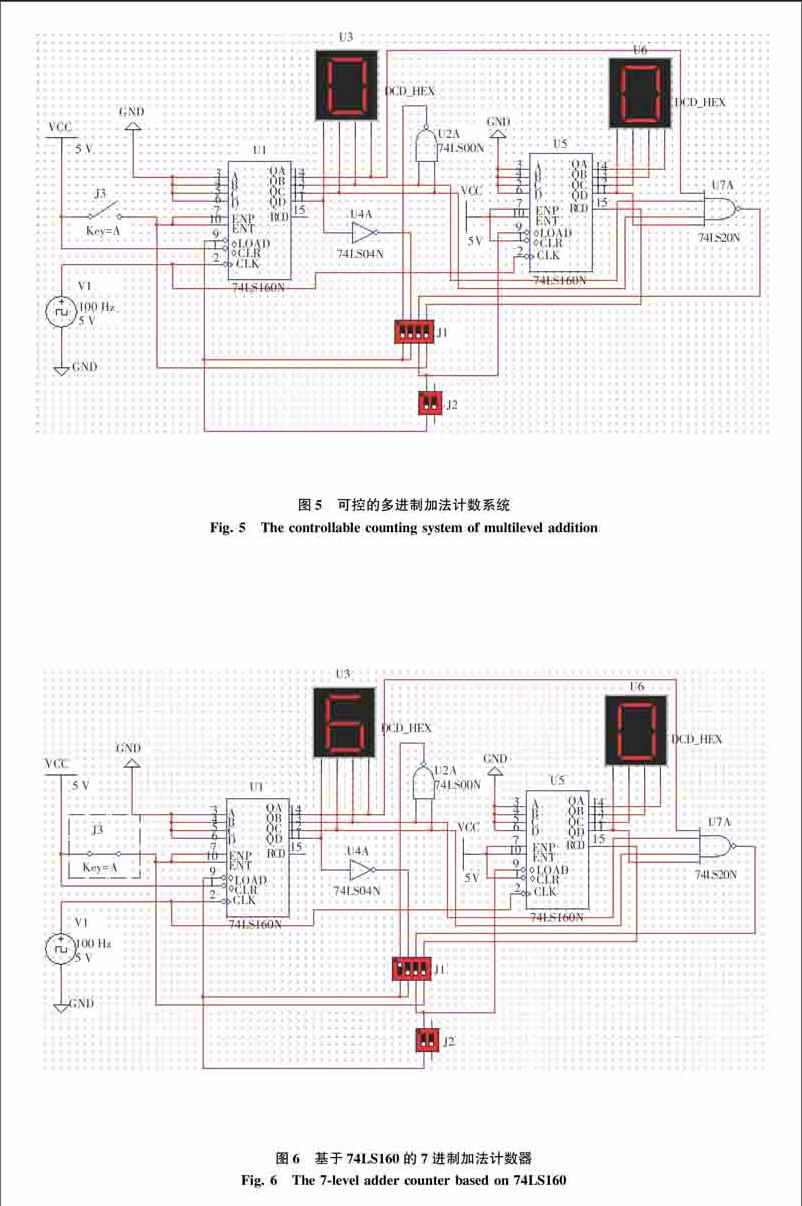

将图2、图3和图4综合起来,便可构成可控的多进制加法计数系统,如图5所示。从图中可看出,增加了一个拨码控制电路。该控制电路由一个4路拨码开关J1、一个2路拨码开关J2及一个按键开关J3组成。若闭合J3,且将J1、J2按图6进行设置,则可实现7进制计数。若闭合J3,且将J1、J2按图7进行设置,则可实现9进制计数。若断开J3,且将J1、J2按图8进行设置,则可实现79进制计数。

3结束语

本文提出的可控多进制计数系统是基于74LS160集成同步加法计数器之上展开设计的。利用拨码控制电路,可配置对7、9、79进制计数器的切换,利用数码显示电路检验系统的准确性。整个系统的仿真测试是借助Multim 10来提供操作控制的。测试结果表明,本文设计的可控多进制计数系统运行正常、稳定,具备可控性、灵活性和实用性。该系统不仅可以实现7、9、79进制计数,也可以通过修改反馈置数函数获得其它不同进制计数的切换。

闫石. 数字电子技术基础[M]. 北京:高等教育出版社,2006.

[2] 程勇,方元春. 数字电子技术基础[M]. 北京: 北京邮电大学出版社,2013.

[3] 黄培根,任清褒. Multisim10计算机虚拟仿真实验室[M]. 北京: 电子工业出版社,2008.

[4] 王冠华. Multisim10電路设计及应用[M]. 北京: 国防工业出版社,2008.

[5] 郭丽颖. 基于Multisim的彩灯循环闪烁电路设计与仿真[J]. 实验室研究与探索,2010,29(7):187-189.

[6] 马敬敏. 集成计数器74LS161的Multisim仿真[J]. 现代电子技术,2011,34(2):166-167,170.

[7] 刘文武. 基于Multisim 10的16路竞赛抢答器设计与仿真[J]. 现代电子技术,2011,34(23):178-181.

[8] 宋瑾. 基于Multisim 10的8路彩灯控制系统设计与仿真[J]. 电子设计工程, 2014,22(7):113-116.

[9] 任骏原. 74LS161异步置零法构成任意进制计数器的Multisim仿真[J]. 电子设计工程, 2011,19(14):135-137.endprint