基于FPGA的多通道采集传输模块的设计

2017-11-07董卫珍衡总张磊磊

文/董卫珍 衡总 张磊磊

基于FPGA的多通道采集传输模块的设计

文/董卫珍 衡总 张磊磊

由于多通道体制的声纳具有高信噪比和高精度等特性,它已经成为当前声纳的主流。因此,多通道信号的实时、高效采集尤为关键。本文提出了一种基于FPGA的多通道声纳采集模块,它利用FPGA产生AD芯片的控制信号,并将采集到的串行数据转换为并行数据,最后将采集到的数据传至信号预处理模块。该设计具有高精度、低噪的特点,可同时对多路信号进行AD采集、处理和传输,采集数据有效位数达12bit,采样频率可达240Ksps。

FPGA AD7690 采集

1 引言

对于多通道采集系统来说,其模数转换的多路扩展性、实时性和高精度决定着采集系统的性能。一般的信号采集系统中,常采用单片机或DSP对AD转换进行控制,单片机一般用于低速数据的转换中,且接口单一,灵活性差;DSP以其高速处理、强大而又灵活的接口和通信能力已应用于许多实际系统,但是DSP易受干扰。

FPGA具有硬件可定制的特点,所有功能利用硬件实现,能够有效克服单片机和DSP的缺点。FPGA的时钟频率高、内部延时小、编程配置灵活等特点,使其可以集采样控制、处理、缓存和传输于一个芯片内实现片上系统,从而大大提高系统的可靠性,降低了系统成本。因此,基于FPGA进行AD采集的设计已成为了近些年的主流方向。

2 系统整体架构及器件选型

2.1 系统整体框图

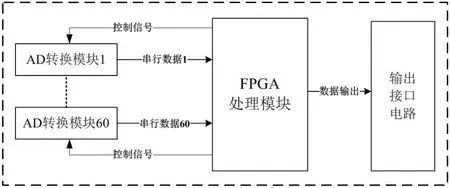

多通道采集模块实现对60路模拟信号的同步采集和数据转换及传输。它主要由三部分组成,包括60路Ad转换模块、FPGA处理模块和输出接口模块。其中:FPGA主要产生AD芯片工作的控制信号,进行数据串并转化的处理;AD转换电路是将输入的模拟信号进行采集、量化转换到数字域,转换后的数据送入FPGA进行相应的处理;输出接口电路负责将处理后数据传至信号处理板进行进一步处理。多通道采集模块的整体框图如图1所示。

图1:多通道采集模块的整体框图

2.2 器件选型

多通道采集模块的FPGA芯片选用的是Xilinx公司Virtex系列的XC5VLX50T,它包含 28800个CLBs,480个I/O,2160kb BlockRam,48个DSP48E Slice;AD芯片选用的是AD7690,它是一款18位、逐次逼近型模数转换器(ADC),它的最高采样速率可达400Ksps,从而满足项目240Ksps的采样速率要求。

AD7690内置一个低功耗、高速、18位不失码的采样ADC、一个内部转换时钟和一个多功能串行接口,在CNV上升沿、AD7690对IN+与IN-引脚之间的电压差进行采样。这两个引脚上的电压摆幅为0V到REF,相位相反。基准电压(REF)由外部提供,最高可以设置为电源电压。

由于AD7690是采用差分输入的方式,所以需要对输入信号进行单端转差分。本设计中的单端转差分转换器选用的是ADA4941-1,该芯片是一款低功耗、低噪声差分驱动器。它具有宽输入电压范围(当采用5V单电源时,可达0V至3.9V)、轨到轨输出、高输入阻抗和用户可调增益,非常适合驱动AD7690。

2.3 AD7690的工作时序

AD7690芯片的控制信号不是特别复杂,具体控制信号的时序要求如图2所示。其中信号的逻辑功能为:

图2:AD7690的工作时序

图3:AD控制模块的仿真波形图

(1)CNV 转换输入。此输入有多项功能:在它的上升沿,它启动转换过程并选择该部分的接口模式(链路或者片选)。当处于片选模式时,SDO管脚在CNV为低电平时有效;当处于链路模式时,数据只有在CNV为高电平时才可以进行读取。

(2)SCK串行时钟,逻辑输入。串行时钟输入提供用于访问AD7690 中的数据的串行时钟。此时钟也用作转换过程的时钟源。

(3)SDO 串行数据输出。转换数据以串行数据流的方式输出到该管脚,并且输出数据与SCK同步。

3 系统逻辑功能设计

系统的逻辑功能设计主要实现对AD芯片的控制,将采集数据进行串并转换,并将数据进行缓存和传输等功能。下面将对各部分逻辑功能进行详细介绍。

3.1 AD控制模块设计

本设计中,AD7690的接口方式采用的是片选模式,即在CNV为低电平时才可以进行数据的读取。由于芯片的数据转换时间为(0.5~2.1us),本设计中设置CNV的高电平持续时间大于2.1us,确保采集数据的正确。

控制模块的工作流程为:当接收到同步信号sys_start后,计数器cnt_cnv开始计数,计数周期为500个120MHz时钟;在cnt_cnv为1~265时,将CNV信号置高(保证大于2.1us);在cnt_cnv为266~480时,给出串行时钟SCK(选用12MHz)。该模块的仿真波形图见图3。

3.2 AD数据处理模块

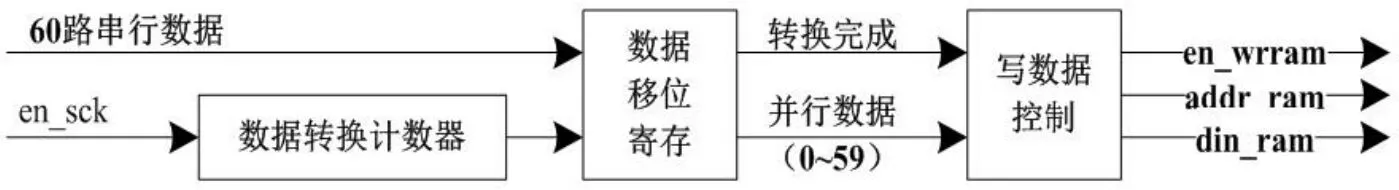

模拟信号经AD7690转换后得到的是串行数据,而信号处理需要的是并行数据,所以需要将64路信号进行串并转换。AD数据处理模块就是将60路数据信号进行串并转换,并将数据传入后端的数据缓存模块,该模块的逻辑框图如图4。

图4:AD数据处理模块的流程图

以第一通道为例,描述下具体实现方式:

(1)在en_sck为高期间,派生以一个计数器cnt_rdad0,同时对接收到的串行数据进行移位寄存,当计数器计到18时,将移位寄存器ad_ram0的值取出,该值din_db0即为当前通道的串并转换得到的位宽18bit的采样数据,该数值仅在每次转换结束后才改变(保持一个采样周期);

(2)当AD数据读取和串并转换(en_ db)完成后:首先派生一个计数器en_cnt_ wr,将60路数据分别写入不同的地址addr_ ram,当60路数据写操作结束时,将写使能信号en_wrram拉底。

3.3 采集数据的缓存

缓存AD数据模块的功能是将AD采集数据存入RAM,并在要求读取数据时,及时将数据读出。该设计中开辟了一个128×18bit的RAM,采取乒乓存储的方式,以保证读写数据不冲突。其具体实现方式:

(1)派生了一个标志信号ping_pang,该标志在每次同步信号到来时,发生改变;同时利用ping_pang和ad_data模块传来的地址信号addr_ram,作为写入缓存RAM的地址,实现当数据写进地址(0~59)时,读取地址(64~123)的数据,反之亦然。

(2)当发送模块传来的读数据使能信号en_ram为高时,派生出一个读数据计数器cnt_rdram,用于进行缓存RAM中数据的读取。读取的数据采用LVDS--Low Voltage Differential Signal模式传输至信号处理板,进行进一步的处理,图5为数据缓存模块的仿真波形图。

图5:数据缓存模块波形图

4 基于硬件开发环境下的程序下载验证

在ISE软件环境下进行综合、布局布线后,首先将程序下载到多通道采集模块的硬件中;输入模拟信号正弦波,使用在线逻辑分析仪ChipScope抓取串并转换后的AD采集结果;AD采集结果画图后如图6所示,可以看出采集模块的数据采集功能是正常的。

图6:串并转换后的采集数据

5 结论

本文通过FPGA来实现对AD7690的时序控制和数据传输,实现了对60路数据的同步采集。文中给出了系统部分功能的仿真,验证了FPGA内部逻辑程序的正确性;程序在线下载的测试结果,也验证了采集模块的工作正常。通过仿真和测试结果,可以看出系统的正确性和合理性,该设计已应用于实际项目当中。

[1]杨大伟,杨秀芳,李大伟等.基于FPGA的高速串行AD转换器控制设计与实验研究[J].西安理工大学学报,2014(03):91-95.

[2]刘新玮,韩巍,张泳等.基于FPGA的多通道AD同步采集卡设计[J].工程与试验,2013(53):75-77.

[3]郭云飞,赵冬娥,张斌等.基于FPGA的高速AD采集设计[J].山西电子技术,2013(05):37-39.

[4]黄容兰.基于FPGA的A/D转换采集控制模块设计[J].数据采集与处理,2009(10):237-240.

[5]何永泰.基于FPGA的多路A/D转换控制接口设计[J].电子测量技术,2006(29):78-80.

[6]赵吉成,王智勇.xilinx FPGA设计与实践教程[M].西安:西安电子科技大学出版社,2012:26-40.

[7]田耘,徐文波.xilinx FPGA开发实用教程[M].北京:清华大学出版社,2008:295-316.

作者单位上海船舶电子设备研究所 上海市 201108