高速PCM信号解码电路设计

2017-11-07衡总董卫珍

文/衡总 董卫珍

高速PCM信号解码电路设计

文/衡总 董卫珍

为了准确接收解码某系统的高速PCM数据,设计以PLL方式的时钟、数据恢复电路(CDR),实现硬件时钟同步、码同步, 并进行串并转换完成对高速PCM 码的解调。该电路对高速NRZI串行信号完成均衡后,转换为高速ECL电平逻辑,利用延时异或运算提取时钟信息,由PLL完成时钟提取与数据对齐。电路测试表明该方法能够有效地利用已有串行数据流产生具备合适相位的同步采样时钟信号,电路设计已用于某设备, 具有工作稳定, 抗干扰能力强的特点。

PCM CDR PLL 延时异或

某型系统采用同轴电缆同时完成高压直流供电与传输数据,数据上行传输采用高速PCM串行模式,实现湿端多通道AD采样数据与湿端设备运行状态等数据的混合上传。PCM编码的主要特征为:输出码型为不归零码(NRZI)。则干端接收模块可以根据PCM码流特征设计时钟数据恢复电路(CDR),提取出接收时钟与数据信号,在FPGA内完成PCM数据采样和串并转换。PCM解码的关键是时钟相位与数据码流的对齐。时钟信号的同步可以有两种模式:主模式和从模式。主模式由主控设备提供时钟,对于长距离单芯电力线通信而言不适用。在时钟同步采用从模式设计方式时,芯片需要从接收到的串行数据流中提取时钟信号以便正确可靠地进行串行数据流接收。

针对这个问题,文中介绍了一种从串行PCM 数据流中提取同步时钟的方法。

1 PCM传输总体结构

PCM通信模型如图1所示:湿端与干端通过同轴电缆相连,干端提供高压直流电源和下行的低频控制信号,湿端使用高频PCM上传关键数据。湿端包括PCM编码与预加重电路,通过变压器耦合到高压直流线缆上传;干端接收电路对线缆上的信号,去除高压直流,耦合得到高速串行信号,完成均衡预处理和信号电平转换,送到CDR电路完成时钟提取与数据相位同步,由FPGA完成数据采集与串并转换。

当数据流在单芯线缆中传输时,并没有附带时钟,数据接收端需要通过CDR从接收到的含有较大干扰和抖动的数字信号中提取接收位同步时钟,如图2所示,并用这个时钟对该数据信号重新采样,恢复出具有规范波形的原数据信号。因此CDR的基本目的是判别所读的数据的最佳时钟相位并采样。锁相环(PLL)是相位和频率跟踪的最有效的方法之一,专用高速时钟数据恢复电路的结构一般是基于PLL。

PCM信号解调的关键是利用PLL完成数据时钟提取和数据位对齐。

图1:供电与传输结构图

图2:时钟恢复示意图

2 CDR电路工作原理

目前,时钟恢复电路主要有两种设计方案:无源滤波器型(开环型)和有源滤波器型(闭环、PLL)。无源滤波器型结构如图3(a)所示,由时钟信息提取电路、高Q值滤波器和限幅放大器组成。有源滤波器型结构如图3(b)所示,由时钟信息提取电路、鉴相器、滤波器和压控振荡器组成。无源滤波器型的结构相对简单,但需要高Q值的滤波器。有源滤波器型一般采用PLL作为滤波器。由于数据传输为连续模式而非突发模式,数据时钟跟踪后变化不大,且数据速率相对不高,跟踪保持后数据率变化不大,则本设计使用PLL实现串行时钟提取。

图3:无源时钟提取电路和闭环时钟提取电路

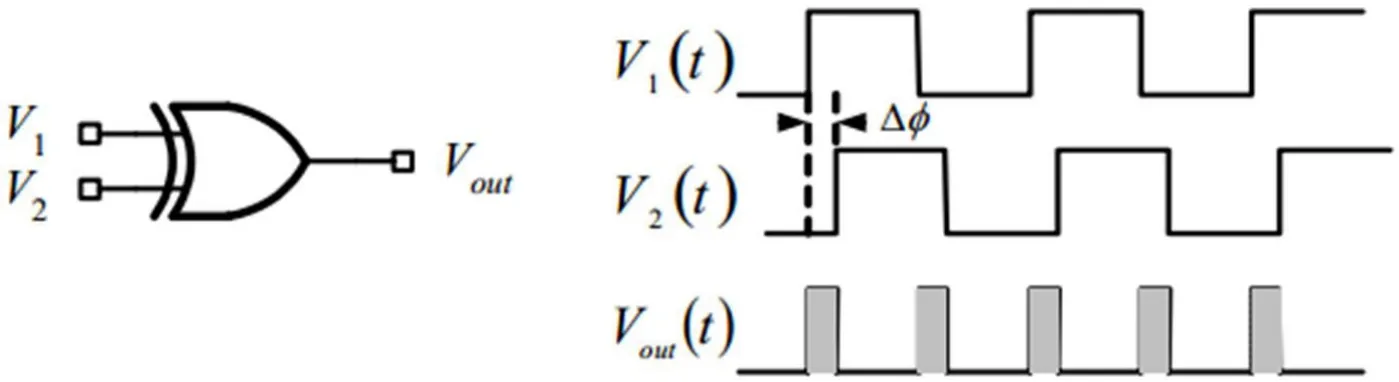

时钟信息提取的目标是检测输入数据的时钟信息,转变为频谱符合要求的信号。时钟信息的提取与输入数据的格式有关,双极性非归零数据信号(NRZI)功率谱中不包含比特率整数倍的频率分量,也不包含除直流以外的离散频谱分量,其时钟信息包含在电平跃变当中。因此,时钟信息提取电路的任务是检测电平跃变,产生一个幅度尽可能高的频谱分量部分。

延时单元结合异或逻辑的结构可以检测出数据的边沿跳变。当延时单元的时延等于四分之一单位比特数据通过所需时间时,产生的频谱分量最大。如图4所示,对输入PCM数据流经过专用延时ASIC:1519-20B延时,延时信号与原参考信号经过高速异或芯片MC10107,提取出信号的边沿变化,即时钟信息,该时钟信号作为PLL输入参考时钟,提取时钟信息。

图4:时钟信息提取电路与相关节点波形

图5:PLL基本结构

3 PLL电路结构

本设计以PLL电路实现时钟提取,PLL是具有固定的结构,如图5所示,包括鉴相器(PD)、环路滤波(LF)、压控振荡器(VCO)。

鉴相器输入信号为延时异或逻辑提取得到的数据流边沿变化时钟与VCO输出信号。异或逻辑输出信号如图4所示,提供了所有边沿变化信息,即时钟信息。

鉴相器是一个时序逻辑,最经典的是三态状态机鉴相,比较出相位超前与滞后关系,本设计使用MC12040 鉴相器,逻辑实现方式为SR触发器,采用ECL电平逻辑,适应高速应用场合,信号逻辑如图6所示,比较出信号相位的超前、滞后关系。

鉴相器输出利用高速差分电路进行电平搬移,送到低通滤波,去除高频分量,保留直流分量。

压控振荡器VCO则采用经典款MC1648实现,配合MC12040 的ECL逻辑设计。

图6:鉴相器结构与输入输出逻辑

4 电路实验测试结果

实验测试时,湿端处于空闲状态,AD采集关闭,外围采集设备关闭,设备状态稳定可控,上传数据为一组固定帧结构的 PCM 数据流。数据流送到CDR电路完成数据时钟提取与数据采集。接收前端耦合到的串行信号与均衡后数据波形如图7所示,完成对串行数据的整形。

图7:串行数据均衡前后波形

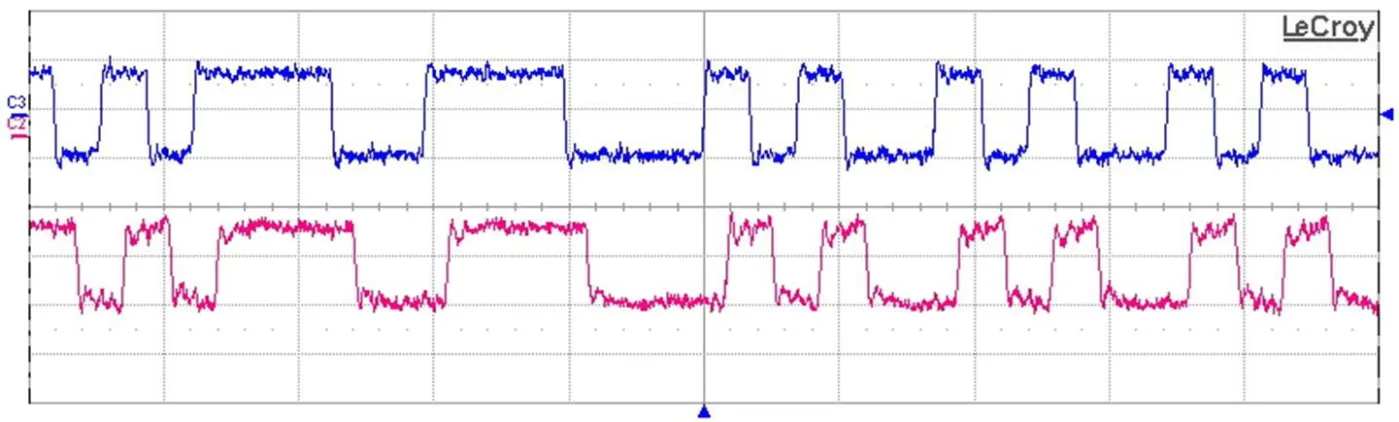

均衡后数据完成逻辑电平转换,对数据延时,延时前后数据波形如图8所示。

图8:串行数据经过1519-20B延时前后波形

经过PLL时钟跟踪锁定后,最终的PCM_CLK和相位对应的PCM_DATA,时钟与数据相位对齐,如图9所示。

图9:PCM解调后数据时钟与数据相位

测试时模拟输入8个连零或连一时, 电路也能够提取出较好的时钟信息分量。

5 结论

本文所设计PCM解码电路,利用PLL完成CDR功能,实现数据时钟提取与数据相位对齐,实现数据提取。经过实际测试,电路工作稳定,抗误码能力强,可根据实际情况灵活配置参数,根据以上特点,该设计对于远程通信设备具有很大的参考价值。

(通讯作者:衡总)

[1]王煜,文开章,汪为伟.PCM串行数据流同步时钟提取设计[J].现代电子技术,2010,23(334):192-194.

[2]Ching-Yuan Yang.PLL及應用-2004[M]. National Chung-Hsing University Department of Electrical Engineering.

[3]尹晶,曾列光.一种快速同步的时钟数据恢复电路的设计实现[J].光通信技术,2007(01):52-54.

[4]仇应华,王志功,朱恩.10Gb/s NRZ码时钟信息提取电路[J].固体电子学研究与进展,2005(03).

作者单位上海船舶电子设备研究所 上海市 201108

衡总(1989-),男,江苏省徐州市人。工程师。研究方向为FPGA信号处理。