基于原位等离子体氮化及低压化学气相沉积-Si3N4栅介质的高性能AlGaN/GaN MIS-HEMTs器件的研究∗

2017-10-23李淑萍张志利付凯于国浩蔡勇张宝顺

李淑萍 张志利 付凯 于国浩 蔡勇 张宝顺†

1)(苏州工业园区服务外包职业学院纳米科技学院,苏州 215123)

2)(中国科学院大学,苏州纳米技术与纳米仿生研究所,苏州 215123)

基于原位等离子体氮化及低压化学气相沉积-Si3N4栅介质的高性能AlGaN/GaN MIS-HEMTs器件的研究∗

李淑萍1)#张志利2)#付凯2)于国浩2)蔡勇2)张宝顺2)†

1)(苏州工业园区服务外包职业学院纳米科技学院,苏州 215123)

2)(中国科学院大学,苏州纳米技术与纳米仿生研究所,苏州 215123)

通过对低压化学气相沉积(LPCVD)系统进行改造,实现在沉积Si3N4薄膜前的原位等离子体氮化处理,氮等离子体可以有效地降低器件界面处的氧含量和悬挂键,从而获得了较低的LPCVD-Si3N4/GaN界面态,通过这种技术制作的MIS-HEMTs器件,在扫描栅压范围VG-sweep=(−30 V,+24 V)时,阈值回滞为186 mV,据我们所知为目前高扫描栅压VG+(>20 V)下的最好结果.动态测试表明,在400 V关态应力下,器件的导通电阻仅仅上升1.36倍(关态到开态的时间间隔为100µs).

氮化镓高电子迁移率晶体管,低压化学气相沉积,原位氮化

1 引 言

以GaN为代表的第三代半导体具有较宽的禁带宽度、高的击穿电场、化学稳定性强、电子迁移率高和极强的抗辐射能力等特点,在电力电子器件方面显示出良好的应用前景[1,2].与传统的Schottky-gate高电子迁移率晶体管(HEMT)相比,MIS-HEMTs器件具有更加突出的优势,因为栅介质的引入不仅可以降低器件的栅漏电,而且可以增加栅摆幅,提高器件的栅驱动能力[3].然而,栅介质的引入会产生新的介质/(Al)GaN界面态,从而带来新的挑战,如:阈值回滞、电流崩塌和器件的可靠性等问题[4,5].目前,通过一些技术手段可以使这些问题得到一定程度的缓解,如:栅介质优化[6]、表面化学处理[7]、原位等离子体氮化[8]等,并且通过这些手段获得了在低扫描栅压下(VG+<10 V)的低阈值回滞.但是,到目前为止,尚未见在高扫描栅压下(VG+>20 V)的低阈值回滞的报道.

另一方面,低压化学气相沉积(LPCVD)的氮化硅具有较高的薄膜质量、高的热稳定性及无等离子体诱导损伤等特点.在用作HMET器件的栅介质和钝化层方面具有较大的潜力和优势[2,9,10].

在这个工作中,我们通过对LPCVD系统进行改造,实现在沉积Si3N4薄膜前的原位等离子体氮化处理,降低了LPCVD-Si3N4/GaN的界面态密度,通过这种技术制作的MIS-HEMTs器件,在扫描栅压范围为VG-sweep=(−30 V,+24 V)时,阈值回滞为186 mV,击穿电压为881 V(衬底接地).动态测试表明,在400 V关态应力下,器件的导通电阻仅仅上升1.36倍(关态到开态的时间间隔为100µs).

2 器件的结构与制备

2.1 N2等离子体氮化提升界面态的物理机理

在之前的报道中指出,由于GaN暴露在空气中,表面会吸附氧原子或者形成一层非常薄的氧化层,这种表面的自然氧化物(GaOx)会增加介质与(Al)GaN的界面态密度[3],如图1所示,在界面处存在氧杂质和氮空位两种主要的缺陷态.高的界面态密度会对器件的性能产生严重影响,如:器件的电流崩塌效应、栅回滞效应和器件的可靠性等问题.

原位的等离子体处理可以降低表面的自然氧化物含量,从而提高界面质量.通过N2等离子体在合适的功率下对AlGaN/GaN HEMT器件表面进行处理,这种处理主要有两个作用:一是N2等离子体可以对(Al)GaN表面的N空位进行填充,减少表面的悬挂键;另外,在等离子体中的离子都具有一定的能量,这种能量可以对材料表面产生轰击的作用,所以,另一个作用是通过离子轰击,去除表面的氧原子,从而提高介质与(Al)GaN的界面质量[11].

图1 (网刊彩色)(Al)GaN与介质层界面的缺陷结构示意图Fig.1.(color online)The schematic diagram of(Al)GaN and dielectric layer interface defect structure.

2.2 器件制作

图2(a)展示了AlGaN/GaN MIS-HEMT器件的基本结构,AlGaN/GaN异质结材料通过金属氧化物化学气相沉积MOCVD的方式生长在Si(111)衬底上,结构从衬底到表面依次为4.1µm厚的GaN缓冲层、100 nm厚的GaN沟道层、1 nm AlN空间层、25 nm本征Al0.26Ga0.74N势垒层和2 nm厚的GaN盖帽层.通过霍尔测试表明,外延结构室温下电子迁移率为 1843 cm2·V−1·s−1,二维电子气浓度为1×1013cm−2.

对于器件的制作,首先在LPCVD系统中对样品采用原位等离子体处理,等离子处理的基本结构在图2(b)中给出.处理过程中维持炉管内的压强为300 mtorr,温度为400°C,等离子体功率为50 W处理3 min,然后将温度从400°C上升到780°C,进行LPCVD-Si3N4的沉积,氨气(NH3)和二氯二氢硅SiH2Cl2的流量分别为280 sccm和70 sccm,沉积速率大约为3.5 nm/min.沉积LPCVD-Si3N4之后光刻出源漏电极图形,然后使用SF6等离子体将源漏电极下端的Si3N4去除,接下来通过电子束蒸发沉积Ti/Al/Ni/Au(20 nm/130 nm/50 nm/150 nm)四层金属,剥离后在890°C退火30 s形成欧姆接触.

图2 (网刊彩色)(a)AlGaN/GaN MIS-HEMTs器件的基本结构示意图;(b)改造的LPCVD系统示意图Fig.2.(color online)(a)Schematic of AlGaN/GaN MIS-HEMTs device;(b)a reformed LPCVD system.

TLM测试接触电阻为1.6 Ω·mm.使用F离子进行器件隔离.沉积Ni/Au(50 nm/150 nm)剥离后形成栅电极.为了提高器件的动态特性,我们制作了场板结构,场板下介质层为300 nm厚的等离子体增强化学气相沉积(PECVD)SiNx,生长温度为350°C,场板向漏端和源端延展出的尺寸都为2µm,栅长和栅宽分别为4µm和100µm,栅到漏的距离为17µm,栅到源的距离为6µm.

3 实验结果与分析

3.1 X射线光电子能谱分析(XPS)表征界面质量

为了测试界面处元素含量,进行了XPS测试,XPS是用X射线去辐射样品,使原子或分子的内层电子或价电子受激发射出来.被光子激发出来的电子称为光电子,可以测量光电子的能量.以光电子的动能为横坐标、相对强度(脉冲/s)为纵坐标可做出光电子能谱图,从而获得待测物组成.所以,使用XPS技术可以有效获得界面处每种元素的含量,为分析N2等离子体表面处理技术提供理论支持.

通过测试能谱分析界面处的元素种类、元素含量和每一种元素的成键信息,如图3所示,对于经过N2等离子体处理和未经N2等离子体处理的两个样品,最明显的两个峰出现在Ga-N和Si-N的位置.为了获得其他成键情况,需要对测试的实验结果进行分峰拟合,发现在Ga-N峰附近存在Ga-O峰,在Si-N峰附近也存在明显的Si-O峰.通过对每种成键峰的积分得出结论:在经过N2等离子体处理后,界面处Ga-O峰降低了30%,Si-O峰降低了43%,说明N2等离子体处理的确可以降低GaN表面的自然氧化物,从而提高界面态的质量[12,13].

3.2 器件性能

图3 (网刊彩色)XPS分峰拟合曲线,Ga-O峰降低了30%,Si-O峰降低了43%Fig.3.(color online)The fi tting curves of XPS peak,Ga-O peak and Si-O peak has decreased by 30%and 43%,respectively.

图4 (网刊彩色)(a)经过原位等离子体处理的AlGaN/GaN MIS-HEMT器件典型的转移曲线;(b)在对数坐标系中不同正向扫描栅压下器件的转移曲线Fig.4.(color online)(a)Transfer curves of the AlGaN/GaN MIS-HEMT with in-situ pre-deposition plasma nitridation;(b)transfer curves of the device with di ff erent positive end of gate sweep voltages in log-scale.

图4(a)展示了LPCVD-Si3N4/GaN/AlGaN/GaN MIS-HEMTs器件典型的转移曲线,采用N2等离子体处理器件的最大饱和电流IDS-max和最大跨导Gm-max分别为513 mA/mm和64 mS/mm,基本与未经过等离子体处理的器件相同[10].器件的阈值电压为−23.6 V(阈值电压定义为漏电流为10µA/mm),一个更负的阈值电压可能是由于正的界面固定电荷或新的施主态产生,这个现象在文献[14]中也报道过.对于器件回滞∆Vth的评估,栅压从−30 V扫描到24 V然后再回扫回来,器件的阈值回滞∆Vth大约为186 mV(VG-sweep=(−30 V,+24 V)).据我们所知,这是目前在较大正向扫描栅压(VG+>20 V)下获得的最好的结果[5,15,16].图4(b)展示了在对数坐标系下不同正向扫描栅压的转移曲线,在不同正向栅压下,器件依然保持一个较小的阈值回滞,说明使用原位N2等离子处理可以有效提高器件的阈值稳定性.

图5 原位N2等离子体处理的MIS-HEMT器件在不同正向扫描栅压下的阈值回滞Fig.5.Summary of Vthof the samples with in-situ plasma nitridation versus positive end of gate sweep voltages VG+.

图5总结了器件在不同正向扫描栅压VG+下阈值回滞Vth的变化. 有两个明显特别的地方需要注意:一个是阈值回滞方向与之前文献报道中的回滞方向不同[17−20],阈值回滞是一个负值;另一个不同是对于经过等离子体处理过的器件,阈值回滞Vth随着正向扫描栅压VG+的增加而减小,而对于一般MIS-HEMT器件[17,20],由于界面处类受主界面态的影响,更正的扫描栅压导致更多的电子被俘获,从而阈值在回扫的过程中正向移动.对于经过等离子体处理的器件,阈值电压有一个轻微的负向移动,这主要是由于在负向栅压时,GaN中的缺陷俘获电子,在回扫过程中阈值负向移动[21],类似于上面的分析,越高的正向扫描栅压VG+导致阈值电压正向移动,但是由于界面质量的提高,正向移动的幅度要远小于未经过等离子处理的器件.综上所述,经过等离子体处理的器件阈值回滞是由于界面态密度的降低导致界面态俘获电荷数量下降,在一个较负的栅压下,GaN缓冲层中的缺陷作用相对明显,最终决定了器件阈值回滞的大小和方向.

AlGaN/GaN MIS-HEMT器件的输出特性如图6(a)所示,栅压扫描范围和漏压扫描范围分别为0 V到10 V和−24 V到−8 V.器件的开态电阻RON为10.3 Ω·mm@VGS=−8 V.最大饱和电流达到513 mA/mm.图6(b)展示了器件的击穿特性,在测试过程中,栅压保持在−24 V,衬底接地.在漏端电压小于400 V时,器件的漏电增加缓慢,当电压继续增加后,漏电明显增加,可能对应的是器件的缓冲层漏电,当电压达到881 V时,器件击穿.

图6 (网刊彩色)(a)AlGaN/GaN MIS-HEMT器件的转移特性曲线;(b)器件的击穿特性曲线,击穿电压测试中衬底接地Fig.6.(color online)(a)Output curves of AlGaN/GaN MIS-HEMT device;(b)OFF-state breakdown characteristics with the substrate grounded.

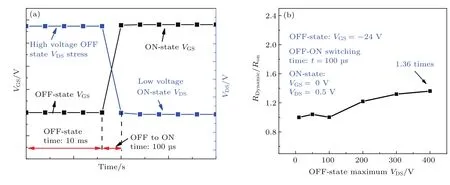

图7 (a)器件动态测试设置示意图;(b)归一化的动态电阻与漏端施加应力的关系Fig.7.(a)On-wafer transient switching characteristics of the MIS-HEMTs;(b)normalized dynamic Ronwith various values of o ff-state VDS.

最后,器件的电流崩塌效应通过Agilent的动态测试系统进行评估,开态设置为VGS=0 V和VDS=0.5 V,器件的关态时间为10 ms,开关间隔为100µs.图7(a)展示了动态测试的具体过程,首先对器件施加一个关态应力,利用栅压使器件处于关闭状态,漏端施加一个高压,电压范围从50 V到400 V.然后迅速将器件开启,开启后测量源漏之间的电阻,开启时间最短为100µs.如图7(b)所示,经过N2等离子体处理的器件的电流崩塌得到明显抑制,在400 V关态应力条件下,动态电阻仅仅上升了36%.

4 结 论

通过设备改造,在LPCVD系统里引入原位的等离子体处理装置,并且通过XPS测试对处理后的界面进行了测试分析,在经过N2等离子体处理后,界面处Ga-O峰降低了30%,Si-O峰降低了43%,说明N2等离子体处理的确可以降低GaN表面的自然氧化物,从而提高界面态的质量.并且基于原位N2等离子体处理技术,制作出了高性能的GaN MIS-HEMT器件,如阈值回滞∆Vth大约为186 mV(VG-sweep=(−30 V,+24 V))、击穿电压BV=881 V和400 V关态应力条件下动态电阻仅仅上升了36%,这些关键工艺的研究为制作增强型MIS-HEMT器件打下了坚实的基础.

[1]Yuan S,Duan B X,Yuan X N,Ma J C,Li C L,Cao Z,Guo H J,Yang Y T 2015Acta Phys.Sin.64 237302(in Chinese)[袁嵩,段宝兴,袁小宁,马建冲,李春来,曹震,郭海军,杨银堂2015物理学报64 237302]

[2]Hua M,Liu C,Yang S,Liu S,Fu K,Dong Z,Cai Y,Zhang B,Chen K J 2015IEEE Electron Dev.Lett.36 448

[3]Yang S,Tang Z K,Wong K Y,Lin Y S,Liu C,Lu Y Y,Huang S,Chen K J 2013IEEE Electron Dev.Lett.34 1497

[4]Xin T,Lu Y J,Gu G D,Wang L,Dun S B,Song X B,Guo H Y,Yin J Y,Cai S J,Feng Z H 2015J.Semicond.36 074008

[5]Hsieh T E,Chang E Y,Song Y Z,Lin Y C,Wang H C,Liu S C,Salahuddin S,Hu C C 2014IEEE Electron Dev.Lett.35 732

[6]Choi W,Ryu H,Jeon N,Lee M,Cha H Y,Seo K S 2014IEEE Electron Dev.Lett.35 30

[7]Chakroun A,Maher H,Al Alam E,Soui fiA,Aimez V,Ares R,Jaouad A 2014IEEE Electron Dev.Lett.35 318

[8]Liu S C,Chen B Y,Lin Y C,Hsieh T E,Wang H C,Chang E Y 2014IEEE Electron Dev.Lett.35 1001

[9]Zhang Z L,Qin S J,Fu K,Yu G H,Li W Y,Zhang X D,Sun S C,Song L,Li S M,Hao R H,Fan Y M,Sun Q,Pan G B,Cai Y,Zhang B S 2016Appl.Phys.Express9 084102

[10]Zhang Z L,Yu G H,Zhang X D,Deng X G,Li S M,Fan Y M,Sun S C,Song L,Tan S X,Wu D D,Li W Y,Huang W,Fu K,Cai Y,Sun Q,Zhang B S 2016IEEE Trans.Electron Dev.63 731

[11]Feng Q,Tian Y,Bi Z W,Yue Y Z,Ni J Y,Zhang J C,Hao Y,and Yang L A 2009Chin.Phys.B18 3014

[12]Edwards A P,Mittereder J A,Binari S C,Katzer D S,Storm D F,Roussos J A 2005IEEE Electron Dev.Lett.26 225

[13]Huang S,Jiang Q M,Yang S,Zhou C H,Chen K J 2012IEEE Electron Dev.Lett.33 516

[14]Reiner M,Lagger P,Prechtl G,Steinschifter P,et al.2015IEEE International Electron Devices MeetingWashington,Dec.7–9 2015,p35.5.1

[15]Liu S,Yu G H,Fu K,Tan S X,Zhang Z L,Zeng C H,Hou K Y,Huang W,Cai Y,Zhang B S,Yuan J S 2014Electron.Lett.50 1322

[16]Kanamura M,Ohki T,Ozaki S,Nishimori M,Tomabechi S,Kotani J,Miyajima T,Nakamura N,Okamoto N,Kikkawa T 2013Power Semiconductor Devices and ICs(ISPSD),2013 25th International Symposium onKanazawa,May 26–30,2013,pp411–414

[17]Xu Z,Wang J Y,Liu Y,Cai J B,Liu J Q,Wang M J,Yu M,Xie B,Wu W G,Ma X H,Zhang J C 2013IEEE Electron Dev.Lett.34 855

[18]Lanford W B,Tanaka T,Otoki Y,Adesida I 2005Electron.Lett.41 449

[19]Wu T L,Franco J,Marcon D,de Jaeger B,Bakeroot B,Sto ff els S,van Hove M,Groeseneken G,Decoutere S 2016IEEE Trans.Electron Dev.63 1853

[20]Huang S,Yang S,Roberts J,Chen K J 2011Jpn.J.Appl.Phys.50 0202

[21]Polyakov A Y,Smirnov N B,Govorkov A V,Markov A V,Dabiran A M,Wowchak A M,Osinsky A V,Cui B,Chow P P,Pearton S J 2007Appl.Phys.Lett.91 232116

High-performance AlGaN/GaN MIS-HEMT device based onin situplasma nitriding and low power chemical vapor deposition Si3N4gate dielectrics∗

Li Shu-Ping1)#Zhang Zhi-Li2)#Fu Kai2)Yu Guo-Hao2)Cai Yong2)Zhang Bao-Shun2)†

1)(Suzhou Industrial Park Institute of Services Outsourcing,Suzhou 215123,China)

2)(Suzhou Institute of Nano-Tech and Nano-Bionics,Chinese Academy of Sciences,Suzhou 215123,China)

Gallium nitride(GaN)-based high electron mobility transistor(HEMT)power devices have demonstrated great potential applications due to high current density,high switching speed,and low ON-resistance in comparison to the established silicon(Si)-based semiconductor devices.These superior characteristics make GaN HEMT a promising candidate for next-generation power converters.Many of the early GaN HEMTs are devices with Schottky gate,which su ff er a high gate leakage and a small gate swing.By inserting an insulator under gate metal,the MIS-HEMT is highly preferred over the Schottky-gate HEMT for high-voltage power switche,owing to the suppressed gate leakage and enlarged gate swing.However,the insertion of the gate dielectric creates an additional dielectric/(Al)GaN interface that presents some great challenges to AlGaN/GaN MIS-HEMT,such as the threshold voltage(Vth)hysteresis,current collapse and the reliability of the devices.It has been reported that the poor-quality native oxide(GaOx)is detrimental to the dielectric/(Al)GaN interface quality that accounted for theVthinstability issue in the GaN based device.Meanwhile,it has been proved that in-situ plasma pretreatment is capable of removing the surface native oxide.On the other hand,low power chemical vapor deposition(LPCVD)-Si3N4with free of plasma-induced damage,high fi lm quality,and high thermal stability,shows great potential applications and advantages as a choice for the GaN MIS-HEMTs gate dielectric and the passivation layer.

In this work,an in-situ pre-deposition plasma nitridation process is adopted to remove the native oxide and reduce surface dangling bonds prior to LPCVD-Si3N4deposition.The LPCVD-Si3N4/GaN/AlGaN/GaN MIS-HEMT with a high-quality LPCVD-Si3N4/GaN interface is demonstrated.The fabricated MIS-HEMT exhibits a very-lowVthhysteresis of 186 mV atVG-sweep=(−30 V,+24 V),a high breakdown voltage of 881 V,with the substrate grounded.The hysteresis of our device at a higher positive end of gate sweep voltage(VG+>20 V)is the best to our knowledge.Switched o ffafter an o ff-stateVDSstress of 400 V,the device has a dynamic on-resistanceRononly 36%larger than the staticRon.

GaN-based high electron mobility transistor,low pressure chemical vapor deposition,in-situpre-deposition plasma nitridation

24 April 2017;revised manuscript

10 July 2017)

(2017年4月24日收到;2017年7月10日收到修改稿)

10.7498/aps.66.197301

∗江苏省重点研发计划(批准号:BE2013002-2)、国家重点研发计划(批准号:2016YFC0801203)、江苏省重点研究与发展计划(批准号:BE2016084)、国家自然科学基金青年科学基金(批准号:11404372)和国家重点研发计划重大科学仪器设备开发专项(批准号:2013YQ470767)资助的课题.

#共同第一作者.

†通信作者.E-mail:Bszhang2006@sinano.ac.cn

©2017中国物理学会Chinese Physical Society

PACS:73.40.Kp,73.40.Vz

10.7498/aps.66.197301

*Project supported by the Key Technologies Support Program of Jiangsu Province,China(Grant No.BE2013002-2),The National Key Research and Development Program of China(Grant No.2016YFC0801203),the Key Research and Development Program of Jiangsu Province,China(Grant No.BE2016084),the National Natural Science Foundation of China(Grant No.11404372),and the National Key Scienti fi c Instrument and Equipment Development Projects of China(Grant No.2013YQ470767).

#These authors contributed equally.

†Corresponding author.E-mail:Bszhang2006@sinano.ac.cn