基于亚阈运算放大器的动态锁存比较器设计

2017-10-21张玲

张玲

[摘 要] 基于预放大锁存理论,提出一种低电压低功耗动态锁存比较器。与传统比较器不同,该比较器采用了亚阈运算放大器结构作为前置放大器以实现低电压低功耗。结果表明当工作于1.2V电源电压、500kHz的时钟下,精度可达1 mV,功耗仅为16.45 μW。该电路可应用在低功耗流水线式ADC电路中。

[关 键 词] 动态锁存比较器;前置放大器;亚阈运算放大器

[中图分类号] G712 [文献标志码] A [文章编号] 2096-0603(2017)13-0179-01

一、引言

随着现代通信技术的广泛应用,高速低功耗的电子设备成为市场主流,这些设备都依赖于高性能的模数转换器(ADC),特别是对功耗的要求越来越高,低功耗ADC成为决定设备性能的关键因素。而模数转换器中比较器是重要模块,其精度、功耗和速度等指标对整个ADC的性能有重要的影响[1]。

这里设计了一种新型低电压低功耗动态锁存比较器。与传统的比较器相比,由于采用亚阈运算放大器作为前置放大器,极大地降低了整个电路的功耗。

二、比较器的结构设计

为了实现电路的低功耗,使电路中的MOSFET工作在亚阈区[2]。比较器采用动态锁存结构,它由三级电路构成,第一级是前置放大器,第二級是动态锁存器,第三极是输出锁存器。原理框图如图1所示。

(一)前置放大器

前置放大器的作用有两个:一是放大输入信号,降低动态锁存器的比较时间,同时降低总体延时;二是放大输入信号差,减小比较器失调电压的影响。

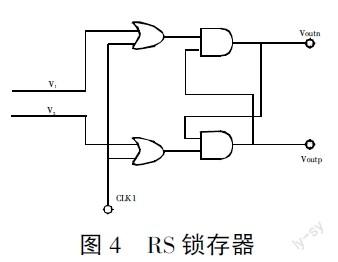

(二)动态锁存器

本次设计的锁存器采用动态锁存器结构。动态锁存器优于静态锁存器的特点是电路瞬间功耗低,直流功耗近乎为零,并且电路面积小,但动态锁存器需要时钟控制信号。图3為动态锁存器的原理图。

(三)输出锁存器

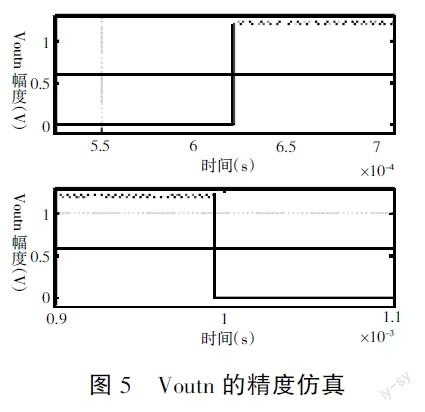

输出锁存器其实是一个带使能端的RS锁存器,其结构如图4所示。当使能端CLK1=0时,输出锁存器接收动态锁存器的输出结果;而当CLK1=1时,输出锁存器对当前输入状态进行锁存并输出。

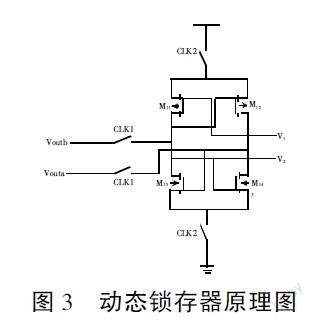

三、电路仿真

为了验证设计效果,利用Synopsys Hspice软件,在电源电压为1.2V下,采用TSMC 0.18μm工艺模型对上面设计的动态锁存比较器进行仿真。

四、结论

基于预放大锁存理论设计一种三级动态锁存比较器,每一级的电路结构简单,并且利用MOSFET亚阈区特性实现低电压、低功耗的要求。在TSMC 0.18μm CMOS工艺模型下,采用Synopsys Hspice对电路进行模拟,结果表明在500 kHz的时钟下,比较精度可达到1 mV,功耗为16.45 μW。该电路可以应用在低功耗流水线ADC电路中。

参考文献:

[1]黄智伟.低功耗系统设计:原理、器件与电路[M].北京:电子工业出版社,2011.

[2]段吉海,覃宇飞,潘磊.高速CMOS钟控比较器的设计[J].电子器件,2010(2):158-161.