基于FPGA+DSP架构的RapidIO总线的实现

2017-09-30范海峰叶兆阳

范海峰,叶兆阳

基于FPGA+DSP架构的RapidIO总线的实现

范海峰,叶兆阳

(南海舰队自动化站,广东湛江 524002)

RapidIO传输效率高、系统成本低、系统稳定性好,在高性能嵌入式系统中得到了广泛的应用。通过对RapidIO总线及其交换技术的深入研究,设计并实现了基于FPGA+DSP架构的RapidIO总线协议,为不同应用系统提供一个模块化的功能单元,解决了大部分熟悉Avalon接口而不熟悉RapidIO接口的FPGA用户的需求。在基于该架构的设计中,FPGA的功能主要是通过SOPC系统实现RapidIO协议处理,以及提供必须的硬件接口;DSP主要实现RapidIO协议的控制,以及提供对用户的逻辑接口。文章主要从软件方面对RapidIO接口实现方案进行了详尽的阐述。最后搭建实验平台对所实现的RapidIO总线进行了连通性测试,证明了此种方案的可行性。

RapidIO 嵌入式互连 FPGA DSP

0 引言

目前嵌入式总线的总体发展趋势是:串行接口取代并行接口,差分传输取代单端传输,点对点方式取代管道方式,交换结构取代共享总线结构[1]。在这种趋势下,新的总线不断推出,其中具有代表性的总线有:Hyper Transport[2]、PCI Express、InfiniBand、RapidIO等。各总线均有其优点和不足,应用在不同的实际应用中。其中RapidIO总线的设计目标是应用于系统内部互连[3]。RapidIO技术最初是由Motorola和Mereury Computer公司在90年代为适应高速发展的嵌入式系统而共同研发的一项互连技术。经过不断地发展,RapidIO成为嵌入式互连技术方面唯一一个得到授权的标准。到目前为止,RapidIO己经成为电信、通信行业以及高性能嵌入式系统中的芯片与芯片之间,板间、背板间互连技术的主要手段,几乎所有的嵌入式系统芯片设备供应商都加入了RapidIO行业协会[4]。针对机箱内的内部系统互连,RapidIO总线具有最优的总线结构。

1 RapidIO总线协议简介

RapidIO总线是一种新型嵌入式总线,具有传输效率高、系统成本低、系统稳定性好等优点。该总线采用交换结构,支持点到点或点到多点的串行传输,运用8B/10B编码将时钟嵌入数据中,物理上采用LVDS信号[5]。这些特点为RapidIO总线的数据传输速率的提升提供了可靠保障。

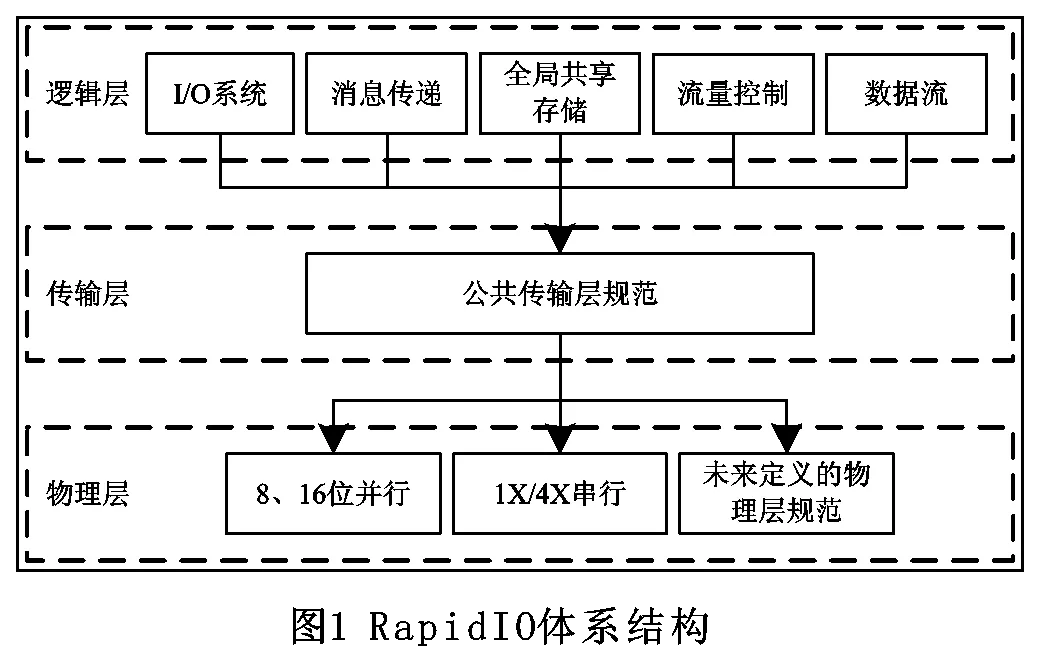

RapidIO协议分为逻辑层、传输层、物理层,体系结构[6]如图1所示:

这种分层体系结构使得系统具有良好的灵活性、扩展性和模块化能力。

逻辑层位于协议的最高层,提供用户接口的相关规范。主要由五大规范组成,包括I/O逻辑操作协议、消息传递协议、全局共享存储协议、流量控制协议以及数据流协议。

传输层位于协议的中间层,兼容不同的逻辑层和物理层应用,为不同的系统提供相同的或可共存的包格式来传输数据。

物理层位于协议的最底层,定义了两种物理层器件级接口标准:8/16并行LVDS协议和1x/4x串行协议。两种协议具有相同的编程模型、事务处理和寻址机制。8/16并行LVDS协议主要用于紧耦合系统内部互联,支持的工作频率为250MHz、500MHz、750MHz及1GHz,传输性能可从1Gbps到 64Gbps。1x/4x串行接口则适合于长距离传输、引脚数目有限且对延迟要求不高的应用,支持1.25G、2.5G、3.125G、5G、6.25G等5种波特率,传输性能可从1Gbps到20Gbps[7]。

2 RapidIO接口模块设计

RapidIO接口模块实现对用户数据的透明传输。针对基于FPGA+DSP结构的系统,用户数据、命令通过RapidIO接口模块,由Avalon总线标准转换为RapidIO总线标准发送出去;同时接收其他处理单元的数据、命令,并通过RapidIO接口模块将其转化为Avalon总线标准,然后送给用户逻辑进行处理。对用户而言,无需了解RapidIO交互细节,可基于Avalon总线甚至自定义新的协议来实现使用RapidIO接口的系统,大大提高了灵活性,也可减少开发者重复开发。

RapidIO接口模块实现方案如图2所示。

用户逻辑不直接与RapidIO总线进行数据的交互,而是增加两套相互独立的数据缓存空间,对需要发送和接收的数据先解耦,然后发送出去或者返回给用户,这样便满足同时进行数据接收和发送的要求。

在发送数据时,RapidIO接口模块将接收到的一组数据数据写入缓存,然后发起一次直接存储器访问(DMA),查询DMA状态,完成后发送一个门铃中断给目标RapidIO接口模块,提示其取数据。相反,在接收数据时,RapidIO接口模块接收到门铃中断后,读命令空间和数据缓存空间,得到需要处理的命令信息、状态信息和数据。

这样相对用户来说,可以直接使用DSP来进行用户数据传输逻辑的灵活定义,而不必关心RapidIO底层的实现。且对大多数的嵌入式系统来说,特别是数字信号处理系统,使用DSP+FPGA的硬件结构是非常流行的。

3 RapidIO接口模块的实现

处理单元采用DSP+FPGA架构,DSP芯片选用TI公司的TMS320C6000系列芯片。FPGA选用Altera公司的StratixⅡ GX系列芯片。FPGA实现RapidIO总线协议,DSP提供用户逻辑接口,并实现对RapidIO总线中各寄存器的管理。

软件主要采用VHDL语言和C++语言进行编程实现。在软件设计中,采用面向过程的、自顶向下分解和构成层次;以功能实现为单元,由底向上构造和组合模块,以实现层次化和模块化的结构设计。

RapidIO接口模块中FPGA软件设计核心是利用Quartus已有的IP核实现RapidIO协议[8],利用SOPC(可编程片上系统)编程将DMA和RAM等资源有机地结合在一起,实现RapidIO接口,此外还提供接口转换时序逻辑为DSP管理RapidIO软件核提供通路。

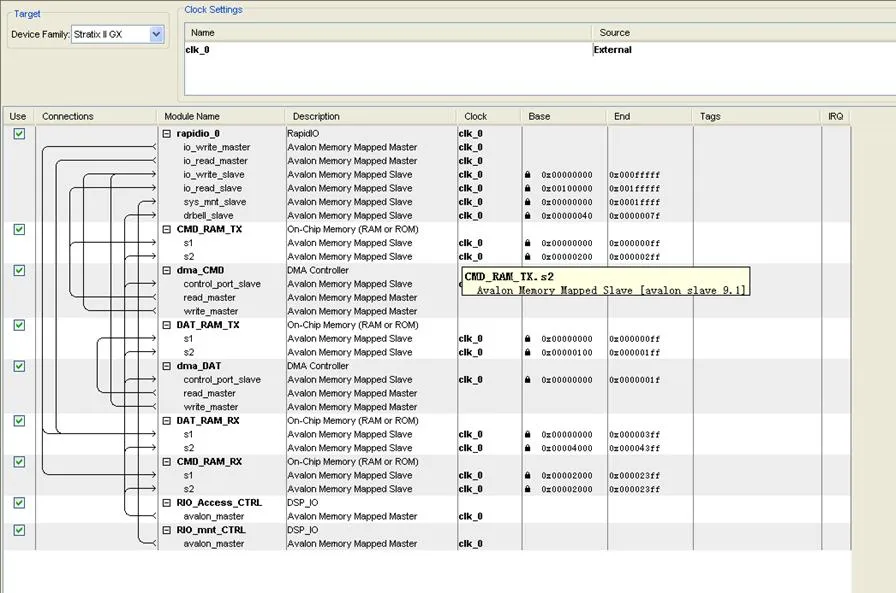

SOPC系统的搭建主要就是在SOPC Builder中添加相关组件并按照一定的逻辑关系将各组件连接好,形成一个有独立功能的系统。在SOPC编辑界面中,加入RapidIO组件,DMA组件、片内存储器、DSP_IO模块。各个SOPC中提供的组件,均提供Avalon-MM总线的标准接口。按照逻辑关系将各组件连接起来如图3所示。

图3 SOPC编程结构

RapidIO核[9]参数配置界面如图4所示,按向导完成协议各个层次的参数配置。

设置DMA参数最大突发传输大小为128个单元,对发送的数据和命令分别用不同的存储器和DMA,这样区分数据的类别,便于管理。对接收存储器不使用DMA,因为可以通过门铃标志判断数据的传送状态,实时接收数据。

加入片内存储器,设置存储深度设为128字节。存储器将命令和数据分开,发送和接收分开,形成四个独立的存储器,这样更便于管理和提高效率。

图4 RapidIO的IP核参数设置

DSP_IO模块是一个自定义模块。DSP与FPGA通信使用EMIF接口,而SOPC组件并不提供对系统外部的Avalon-MM接口,因此需要建立一个内部Avalon-MM接口到外部EMIF接口的转换器,实现DSP与SOPC内部组件的通信。在SOPC编程界面中,可以自定义DSP_IO模块,根据Avalon-MM接口时序和EMIF接口时序,可以方便地设计出DSP_IO模块的信号时序。根据时序配置相应参数即可。

DSP主要完成控制功能,包括初始化、复位、数据的发送接收等。

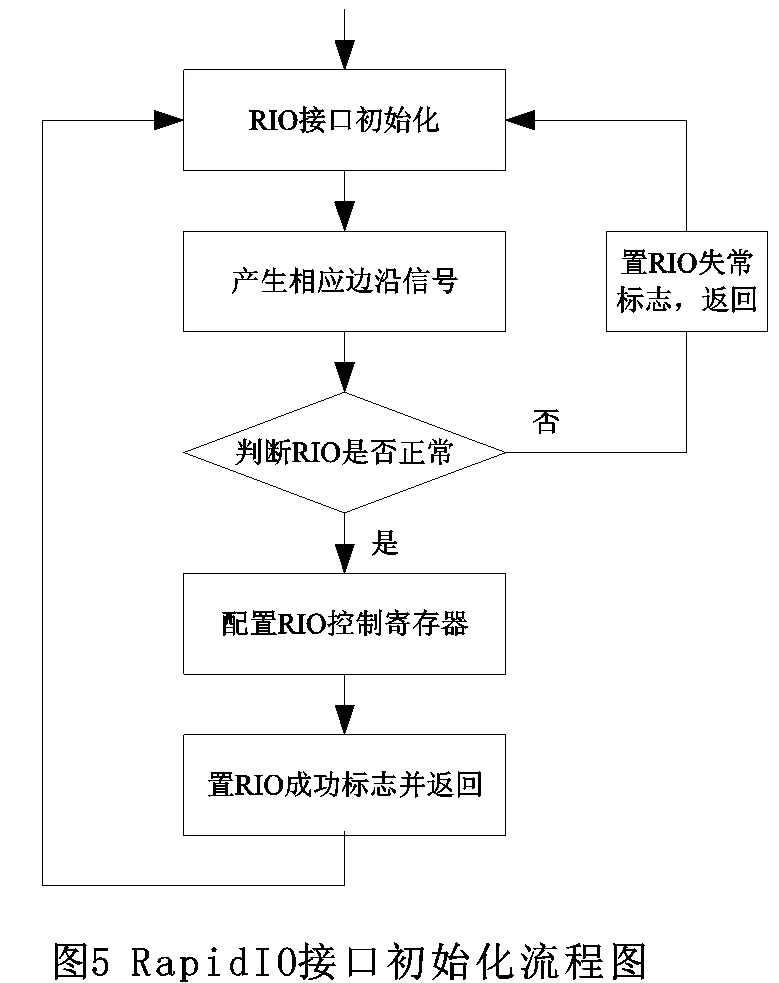

RapidIO初始化软件流程如图5所示。

1)主机开机或者接收到初始化命令,开始初始化。

2)系统首先对GXB powerdown产生一个下降沿信号,再对SOPC reset产生一个上升沿信号。

3)判断读RapidIO核的端口0的错误状态寄存器和命令状态寄存器(CSR),开始端口初始化。若正常则进行寄存器配置,若错误跳转到(1)。

4)设置器件ID寄存器,设置Base Device ID寄存器。将Port General Control CSR 寄存器中的ENA区域置1。设置发出维护请求包的目的地址,置Tx Maintenance Window 0 Control 寄存器的目的ID区域。设置全局地址适配窗口,将Tx Maintenance Window 0 Mask寄存器的第二位WEN区域写1。

5)初始化完成。

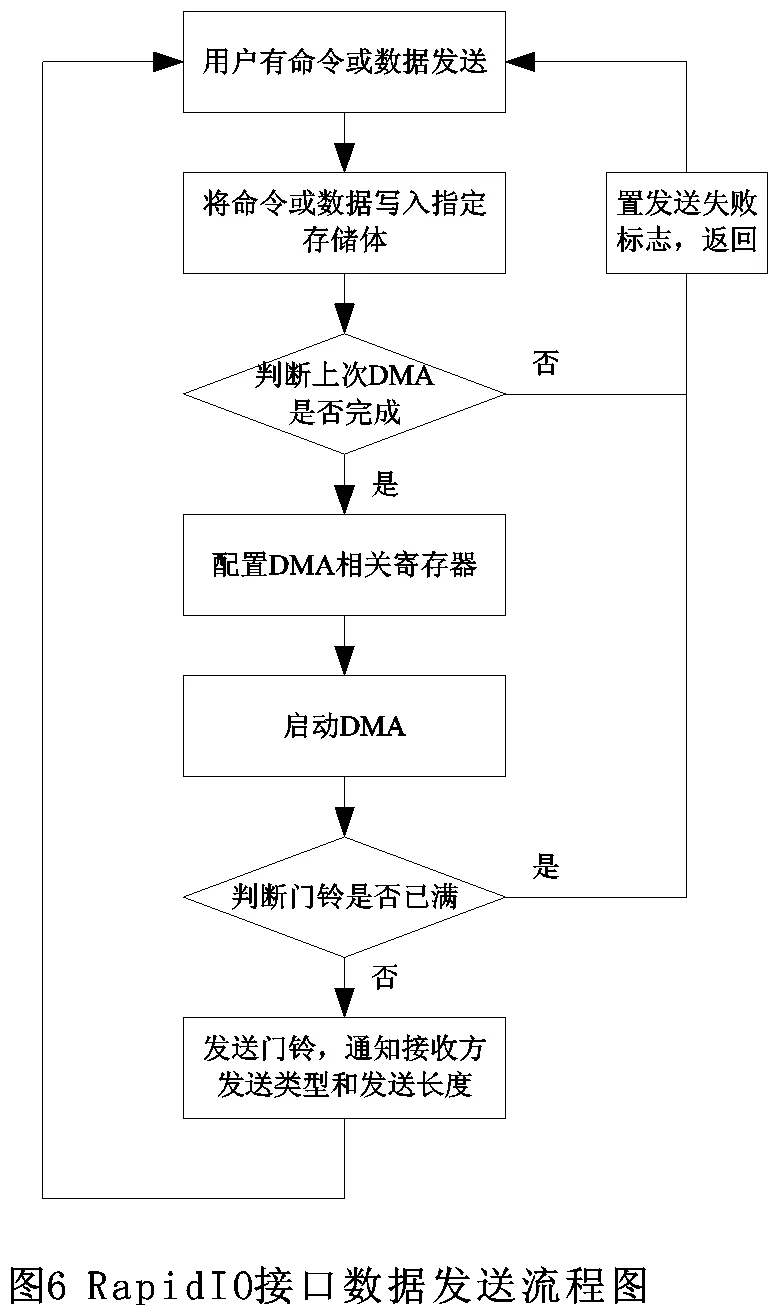

RapidIO接口数据和命令发送软件流程如图6所示。

1)用户有命令或数据发送时,先将命令或数据写入指定的存储器。实现用户与RapidIO之间数据的解耦。

2)读DMA控制寄存器,判断上次DMA传输是否完成,若未完成,则返回发送失败。DMA未完成不能进行新的数据的写入,会导致两次数据的冲突。若完成,则启动DMA寄存器配置。

3)配置DMA寄存器,包括读地址、写地址和长度。

4)启动DMA。

5)读门铃发送寄存器状态,如果发寄存器满,则返回发送失败。不能写入门铃,将无法通知目标接口进行数据的接收。如果发寄存器未满,则发送门铃。

6)写门铃控制寄存器。门铃中包含信息类型、信息长度以及信息发送方ID等信息。门铃是接收方接收数据的唯一标志。发送完成后等到下一次数据的发送。

DSP接收数据或者命令过程很简单,在收到门铃中断后,读取接收存储器中的数据或命令即可,不再赘述。

DSP需要完成普通数据、命令数据的发送和接收,DMA的控制,门铃的发送和解析等功能。在DSP中,可以使用不同的地址空间来区分这些功能[10]。此外,根据功能的不同,将地址空间分为若干块,不同的功能使用不同的地址空间可以使得程序结构清晰,逻辑简单,运行效率高。根据实际的需要,可将地址空间分为SOPC 组件,门铃事物,本地维护等四大块地址空间。而SOPC组件地址空间还可进一步细分。需要注意的是,地址空间的分配需要有预留,方便以后功能的扩展。

4 RapidIO接口模块的互联实验

本实验平台由2个处理单元构成。DSP仿真器使用Wintech TDS560USB PLUS,FPGA仿真器使用Altera V10.0。

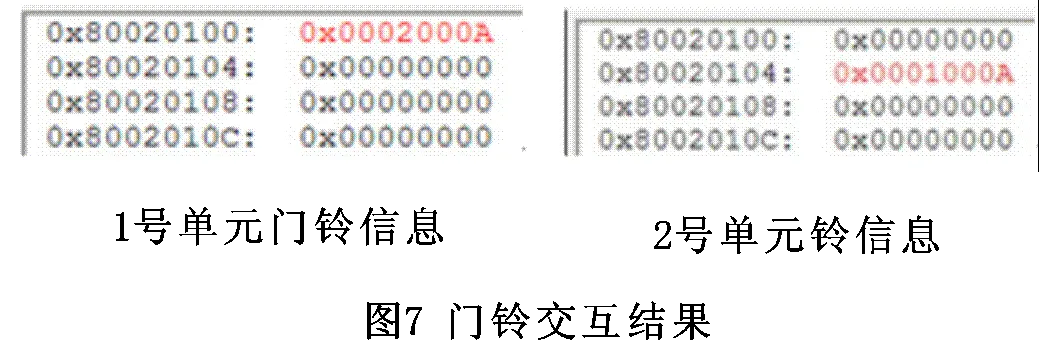

手动门铃通路测试。这样一方面测试了RapidIO通路的连通性,也测试了DSP与FPGA之间的交互性。门铃信息由到达RapidIO接收单元后,接收单元的DSP会将其读出并存于特定存储单元,通过CCS软件,可在PC上显示。门铃发送和接收显示的地址为0x80020100和0x80020104两个地址单元。处理单元的ID分别设为1和2。门铃信息空间高16位为ID信息,低16位为门铃内容信息。

1号单元向2号单元发送门铃信息为a,结果如图7所示。

两个单元之间门铃信息发送和接收的ID信息指示及门铃内容均正常,交互正常。系统门铃通路正常。也证明RapidIO连通性正常。

5 结束语

RapidIO总线技术是一种较为成熟的下一代嵌入式总线技术,具有诸多优点。本文首先对RapidIO总线协议进行了阐述,重点说明了RapidIO总线的特点。针对熟悉Avalon总线,而对RapidIO总线较为陌生的用户,对FPGA+DSP这类典型嵌入式应用系统中RapidIO接口的设计作了详尽的阐述,并给出相应的FPGA和DSP软件的设计和实现,为该类用户提供了一种简单可行的解决方案。最后对实现的RapidIO接口进行了连通性测试。

[1] 李少龙,高俊,娄景艺.基于SRIO总线的数字信号处理系统的实现 [J].通信技术,2012,(5):101-103.

[2] 裘嵘,郭御风,江乱,等. 新型高性能互连技术HyperTransport研究[J]. 计算机应用研究,2004,(5):258-259.

[3] 李琼,郭御风.I/O互联技术及体系结构的研究与发展[J] .计算机工程, 2006,32(12):93-95.

[4] Wu Changrui, Cen Fan, CaiHuizhi.A High-performance heterogeneous embedded Signal processing system based on serial rapidIOinterconnecTIon [J].InsTItute of AcousTIcs, Chinese Academy of Sciences, Beijing,2010,28(1):611-612.

[5] Altera CorporaTIon.LVDS SERDES Transmitter / Receiver (ALTLVDS_TX andALTLVDS_RX) MegafuncTIon [EB/OL].101 InnovaTIonDriveSan Jose, CA 95134,2012.

[6] Fuller S.RapidIO the embedded system interconnect[M].NewYork:John Wiley & Sons,Inc,2005.

[7] 王运盛,王坚,周红.基于RapidIO的TIPC通信软件设计[J] .电讯技术,2012,(12):1980.

[8] 吴海燕.基于RapidIO总线的信号处理平台设计[D].成都:电子科技大学, 2006.

[9] Altera CorporaTIon. RapidIOmegacore function user guide [EB/OL].101 InnovaTIonDriveSan Jose, CA 95134, 2009.

[10] 廖娜.DSP应用技术综述[J].IT技术论坛,2008, (32):78.

Implement of RapidIO Protocol Based on FPGA+DSP

Fan Haifeng,Ye Zhaoyang

(PLA South China Sea Fleet, Zhanjiang 524002, Guangdong, China)

TP393

A

1003-4862(2017)09-0051-05

2017-06-15

范海峰(1977-),男,高级工程师。研究方向:计算机嵌入式系统、计算机网络。