基于FPGA的DDFS函数信号发生器设计

2017-09-15黄丽

黄 丽

(武汉铁路职业技术学院,湖北 武汉 430205)

基于FPGA的DDFS函数信号发生器设计

黄 丽

(武汉铁路职业技术学院,湖北 武汉 430205)

FPGA的可编程属性使得其在通信系统设计中使用越来越频繁,文章采用DDFS算法技术,以模拟电路为基础架构,完成了一个多种波形输出、高精度的数字信号发生器设计。且设计了以单片机加LCD、按键为输入控制及实时显示的最小系统,可以手动输入选择输出如方波、正弦波及三角波等任意频率可变的信号。

FPGA;单片机;DDFS;函数信号发生器

有线或者无线通信系统的研究或应用领域,高精度、多类型的信号源必不可少[1]。故信号发生器是用来产生正弦波、锯齿波、方波、三角波等各种信号的一种通用仪器,在科学研究和工程设计中广泛应用[2]。成熟的信号发生器一般采用集成电路器件设计实现,其输出信号只能是某种特定的周期性信号。如果采用现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)进行波形存储器设计之后,将能合成任意波形的信号[3]。用直接数字式频率合成器(Direct Digital Synthesizer,DDS)产生正弦信号的方法具有输出频率信号稳定、相位连续等特点,且很容易通过数字的方法实现调整。本文采用89C52单片机为控制核心,结合FPGA任意可编程功能,采用经典的直接频率数字频率合成(Direct Digital Frequency Synthesis,DDFS)技术,辅助以部分放大模拟电路,设计出了一个高精度、可手动选择、波形稳定的数字信号发生器,输出波形可以在正弦波、方波及三角波间切换。

1 系统总体设计方案及实现框

1.1 总体设计框

系统总体设计框如图1所示,本系统由单片机89C52完成系统控制和数据运算,波形表存储在FPGA中,由FPGA实现DDS的地址累加器,在外围采用D/A及滤波电路完成波形的合成,幅度控制采用双D/A。第一级的输出作为第二级D/A转换的参考电压,滤波模块电路用于滤除由第二级DAC产生的高频分量,以及数字采集样时产生的高次谐波分量,从而得到平滑干净的信号。

图1 总体设计框

1.2 关键模块设计

本系统的关键模块主要是基于FPGA DDFS算法设计。

1.2.1 FPGA的设计

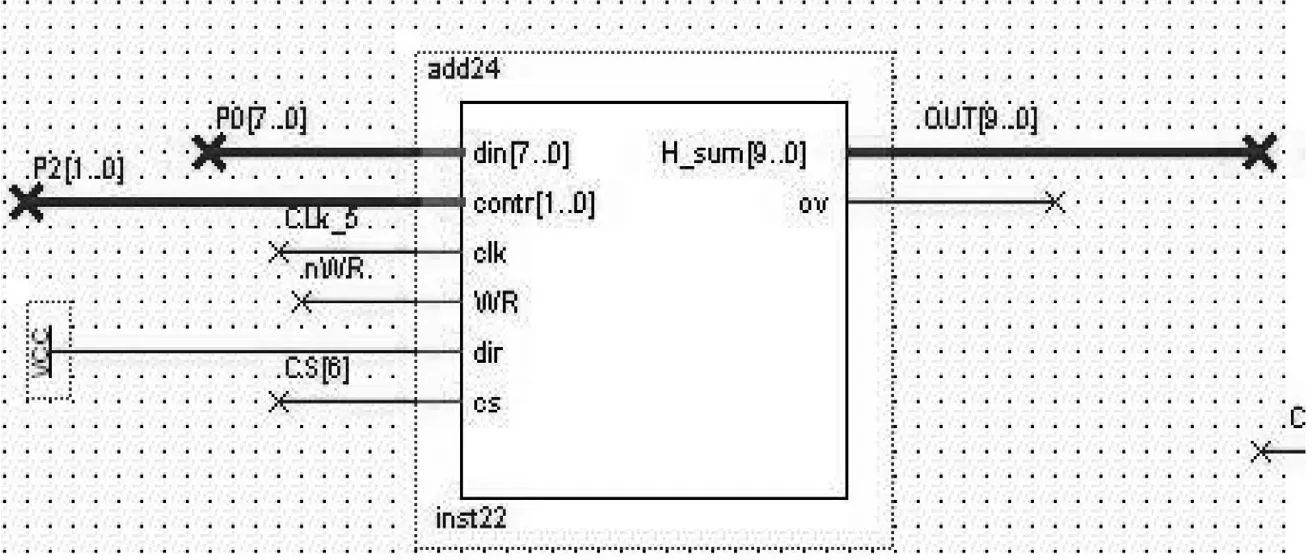

FPGA设计的DDFS实际就是个相位累加器,设计不同的累加步进,即可得到不同的频率分辨率,步进越小,输出的波形越平滑。FPGA将累加输出值送到内部存储好的波形数字幅度RAM的地址上,读出数据后送到DAC完成数模转换,最终输出数字波形到辅助模拟电路,单片机完成相关频率和步进的配置。频率合成器的核心模块如图2所示。

图2 FPGA中核心DDS模块

1.2.2 基于单板机的人机交互模块设计

人机交互是由单片机、LCD和按键来实现的,单板板选用INTEL公司的89C52,其用于控制LCD显示和按键输入控制等;同时还要控制FPGA的输入,配置其频率合成所需要的步进值、信号波形类型等。单片机与FPGA的有基于Intel总线模式的读写接口,对FPGA内部实现配置和选择,从而让FPGA内部的双口RAM内存储数据的读出送到DAC上。两片DAC的控制接口也由单板模拟产生。

本信号发生器人机交互的总体设计思想是:单片机循环等待按键输入,默认输出标准的1 kHz方波,用户可以通过按下按键后选择实现各种功能,如实现方波、正弦波和三角波之间的切换。同时还可完成频率控制和幅度控制,这都可以通过输入相应的数字完成所需要输出波形的频率或幅度输入。LCD的显示也由单板在控制扫描输入,最大支持输入6位数字输入,系统自动默认为001000。设置有取消/删除键取消本次输入或修改之前输入的参数。

1.3 辅助模拟电路设计

模拟电路主要是完成最终的模拟信号输出,选择了2片DAC和滤波放大模块共同实现。DAC器件使用的是DA公司的DA0832,由于DA0832为电流输出型的转换器,因此要获得模拟电压输出时,需接外加转换电路,本设计中采用运放电路作为转换电路。

后边的滤波模块采用二阶巴特沃兹滤低通滤波器进行滤波,滤除波形中由D/A产生的高频分量,使输出波形平滑不失真。

2 系统测试结果

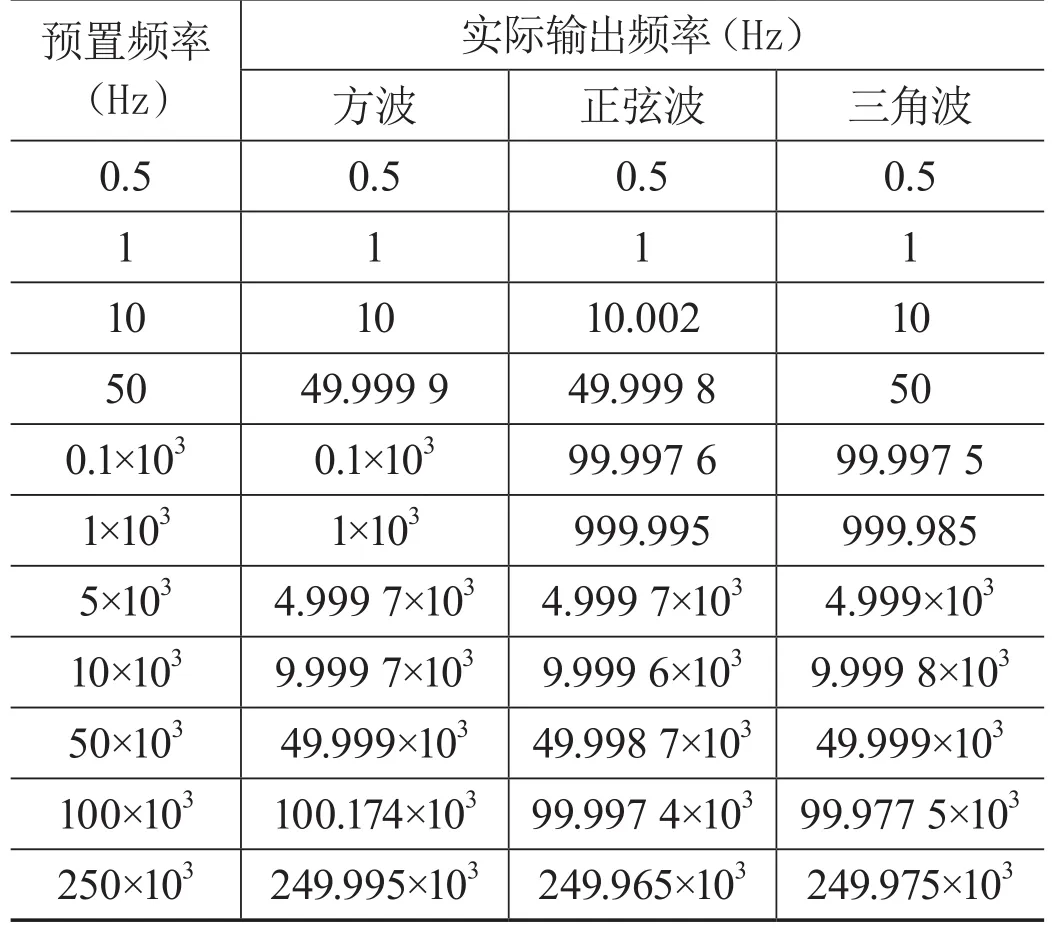

按照上述方案完成系统设计后,对本设计进行了详细的系统测试,本设计的单板、FPGA和模拟电路皆能正常工作,滤波电路也能正常滤波,通过示波器进行观测,输出的波形都能够按照按键输入选择的模式、频率和幅度来输出。部分相关测试数据如表1所示。

表1 基本波形的频率测量结果(0.5~250 kHz,步进0.5 Hz)

3 结语

本设计采用了FPGA来实现DDFS算法,配以INTEL的单片机89C52来作为设计的控制核心,并配合LCD和按键完成人机交互设计,从而完成了一个结构清晰、使用方便且成本低的信号发生器设计,配合以模拟电路,完成高精度、分辨率高的信号产生[4]。方案的核心是用FPGA设计DDFS算法,比采用专用DDS芯片更为灵活方便。通过CPU重新配置和更新FPGA中的双端口RAM中的波形数据,就可以完成任意波形的输出,具有相当大的灵活性[5-6]。FPGA芯片设计为PS加载方法,还支持在线升级,既可以将更多的波形设计输入到此系统中,且不会增加系统的开销,非常灵活多变,这在进行教学研究时具有很大的实用价值。

[1]韩叶祥,朱兆优,张斌.基于MAX038的程控函数信号发生器的设计[J].电子元器件应用,2008(5):22-25.

[2]郝小江,罗彪.基于FPGA的函数信号发器[J].电测与仪表,2008(5):49-51.

[3]易宏,杜志明,吴国辉,等.基于FPGA的函数信号发生器设计[J].电气电子教学学报,2009(6):35-37.

[4]郭振永,邓云凯,杨松,等.线形调频信号DDS频率合成源的设计与实现[J].现代雷达,2005(3):56-59.

[5]郭德淳,费元春.DDS的杂散分析及频率扩展研究[J].现代雷达,2002(1):63-66.

[6]邱娜灵,杨阳.一种基于单片机的函数信号发生器的设计与实现[J].信息通信,2017(5):90-92.

Design of DDFS function signal generator based on FPGA

Huang Li

(Wuhan Railway Vocational College of Technology, Wuhan 430205, China)

The programmable attributes of Field Programmable Gate Array(FPGA)makes it more frequently used in the design of communication system. This paper completes a design with variety of waveform output and high precision digital signal generator uses Direct Digital Frequency Synthesizer(DDFS)algorithm technology and analog circuit as the basic structure. And designs of the smallest system with microcontrollers plus LCD, the key input control and real-time display, which can manually enter the selected output arbitrary frequency variable signal such as square wave, sine wave and triangular wave.

Field Programmable Gate Array; microcontrollers; Direct Digital Frequency Synthesizer; function signal generator

黄丽(1987— ),女,湖北孝感人。