一种应用于EEPROM读出放大器的设计

2017-09-12肖培磊胡小琴刘建成

肖培磊,胡小琴,刘建成

(1. 中国电子科技集团第58研究所,江苏 无锡 214035;2. 中国原子能科学研究院(401所),北京 102413)

研究与试制

一种应用于EEPROM读出放大器的设计

肖培磊1,胡小琴1,刘建成2

(1. 中国电子科技集团第58研究所,江苏 无锡 214035;2. 中国原子能科学研究院(401所),北京 102413)

读出放大器是电可擦除非易失性存储器(EEPROM)中的关键模块,其读取速度决定了EEPROM的操作频率。基于国内先进的0.18 μm工艺,对EEPROM放大器的基准电流源和比较器进行了分别设计,测试结果显示读出放大器的响应时间小于70 ns,可满足10 MHz的EEPROM存取速度的要求。

读出放大器;存储器;EEPROM;响应速度;操作频率;比较器

非挥发存储器EEPROM IP核广泛应用于可改写、易使用的数据存储领域,如智能卡、非接触卡、移动通讯和微控制器等。这些产品都要求EEPROM具有读出数据快速、稳定及功耗低等特性[1]。EEPROM数据读取时间由地址输入到数据输出的关键路径决定[2],包括地址缓冲、译码器、存储单元、读出放大器和输出缓冲器;并且存储容量越大,速度越慢。其中读出放大器是提高速度的关键模块。

本文基于国内先进0.18 μm EEPROM CMOS工艺,设计了一款高性能读出放大器,并成功地应用于一款EEPROM芯片中。

1 读出放大器电路结构

读出放大器由两部分组成:基准电流源和电流比较器。对于每个字节8位的数据并行输入输出的EEPROM,需要8个读出放大器。在电路设计中,设计为8个比较器共用一个基准电流源,既节省芯片面积,又降低芯片功耗。

1.1 参考电流源

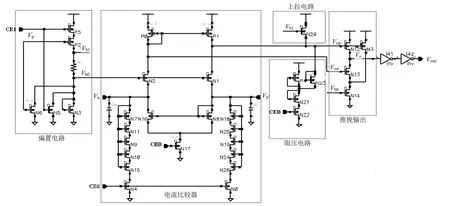

基准源有带隙基准(BGR)、BMR等多种结构,其中以BGR结构的基准源最为常见。电路中采用了图1所示的电流基准源,并没有采用带隙基准电路中的PATA电流的原因:(1) BGR电路需要一定的启动时间,不能满足快速读操作的需求;设计为芯片上电后即启动,增大了额外的静态功耗;(2) BGR中的PATA电流与EE单元读出电流相对独立,两个电流的电压和温度特性不一致。

图1采用电阻负反馈的共源放大器作电流产生源,并用反相器代替放大器,简化了电路;通过调节电阻值和反相器的翻转点来唯一确定电流值,电流值的大小设计为被编程存储单元电流的一半。使能端CE1控制基准源的开关,几乎没有静态功耗。由于存储单元的读出电流随电压和温度的变化而波动较小,该种结构的参考电流可满足精度要求。

图1 参考电流源Fig.1 Reference current source

1.2 电流比较器

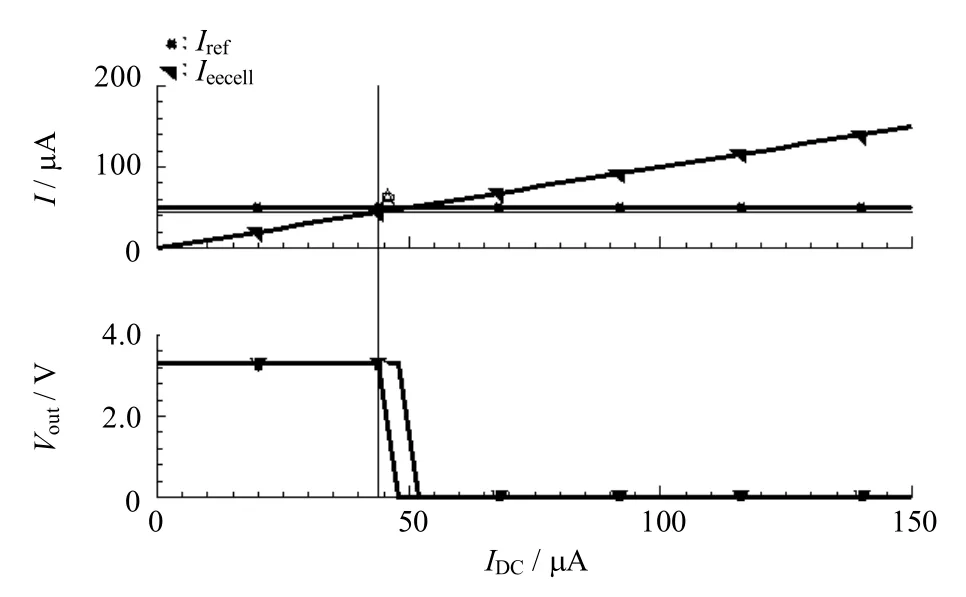

电流比较器设计为双端输入、双端输出的全差分结构,如图2所示。两个输入端Vn、Vp分别连接着参考电流源Iref和EE单元,三个使能端CE0、CE1、CEB,一个偏置电压输入端Vb0,差分输出端口Von、Vop。其工作原理为:CE0=1、CEB=0时,电路处于非读状态,此时 Vb0=0,电路没有静态功耗。当CE0=0、CEB=1时,电路处于读出状态;CEB=1为比较器电路提供电流沉;Vb0提供2.1 V左右的偏压;Vn外接参考电流Iref,Vp外接存储单元电流,当两个电流不相等时,Von、Vop差分信号输出。

1.3 优化设计

为了将差分输出信号转换为单端信号,增加一组推挽输出的源随器和缓冲器。此外,还要考虑寄生电容的影响。在大规模EEPROM芯片中,与位线相连的金属导线和大量的 EE单元产生较大的寄生电容,导致Vp端充电时间延长,从而制约了放大器的响应时间;严重时,会使存储数据发生误读(Vp端寄生电容的充电电流误认为EE单元导通电流)。对此,需在Vop端增加上拉电路,同时为了避免上拉过充现象,还需设计限压支路。完善后的比较器电路如图2所示,包括偏置电路、电流比较器、上拉电路、限压电路及输出缓冲电路。

图2 电流比较器整体电路Fig.2 Current comparator circuit

目前,除了增大上拉N管的宽长比之外,读出放大器的响应时间似乎没有明显缩短。在参考文献中[3-4]均采用了正反馈电路来提高响应速度,在本次电路设计中也巧妙地引入了正反馈技术。如图2所示,Vp端信号被引入到偏置电路中。当Vp端被较大的寄生电容拉低时,偏压Vb1、Vb0升高,上拉N管的栅压升高,从而提供更大的充电电流,使Vp端快速升高稳定。当Vp端被拉高后,偏压Vb1、Vb0降低,相应地充电电流降了下来。此外,在推挽输出级Vb0的降低加速了Vo跟随Vop,提高了响应速度。

2 仿真与分析

基于国内先进的0.18 μm EEPROM CMOS工艺,对上述快速读出放大器电路采用Cadence Spectre软件进行电路仿真。(1)灵敏度仿真:放大器的Vn接固定电流Iref=50 mA,对Vp端口电流进行三温直流扫描,结果如图3所示。从仿真结果可知,当两端电流差值大于6 mA时,放大器将迅速响应。较大的响应空间,不仅提高了放大器的响应速度,同时延长了EE单元的擦写寿命(因为随着EE单元的擦写次数增加,阈值窗口逐渐变小[5],被编程与被擦除EE单元电流逐渐靠近参考电流,容易导致误读)。(2)充电能力仿真:前面已提到Vp连接至EEPROM阵列的位线上,在Vp端加12 pF的等效负载电容,进行读1模拟仿真。仿真结果如图4所示,由于寄生电容的存在,在放大器开始工作后假读为0,而该电路设计有正反馈的充电支路,12 ns后充电完成读出正确数据。

图3 放大器灵敏度仿真1Fig.3 Sensitivity simulation of amplifier1

图4 放大器灵敏度仿真2Fig.4 Sensitivity simulation of amplifier2

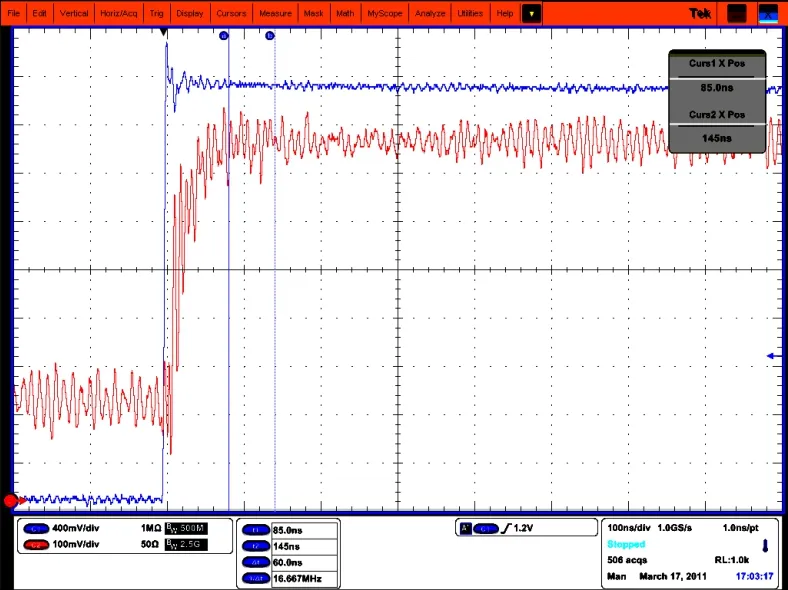

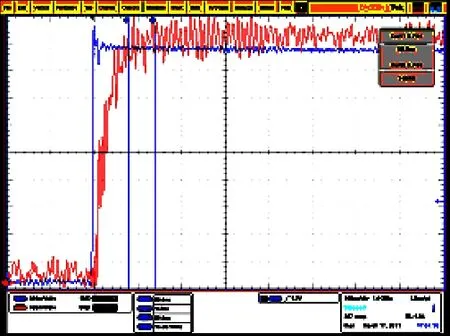

3 测试

将放大器的Vp端引出作为测试端,可真实地反应读出放大器的工作环境,通过NI测试系统和示波器,在1兆位的EEPROM芯片中,对Vp端口进行读“0”和读“1”测试。图5和图6分别是读出放大器在读“0”和读“1”时,Vp端口电压的测试波形。从测试结果可得,Vp端口充电完成所需时间70 ns左右。考虑到测试探头电容对信号的影响,整个响应时间应该小于70 ns。

4 结论

本文提出了一种快速读出放大器的设计结构,使能端口控制其几乎没有静态电流,反馈结构使其在较低的动态功耗下能快速响应。最终应用于一款1兆位EEPROM芯片中;基于国内0.18 mm EEPROM工艺流片,测试结果表明读出放大器的响应时间在70 ns内,满足EEPROM芯片10 MHz的工作频率需求。

图5 读“0”时位线电压波形Fig.5 Read“0” bit-line's voltage wave

图6 读“1”时位线电压波形Fig.6 Read“1” bit-line's voltage wave

[1] 徐飞, 贺祥庆, 张莉. 一种40 ns 16 kB EEPROM的设计与实现 [J].微电子学, 2005, 35(2): 133-136.

[2] SASAKI K. A 7 ns 1MB CMOS SRAM with current sense amplifier [C]// ISSCC. NY, USA: IEEE, 1992: 208-209.

[3] TAKEDA K. A 16 MB 400 MHz loadless CMOS four-transistor SRAM macro [J]. IEE J Solid State Circuits, 2000, 35(11): 18.

[4] CAPPELLETTI P, GOLLA C, OLIVO P, et al. Flash memories [M]. London: Kluwer Academic Publishers, 1999.

[5] 于总光, 郝跃. 电可改写非挥发存储器 [M]. 北京: 国防工业出版社, 2002.

(编辑:曾革)

Design of EEPROM’s sense amplifier

XIAO Peilei1, HU Xiaoqin1, LIU Jiancheng2

(1. China Electronics Technology Group Corporation No.58th, Wuxi 214035, Jiangsu Province, China; 2. China Institute of Atomic Energy, Beijing 102413, China)

The sense amplifier is the key module of EEPROM (Electrically Erasable Programmable Read-Only Memory) and it's response speed directly determines the EEPROM's operating frequency. Based on domestic advanced 0.18 μm EEPROM process, the amplifier's refer current source and comparator were respectively designed in this paper. The testing results show that the response time of the sense amplifier is less than 70 ns, and completely satisfies 10 MHz -EEPROM frequency requirement.

sense amplifier; memory; EEPROM; response speed; operating frequency; comparator

10.14106/j.cnki.1001-2028.2017.09.007

TN304

A

1001-2028(2017)09-0030-03

2017-07-16

肖培磊

肖培磊(1983-),男,山东泰安人,工程师,主要从事ADC、DC-DC电源开发与应用研究,E-mail: xiaoplcetc58@163.com ;胡小琴(1985-),女,安徽池州人,工程师,主要从事反熔丝存储器的研究,E-mail: kokojoan@163.com 。

时间:2017-08-28 11:09

http://kns.cnki.net/kcms/detail/51.1241.TN.20170828.1109.008.html