双踪示波器设计中的采样率自适应分配技术

2017-09-08张凯李晨杰刘豫东金明顾斌吴珊珊

张凯+李晨杰+刘豫东+金明+顾斌+吴珊珊

摘 要: 基于奈奎斯特采样定理和FPGA器件设计了一款采样率自适应分配的双踪数字示波器。采用双通道共享双A/D,按照输入信号带宽比自适应分配二通道采样率的方案,有效地解决了传统模式下二通道采样率无法相互调剂的弊端,从而显著提高了示波器的带宽上限和采样效率。在总采样率约束下,较传统采样模式,带宽上限提高近2倍, 对高斯分布下的信号带宽采样效率提高约1.5倍。

关键词: 示波器; 带宽; 采样; 自适应; FPGA

中图分类号: TN702?34 文献标识码: A 文章编号: 1004?373X(2017)17?0154?04

Self?adaptive allocation technology of sampling rate in design of dual?trace oscilloscope

ZHANG Kai1, 2, LI Chenjie1, LIU Yudong1, JIN Ming2, GU Bin2, WU Shanshan2

(1. Jiangsu Province R&D Center of Electronic Information Engineering Technologies, Nanjing 210023, China;

2. School of Electronic Information Engineering, Nanjing College of Information Technology, Nanjing 210023, China)

Abstract: Based on the Nyquist sampling theorem and FPGA devices, a sampling rate adaptively?allocating dual?trace digital oscilloscope was designed. The two channels sharing dual A/Ds are adopted to allocate two channels′ sampling rates in accordance with the bandwidth ratios of input signals, and overcome the disadvantage that the sampling rates cannot be mutually supported between two channels in the traditional mode, thereby the bandwidth upper limit and sampling efficiency of the oscilloscope are significantly raised. Under the constraint of the total sampling rate, the upper limit of the bandwidth is nearly doubled, and the sampling efficiency is increased by roughly 1.5 times for signals′ bandwidths in Gaussian distribution, in comparison with the traditional sampling mode.

Keywords: oscilloscope; bandwidth; sampling; self?adaption; FPGA

0 引 言

數字示波器作为电子设计及工业测量领域里一种广泛应用的电子测量仪器,其工作实质为将时变电信号转换成时域曲线,通过对电量的频率、幅度、电位差等参数进行实时分析,以实现对信号实时变化过程的研究[1?3]。目前,数字存储示波器通常是双通道的,且采用每一个通道配一个A/D芯片,两个通道采样率相同[4?8]。然而,在双踪观察信号时,两个通道信号的带宽相差较大的情况是常见的。因此,传统设计往往会发生如下现象:其一通道的宽带信号由于采样率不够导致欠采样,而另一通道的窄带信号由于采样率过剩导致过采样,从而使示波器的观察能力不能得到充分发挥。基于此,本文提出一种双通道共享双A/D的方案,按照双通道信号带宽比自适应分配采样率,有效地解决了上述问题。

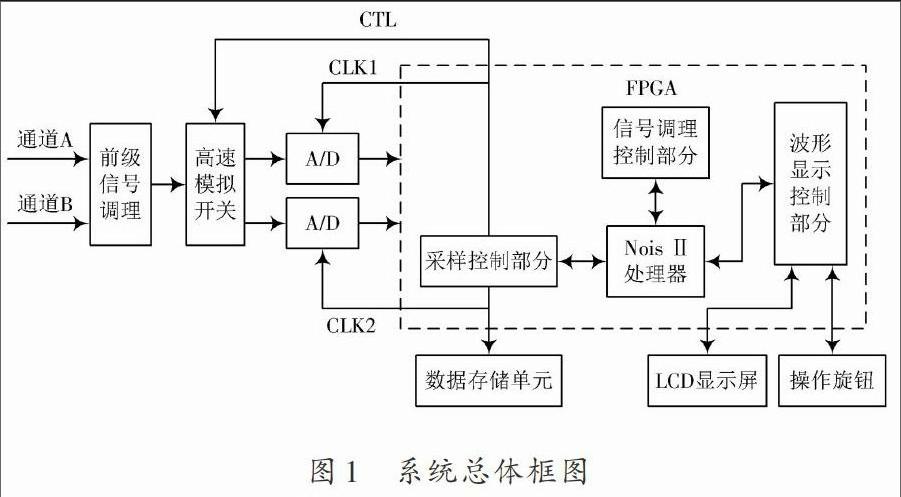

1 系统总体设计方案

如图1所示为系统总体框图。FPGA是整个系统的控制及数据处理核心,负责完成硬件电路以及大量数据信息的处理控制工作。信号从A、B两通道输入后,首先由前级信号调理电路将其调理至A/D转换器采样时所能处理的电压范围以内,而后通过高速切换的模拟开关控制两路目标信号依次进入A/D转换器,将其转换成可处理的数字量,并将采集到的样本点送入FPGA,在此进一步通过FFT分析其带宽信息并转换成控制时序信号来控制模拟开关的工作。波形显示采用240×128的LCD液晶显示触摸屏,可以实现垂直灵敏度从2 mV/div~2.5 V/div共8档,扫描灵敏度从1 μs/div~500 ms/div共10档,以下主要对系统中的主要硬件模块及其功能进行介绍。

2 系统硬件设计

2.1 高速模拟开关

高速模拟开关的工作原理类似单刀双掷开关,通过控制时序信号(CTL)的控制达到对两个采样通道进行依次切换的目的。当目标信号通过高速切换的模拟开关时,A/D转换器在控制信号为高电平时对A通道进行采样,在控制信号为低电平时对B通道进行采样。

2.2 A/D采样电路

系统中ADC采用TLC5510芯片,其最高采样率为20 MHz,实时采样率可达16 MHz。TLC5510为8 b芯片,对应于0x00~0xFF128点采样范围。但实际只用高7位作为有效位,每比特对应16点,故其采样频率可通过下式得到:endprint

(1)

式中表示LCD显示屏上水平网格中的时间。

2.3 信号调理控制部分

如图2所示为信号调理控制部分电路,负责进一步完成对输入信号的电压调节。

图2 信号调理电路

可见,衰减部分主要为一片8 b数模转换芯片(DAC)DAC0832。其输出电压幅度可表示为:

(2)

式中:为输入电压;为来自Nois Ⅱ处理器的输入信号。当发生改变,系统将调整其衰减系数,每一路通道的每档垂直灵敏度都与调理电路的增益相对应,具体的增益因子与垂直扫描灵敏度之间的对应关系如表1所示。

2.4 采样控制部分

采样控制部分的设计是整个系统设计的核心,主要由高速缓存单元、样本存储单元、采样控制单元、数字滤波单元四部分组成,具体的组成框图如图3所示。

(1) 存储单元

高速缓存单元通过FIFO实现,负责存储经A/D采样模块处理后所得的目标信号的数字量,并将其送入样本存储单元存储起来。

(2) 采样控制单元

采样控制单元调用样本存储单元内的样本点,并对样本点进行快速傅里叶变换(FFT)实现对其带宽信息的分析处理,得到信号带宽的加权系数;再根据信号带宽的加权系数产生一种可变脉宽的控制时序信号CTL,实现对高速模拟开关的控制。需要注意的是,控制信号频率满足奈奎斯特采样定理且小于总采样频率,脉宽的变化情况与加权系数的变化情况成正相关。

自适应控制算法结构图如图4所示,设定一个标准量,将带宽信息量化成可处理数值,通过一定的函数关系加权到标准量上得到加权系数。与此同时,把所设定标准量转化成计数脉冲,作为标准计数脉冲,并在一段时间内得到加权系数锁存起来,让标准计数脉冲无限逼近加权系数所映射的计数脉冲,得到的计数脉冲即可作为高速模拟开关和数据存储的控制信号。

(3) 数字滤波单元

由于在模拟开关高速切换的过程中会引入尖峰脉冲,所以考虑在数据存储前先进行滤波处理。经滤波所得的信号采样时序图如图5所示。

3 系统软件设计

本设计基于可编程片上系统(System?on?a?Programmable?Chip,SOPC)技术,以Nios Ⅱ处理器为核心,利用VHDL语言在FPGA芯片上搭建系统,完成信号调理控制部分、采样控制部分以及波形显示控制部分的管理。该系统具有4 B的FLASH存储器和8 B的SDRAM,并通过阿瓦隆桥(Avalon bridge)与Nios Ⅱ处理器相连接,可以使用定时器、JTAG_UART或者其他模块来运行及调试Nios Ⅱ处理器。系统同时增加了可编程I/O外围设备用于驱动外部仿真液晶及控制显示。系统软件主流程图如图6所示。

4 测试结果分析

4.1 测试方案

为了对本文设计的示波器性能进行测试,首先考虑通过仿真对系统性能加以研究,以此完成可行性分析;后进行实验,利用数字合成信号发生器产生正弦信号,并将其分别送入本示波器输入端,在不同的信号峰峰值以及垂直灵敏度条件下对本示波器的峰值、频率值的测量精度加以分析[9?10]。

4.2 可行性分析

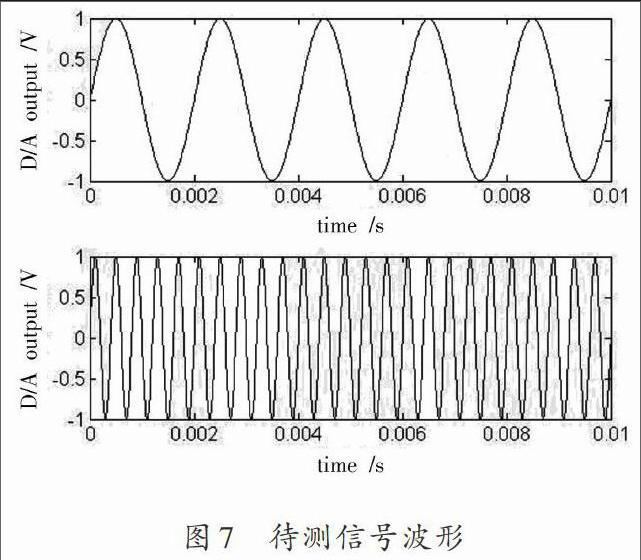

假定送入示波器两输入端的信号幅度为1 V,频率分别为0.5 kHz和2.5 kHz,初相为0的正弦波信号,如图7所示。对本文设计的系统进行仿真所得波形如图8所示。由图7,图8可见,采样率自适应分配的双踪数字示波器可以在提高带宽利用率的同时,完成两路信号的波形显示。

4.3 测试结果

(1) 信号发生器产生的正弦波信号峰峰值为0.8 V,示波器的垂直灵敏度为0.1 V/div时,不同频率信号的测量结果如表2所示。

(2) 信号发生器产生的正弦波信号峰峰值为15 mV,示波器的垂直灵敏度为2 mV/div时,不同频率信号的测量结果如表3所示。

由实验结果可见,本示波器的频率测量误差不高于2%,而电压测量误差小于6%,具有较高的测量精度。其中,频率测量误差主要源自于等精度测频中对频标计数的误差,由高频小信号信噪比较低引起;而电压测量误差则是由在前级调理电路中运放在通频带内幅频特性不平坦、运放间存在串扰等原因所导致。

5 結 语

本文利用FPGA+Nios Ⅱ处理器设计了一款采样率自适应分配的双踪数字示波器。本设计中输入待测信号经过前级信号调理电路把信号调整到A/D输入电压的范围之内,经过A/D转换变成数字信号,送到FPGA中进行相关处理;而后再由Nios Ⅱ处理器把要显示的数据送入LCD屏显示,以此实现信号波形的检测。由于本示波器双通道共享双A/D,按照双通道信号带宽比自适应分配采样率,有效地提高了示波器的带宽利用率。同时,FPGA的应用使得数字存储示波器的设计较为灵活,容易升级,可以根据用户的需要实现电路的升级。

参考文献

[1] 孙铁强.双通道虚拟示波器的设计[J].河北理工学院学报,2002,24(1):54?57.

[2] 安亚君.基于FPGA的多通道数字示波器设计[J].微计算机信息,2011,27(7):115?116.

[3] 叶凯.基于FPGA和LabVIEW的双通道示波器设计[J].西华大学学报(自然科学版),2012,31(5):22?24.

[4] CHAPPEL J F, ZAKY S G. EMI effects and timing design for increased reliability in digital systems [J]. IEEE transactions on circuits and systemsⅠ: fundamental theory and applications, 1997, 44(2): 130?142.

[5] BRACEWELL R N. The Fourier transform and its applications [M]. New York: McGraw?Hill, 1986: 57?63.

[6] BELLANGER M G. Digital processing of signals: theory and practice [M]. New York: John Wiley & Sons, Inc., 1984.

[7] KESTER Walt. High speed design techniques [R]. Massachusetts: Analog Devices Inc., 1996.

[8] SOPHOCLES J O.信号处理导论[M].北京:清华大学出版社,1999:45?49.

[9] 阳兵,彭立艮,江洋.高采样率的双踪数字示波器设计[J].电视技术,2010,34(z1):214?216.

[10] 杨小龙.基于AVR单片机的数字示波器的设计与实现[D].武汉:武汉工业学院,2012.