宽带嵌入式存储系统中实时数据记录的优化方法

2017-09-07彭程飞许家麟吴琼之

彭程飞,许家麟,李 涛,吴琼之

(北京理工大学 信息与电子学院,北京 100081)

宽带嵌入式存储系统中实时数据记录的优化方法

彭程飞,许家麟,李 涛,吴琼之

(北京理工大学 信息与电子学院,北京 100081)

针对宽带信号长时间连续采集的需求,提出了一种基于FPGA和多路标准固态硬盘(SSD)的嵌入式大容量大带宽数据存储系统架构及其优化实现方法。着重分析了标准SSD瞬时写入速率随机性问题,基于实测数据和数学模型提出了一种动态数据调度方法。理论推导和实际测试均表明该方法有效降低了对缓存容量的需求,并提高了系统工作的可靠性。

采集;存储;FPGA;SSD

数据采集存储设备广泛应用于雷达、通信等领域,更高的平均输入带宽、更大的存储容量是其必然发展趋势。随着前端数据采样速率的提升,高速且稳定的数据写入速率也是数据存储系统设计需要着重考虑的问题。

应用于嵌入式环境的数据存储技术已经有大量相关的研究。文献[1]基于Xilinx公司的Virtex-5芯片的高速串行收发器GTX,实现了SATA控制器;文献[2]采用以ARM920T为核心的S3C2410A作为主控器将视频数据进行存储;文献[3]通过FPGA作为主控芯片搭载96片NAND FLASH实现了容量达3TB的存储系统;文献[4]设计了一款由8块SSD硬盘组成的存储阵列,并使用并行存储方式实现大容量高速固态存储。

基于调研工作,文中提了出一种嵌入式大容量大带宽数据存储系统架构,采用现场可编程门阵列(FPGA)为控制核心,并发操作多路标准固态硬盘(SSD)。与其他架构相比,具有带宽高、容量大、成本低和可靠性强等优点。但是由于标准SSD的坏块管理、垃圾回收等操作会对瞬时写入速率造成一定影响,进而影响整个系统的性能。针对该问题,本文在实测和建模分析的基础上提出了一种优化的动态数据调度方法,有效降低了对缓存容量的需求,提高了整个系统的工作效率与可靠性。

1 系统架构

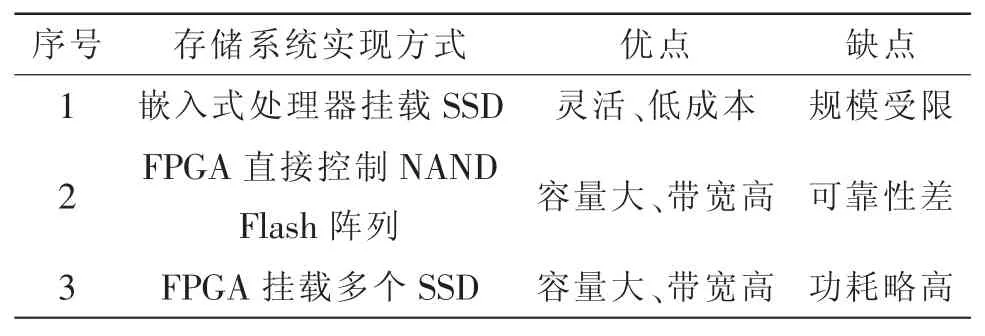

经过调研工作,表1总结了实现高速大容量嵌入式数据存储系统的3种架构方式。

方式1具有低功耗、低成本的优点,使用嵌入式处理器控制能力也较强,但是由于嵌入式处理器结构的固定性,此类系统的扩展性不强,规模有限[5-6];方式2具有带宽高、容量大的特点,但是此类系统使用FPGA芯片作为主控芯片对NAND Flash进行控制,NAND Flash的管理操作,尤其是坏块管理和数据纠错,都需要FPGA逻辑来实现,其完善程度很难和SSD中基于ARM处理器的专用Flash控制器媲美,往往存在可靠性问题[7];方式3同样具有容量大、带宽高的特点,但是如果数据存储方式选择不当,易造成实时性、灵活性不佳的问题[8]。

表1 大容量存储系统实现方式

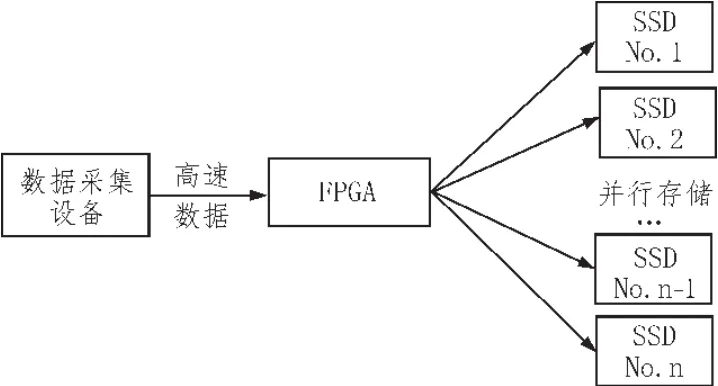

基于以上调研工作,结合本系统超宽带、超大容量的特点,最终选用以FPGA为控制核心,并发操作多路标准固态硬盘(SSD)作为系统的实现架构[9-12],具体结构框图如图1所示。

图1 宽带信号采集系统结构框图

系统如此设计具有以下优势:

1)SSD自带专用Flash控制器。具备自动处理坏块管理、垃圾回收等能力,FPGA仅需实现与多块SSD的通信工作即可,如此既方便了设计工作,也节省了资源消耗;

2)灵活性高。使用过程中如果发现某块盘有损坏的情况,直接更换即可;如果以后出现更高容量的SSD,仅需直接替换就可以使整个系统的容量成倍增长;

3)多个SSD并行存储,写入速率成倍增加。FPGA可以控制n块SSD同时并行写入,整个系统的写入速率理论上可以达到单块SSD写入速率的n倍。

但是,由于SSD存在写入速率随机性的问题,为了满足宽带信号采集系统的实时性,在系统实现设计上需要对此问题着重考虑[13-15]。

2 系统实时性问题及其解决

前期测试时发现,在持续给SSD写入数据的过程中,SSD会出现写入速率不稳定的现象,具体表现为写入操作随机出现短暂的停滞。虽然在设计初期考虑到加入数据缓存模块,但是在超宽带数据输入的情况下,也有可能出现数据丢失的现象,系统实时性无法得到满足。因此,本节对SSD速率随机性问题进行详尽的测试,并根据宽带采集系统对实时性的要求提出一种动态数据调度算法,通过理论推导验证了该算法对于数据缓存容量需求的降低以及系统稳定性的提高有显著效果。

2.1 SSD的速率随机性问题

首先,基于FPGA实现SATA协议,并完成了与单块SSD的通信,之后对SSD进行持续写入测试。由于单块SSD的写入速率在240 MB/s左右,为了充分测试SSD写入速率的随机性,编写数据产生模块,通过FPGA持续向SSD写入速率为300 MB/s的数据流,使SSD一直处于写饱和的状态;通过FPGA观察相关信号,统计SSD处于不能写入状态的最长时间,为宽带信号采集系统的数据存储方式设计提供参考依据。

基于上述测试环境,对当前市面上主流的5款SSD进行充分测试,结果如表2所示。

表2 SSD写入速率随机性测试结果

通过测试结果可以发现,单块SSD的最长无法写入状态持续时间可以达到秒级,不同型号的SSD所表现出的写入速率随机性略有不同。出现此特性的根本原因是SSD的Flash控制器在做垃圾回收等工作时会对写入速率造成一定的影响,而不同厂家使用不同的控制器,因此表现出来的写入速率随机特性也会有一定差别。

基于上述测试结果,对于宽带信号采集系统的存储阵列进行分析。宽带信号采集系统的最高数据写入带宽可以达到GB/s,使用传统并行数据存储方式,如果采集过程中一旦某一块盘处于无法写入的状态,整个系统的数据写入操作停滞;如果SSD无法写入状态的持续时间达到了秒级,则至少需要GB数量级的缓存模块才能保证数据不丢失;更可怕的是,如果两块或多块SSD连续出现无法写入的现象,则需要更大的数据缓存模块来保证系统的实时性,如此大的数据缓存模块已经无法通过使用FPGA的资源来实现,只能使用专用的数据缓存芯片,但是如此一来不但会增加整个系统的功耗,数据缓存芯片的容量也不好把握。仲裁工作所需的时间很短,所以如果FIFO的数据写入带宽足够大,会很快将所有n块SSD前端的FIFO填满,如此以来,理论上可以达到所有n块盘同时进行数据存储的效果,那么整个系统可以实现n倍于SSD单盘写入速率的系统写入带宽。

图2 数据存储方法示意图

2.2 动态数据调度算法

根据上述分析,基于FPGA开发设计出一套高效、稳定的动态数据调度算法,以满足宽带信号采集系统对于实时性的要求。

2.2.1 数据存储

图2表明了动态数据调度算法在进行数据存储操作时的简要原理。FPGA首先对数据进行打包操作,在每包数据的最前面加入包头信息,记录当前的包号与时间等信息。数据分配模块会根据每块盘的状态信息对所有盘进行优先级仲裁操作,在几个时钟周期内判断出当前包数据该存入的SSD盘号,并将其分配到该盘前端的FIFO当中;之后该包数据从FIFO写入到SSD中,同时下一包数据经过下一次仲裁被分配到另一个SSD所对应的FIFO当中;由于

数据分配模块的仲裁规则如下:

1)选出的盘当前要处于正常可以接收数据的状态;

2)选出的盘当前所存包数量是所有盘中已存包数量最少的一个;

3)相邻两包数据不存储于同一块盘当中。

如此进行优先级仲裁操作,可以使采集到的数据尽量快速、平均地存入当前可以正常工作的SSD中,同时也避免了在采集过程当中某一块或几块盘出现速率突变情况而导致整个系统写入停滞、数据丢失的问题。

2.2.2 数据转存

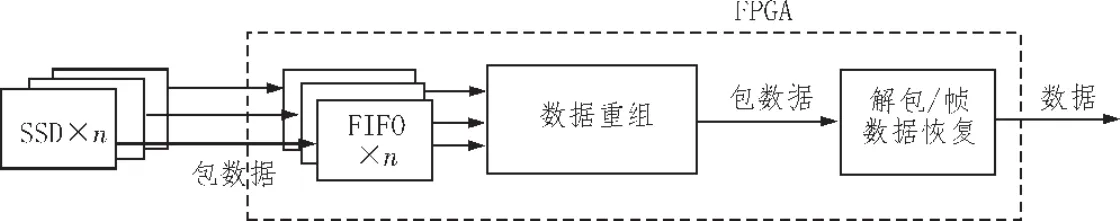

图3 数据转存方法示意图

图3表明了动态数据调度算法在数据转存操作时的简要原理。首先每块SSD逐包将各自存储的数据上传到FPGA中各自对应的FIFO当中,数据重组模块会根据每包数据包头中的包号信息依次将数据拼接并读走,同时SSD将下一包数据送入各自对应的FIFO当中等待下一次数据重组模块的判断,之后数据经过去包头操作,正确、完整地上传到转存设备当中。

如此进行数据转存工作,还可以通过在FPGA当中实现逻辑查找包号,根据需求精确地导出某一包之后的数据,大大增强了整个系统在使用过程当中的灵活性。

2.3 数学模型分析

本节针对宽带信号采集系统并行数据存储方式建立数学模型,比较传统并行数据存储方式与动态数据调度算法所需缓存容量的差异。

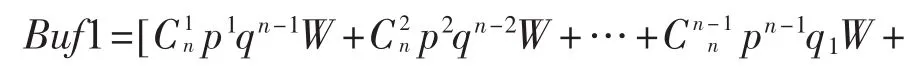

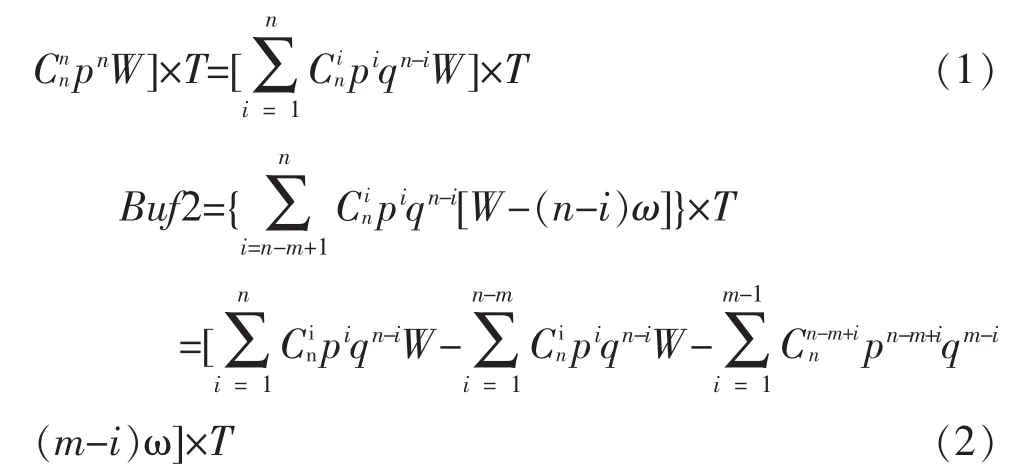

假设单盘SSD出现速率突降的概率为p,q=1-p,系统中共有n块SSD,系统写入数据带宽为W,单盘写入速率为 ω,而且(m-1)ω<W<mω,即至少需要m块盘同时写入才可以满足系统输入的数据带宽。计算在时间T内,传统并行数据存储方式与动态数据调度算法所需要的平均数据缓存容量,Buf1与Buf2,并进行比较。

根据模型分析,采用传统并行数据存储方式,只要有1块盘处于无法写入的状态时,整个系统的数据写入会陷入停滞,此时需要缓存模块来提供整个写入带宽的缓存;而使用动态数据调度算法,当少于m块盘正常,即多于(n-m)块盘处于无法写入状态时才会需要数据缓存模块来缓存数据,而且此时其他的正常盘可以写入数据,提供一定的数据带宽,因此:

通过比较两式可以看出Buf2相对于Buf1减少了后两项,即动态数据调度算法方式相对于传统并行数据存储方式会减少相当一部分数据缓存的使用。

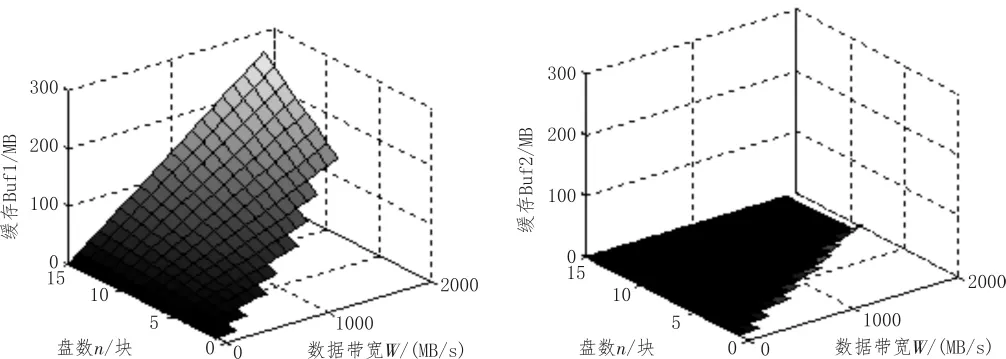

假设SSD出现速率突降的概率p=1%,单盘SSD的写入速率为240 MB/s,定量画图描绘Buf1与Buf2随盘数n与数据带宽W的变化关系:

图4 数据缓存容量对比图

由图4的比较可以看出,随着盘数与数据带宽的增加,传统并行数据存储方式所需的缓存会越来越大,而使用动态数据存储方式需要的缓存容量一直处于非常低并且十分稳定的状态,可见使用动态数据存储方式,有效地降低了整个系统对于数据缓存容量的需求,同时满足系统对实时性的要求,对系统的稳定性也有很大程度的提升。

3 系统实现与测试

3.1 系统硬件环境搭建

基于Xilinx公司的Virtex6FPGA进行硬件程序设计,实现FPGA与15块SSD组成的存储阵列通信,以此搭建硬件环境实现宽带信号采集系统并对动态数据调度算法进行测试。

测试时,在数据源与数据打包模块之间加入数据缓存模块,使用专用DDR3缓存芯片进行数据缓存,可以根据实时监测DDR中的数据深度来观察整个系统实时写入数据的能力。

考虑到测试平台所选FPGA的性能与资源限制,测试时设置每个SATA模块前的缓存FIFO写入时钟频率为150 MHz,FIFO写入位宽为128 bit、深度为两个包长度4 kB,理论上整个系统当前可以满足的最高写入带宽受限于FIFO的数据写入带宽:150 M×128 bit=2.4 GB/s。

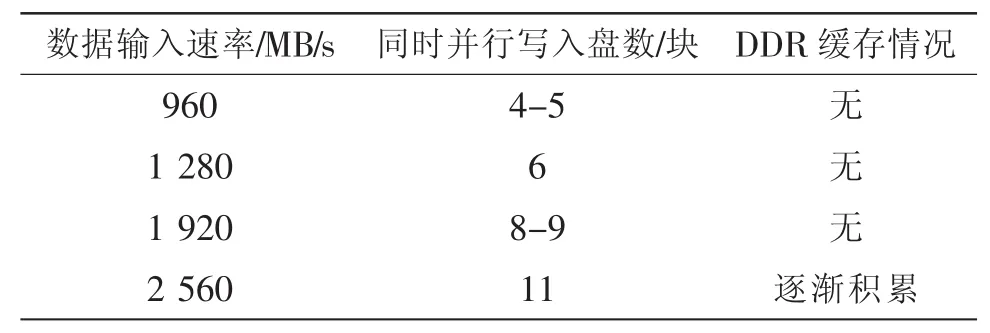

3.2 测试结果

测试时逐渐增加输入数据的带宽,并实时监测DDR中的缓存数据量,观察动态数据调度算法的工作特性,经过长时间的测试工作,得到测试结果如表3所示。

表3 系统性能测试结果

通过以上测试结果可以发现,当输入数据带宽小于2.4 GB/s时,整个存储系统的写入速率稳定,DDR中一直没有缓存数据,说明动态数据存储方式成功地满足了超宽带系统对于实时性的要求,并没有由于某块盘的速率突降现象影响到整个系统的数据写入速率。

当输入数据带宽大于2.4 GB/s时,DDR中的缓存数据逐渐积累,说明此时已经达到了当前系统的极限写入速率,基本符合理论推导值。如果以后需要满足更高带宽的写入速率,可以通过提高FIFO入口数据带宽(时钟或位宽)来进一步提高整个系统所能满足的写入带宽,理论最高带宽为所有15块SSD同时并行写入的速率,可以达到15×240 MB/s=3.6 GB/s。

4 结 论

文中针对超宽带信号长时间连续采集对于存储系统的实时性需求,提出了一种基于FPGA和多路SSD的超宽带、大容量的存储系统架构;针对SSD存在写入速率随机性的缺陷进行详尽的测试与分析,并结合本系统的自身特点,开发出一套高效、稳定的动态数据调度算法,并在测试系统上成功实现,不但节约了FPGA资源与系统功耗,更提高了整个系统的工作效率与使用可靠性。

可以预知随着电子行业的发展,单块SSD容量的增加,本系统的容量可以成倍升级,同时也可以通过增加SSD的个数来扩展整个系统的容量;如果使用更高性能的FPGA,系统最高写入带宽理论上可以提高到所有SSD同时并行写入的速率。因此,本设计具有很大的发展空间与广阔的应用前景。

[1]朱鑫鹏.SATAⅡ设备端IP核的FPGA设计与实现[D].成都:电子科技大学,2011.

[2]李敏.基于ARM+Linux的嵌入式视频监控存储系统[D].西安:西安电子科技大学,2010.

[3]徐玉杰.高速大容量存储系统的设计与实现[D].西安:西安电子科技大学,2014.

[4]范晓星.高速大容量固态存储系统设计与实现[D].西安:西安电子科技大学,2014.

[5]王宗超,马建设,周倩,等.基于ARM和固态硬盘的微型投影嵌入式平台设计[J].重庆理工大学学报:自然科学,2012,26(5):47-50.

[6]王冬星,程书伟,张丽华.基于ARM的数据采集与存储系统的研究与实现 [J].计算机工程与设计,2012,33(12):4526-4530.

[7]吴凡.基于FPGA和NAND Flash的嵌入式存储系统设计[J].电子科技,2016,29(3):97-101.

[8]孟琪.基于SATA接口高速电子存储阵列的设计与实现[D].西安:西安电子科技大学,2014.

[9]王童.基于SATA接口固态硬盘的存储系统的研究与实现[D].西安:西安电子科技大学,2014.

[10]王烨,张峰,李燕斌.SATA高速存储的FPGA实现[J].电讯技术,2012,52(11):1801-1804.

[11]张芬平,王建生.SATA控制器的FPGA实现[J].山西科技,2015,30(6):126-128.

[12]刘明刚,施建礼.基于FPGA高速大容量数据采集与存储系统[J].仪表技术,2014(5):25-27.

[13]SUN Ning-xiao,WU Qiong-zhi,JIN Zhao-jian.A storage architecture for high speed signal processing:Embedding RAID0 on FPGA[J].Journal of Signal and Information Processing,2012(3):382-386.

[14]刘涛.一种基于SSD硬盘缓存加速与备份的RAID设计方法:中国,201310053327.0[P].2013-06-12.

[15]李金猛,周勇军.高速大容量数据存储技术的研究综述[J].测控技术,2016,35(2):1-4.

An optimized method of real-time data recording for wide-band embedded storage system

PENG Cheng-fei,XU Jia-lin,LI Tao,WU Qiong-zhi

(School of Information and Electronic,Beijing Institute of Technology,Beijing 100081,China)

Focusing on the demand of long-term continuous wideband signal acquisition,this paper puts forward an implementation and optimized method of embedded large-capacity and high-bandwidth data storage system architecture based on FPGA and multi-channel SSDs.In this paper,the random instantaneous speed problem of SSD writing is analyzed emphatically,and a dynamic scheduling method is put forward based on the test data and mathematical model.Theoretical analysis and practical tests both indicate that this method reduces the need of data buffer effectively and improves the reliability of the system.

signal acquisition;storage;FPGA;SSD

TN957.52

A

1674-6236(2017)17-0115-05

2016-07-01稿件编号:201607005

彭程飞(1991—),男,辽宁锦州人,硕士研究生。研究方向:复杂电路系统研究与应用。