基于FPGA和LVDS的弹载数据回读系统设计*

2017-09-06赵阳刚郭涛黄玉岗

赵阳刚,郭涛,黄玉岗

(中北大学电子测试技术国防科技重点实验室,太原030051)

基于FPGA和LVDS的弹载数据回读系统设计*

赵阳刚,郭涛*,黄玉岗

(中北大学电子测试技术国防科技重点实验室,太原030051)

针对弹载数据回读过程中,并行数据传输难以同时钟完全同步,且并行电缆线之间的相互串扰等问题,造成并行数据回读电缆长度一般限制在几十厘米,因此设计了一种基于FPGA和LVDS的弹载数据回读系统。以FPGA作为控制核心,以FT245BL作为USB控制芯片,采用低压差分信号技术接口解串和驱动芯片相结合,保证了数据有效的远程收发。试验表明,回读系统能够很好地完成数据传输工作,且数据传输迅速、准确,无错帧与丢帧现象,具有一定的工程应用价值。

数据传输;FPGA;LVDS;USB

当前武器库中,绝大多数的常规炮弹尚未采用制导控制,命中率较低,将微惯性测量器件用于常规弹上进行惯性制导与控制,可极大地提高炮弹的命中率[1-2]。由于常规炮弹一般飞行时间很短,并且考虑到安全性和隐蔽性等因素,炮弹在飞行过程中的动态参量不可能实时地传输到上位机进行处理与显示。通常会将传感器采集的数据存储到数据记录系统中的FLASH中,回收后通过对存储器中的数据回读到上位机,分析、处理进而解算炮弹的飞行弹道及所需参量[3]。

传统的数据回读系统一般采用并行方式直接回读到上位机,由于并行数据传输距离的限制,在炮弹发射前的测试和事后回读过程中很不方便,因此需要一种传输可靠、速率高、功耗低的数据传输方式。低压差分信号技术LVDS(Low Voltage Differential Signaling)使用极低的摆幅通过双绞电缆传输数据,是一种最高传输速率可达1.923 Gbit/s的通用接口技术,并且由于其低压差分的传输方式,具有较强的抑制信号干扰功能,大大提高了数据传输的距离、速率和可靠性[4-6]。

1 系统组成和各模块设计

系统设计目标是数据在3m以上的同轴电缆上稳定可靠的回读。根据设计的需求和方案的合理性,命令和数据分开传输,命令传输采用RS-422差分信号,数据传输采用LVDS信号。

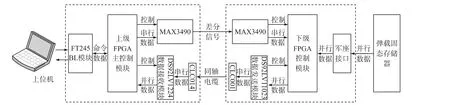

本系统主要有电源模块、FPGA控制模块、LVDS接口模块、FT245BL模块构成,主要实现对弹载固态存储器的数据回读和擦除。上位机通过FT245BL将命令发送到上级FPGA主控模块,然后通过MAX3490将TTL信号转换成RS-422信号传输到下级FPGA模块,下级FPGA模块对弹载固态存储器执行相应的操作。当执行数据回读时,下级FPGA将固态存储器中的数据回读到内部的FIFO中,当FIFO中数据半满后,通过信号标志位通知FPGA可以将数据发送给LVDS芯片,并行数据在LVDS发送端通过串行器DS92LV1023完成数据的并转串,数据传输过程中通过CLC001/CLC014驱动器/均衡器减小信号的衰减和增加数据的传输能力,实现数据高速稳定的传输。在接收端通过解串器DS92LV1224完成数据的串并转化。然后上级FPGA对接收到的并行数据处理后,传输到上位机中进行处理。

图1 系统总体设计框图

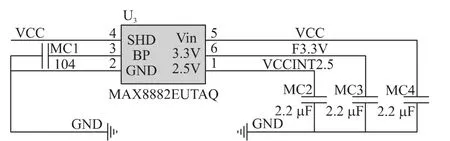

1.1 电源模块

电源模块为整个系统提供正常工作电压。考虑到整个系统的电压的需求有5 V、3.3 V、2.5 V,系统主供电采用USB自供电模式,供电电压为5 V,供电电流最大为500mA,5 V电压为均衡器CLC014提供正常工作电压;然后选用MAXIM公司生产的高功率、高性能、低功耗和低噪声的电压转换芯片MAX8882EUTAQ,该芯片可将2.5 V~6.5 V输入范围内的电压转换为标准的3.3 V和2.5 V电压,3.3 V和

2.5 V为FPGA和LVDS等芯片提供工作电压。

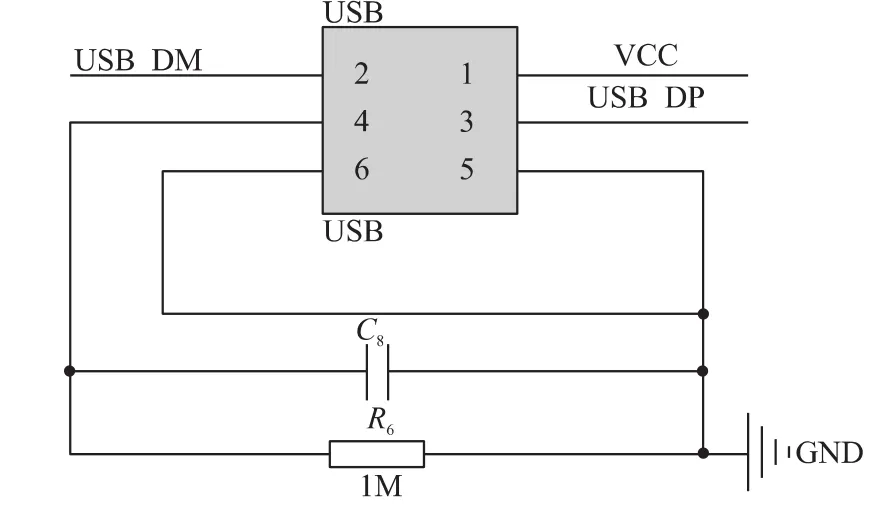

为了防止数据读取过程中,插拔对USB芯片造成的损伤,在电路中接入大的电阻和电容,保护USB芯片,USB供电电路如图3所示。

图2 MAX8882EUTAQ电源转换模块

图3 USB供电模块

1.2 FPGA控制模块

本系统选用两个XILINX公司的XC2S30作为控制芯片,FPGA具有高速、低功耗、高集成度等特点,而且内部集成了6个双口RAM共24 kbit的存储空间,可以开辟成内部FIFO实现数据的缓存,保证数据传输的完整性。上级FPGA作为主控制器,当接收到上位机发送的控制指令时,可以根据通信协议对下级FPGA进行相应的操作;当下级FPGA向上发送回读数据时,上级FPGA对数据进行处理后传输到上位机进行存储、分离等操作。

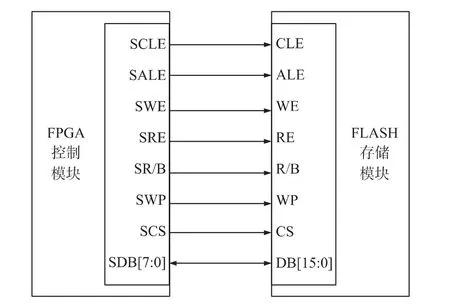

图4 下级FPGA对弹载固态存储器的控制

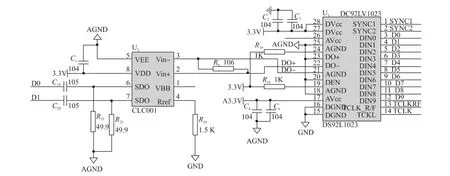

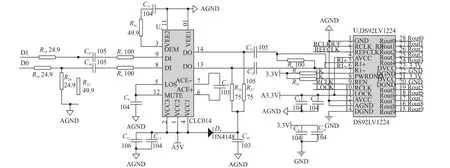

1.3 LVDS接口模块

DS92LV1023和DS92LV1224是美国国家半导体公司生产的10 bit总线型低压差分信号芯片组,其有3种主动工作状态分别为初始化、数据传输和再同步以及两种被动工作状态省电和三态。其中,DS92LV1023为串化器可将10 bit并行的CMOS或TTL数据转换为具有内嵌时钟的高速串行差分数据流;DS92LV1224为解串器可以将接收的差分数据流转换为并行的数据,而且可以从串行的数据流中重建并行时钟。通过内嵌的时钟可以很好的解决时钟与数据不严格同步而造成的高速传输的瓶颈问题[7-8]。

高速驱动器CLC001和自适应均衡器CLC014配合使用,可以保证信号稳定长距离的传输,而且可以补偿信号在电缆上传输过程中出现的衰减,保证数据传输的正确性和完整性[9]。

LVDS接收电路如图6所示,解串器DS92LV1224接收到串行数据后,从中重建出内嵌的时钟RCLK。为了使解串器的PLL(锁相环)必须同步到串行器(即锁定串行器输出的时钟),需要先给解串器提供一个与串行时钟TCLK频率相同的参考时钟REFCLK。最终数据在解串器恢复成十路并行数据,并在RCLK的时钟下降沿将数据传输给FPGA,对数据进行相应的处理。

图5 LVDS数据发送模块

图6 LVDS数据接收模块

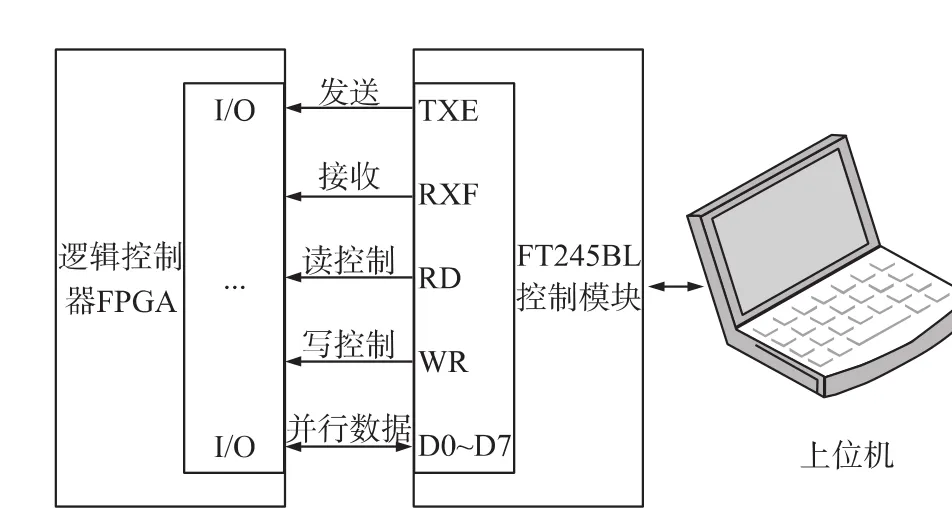

1.4 FT245BL模块

图7 FT245BL接口图

FT245BL芯片为FTDI公司的第2代USB接口芯片,比传统的USB接口设计简单,开发周期短,而且芯片内部有384 byte的发送缓冲区和128 byte的接收缓冲区,芯片上有完整的USB协议,不需要复杂的固件程序配置,并且FTDI公司为用户提供了驱动程序。

2 系统逻辑设计与软件设计

2.1 FPGA控制模块逻辑设计

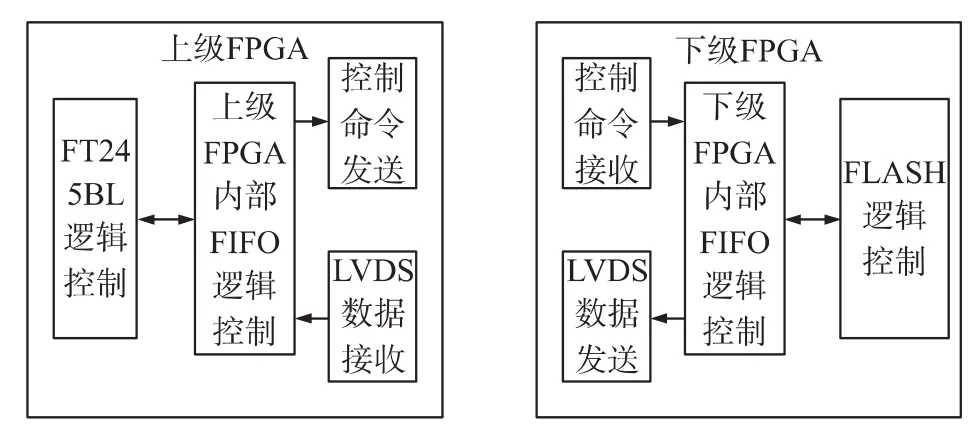

2.1.1 FPGA内部组成及框图

FPGA控制模块包括上级FPGA和下级FPGA模块,上级FPGA主要是接收和发送上位机传送的命令,并对下级FPGA发送来的数据处理上传的;下级FPGA主要实现对弹载固态存储器中的数据回读并上传,FPGA内部组成框图如图8所示。

图8 FPGA内部组成框图

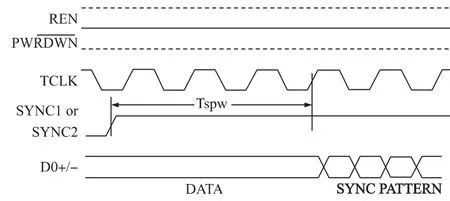

FPGA根据LVDS的时序控制DS92LV1023模块进行数据发送,在程序中定义TCLK的上升沿为发送时钟有效沿,当发送使能处于有效状态且串行器和解串器时钟同步后,下级FPGA将读取的弹载固态存储器中的数据处理后,在发送时钟的有效沿依次向外发送。数据发送模块时序图如图9所示。

图9 数据发送模块时序图

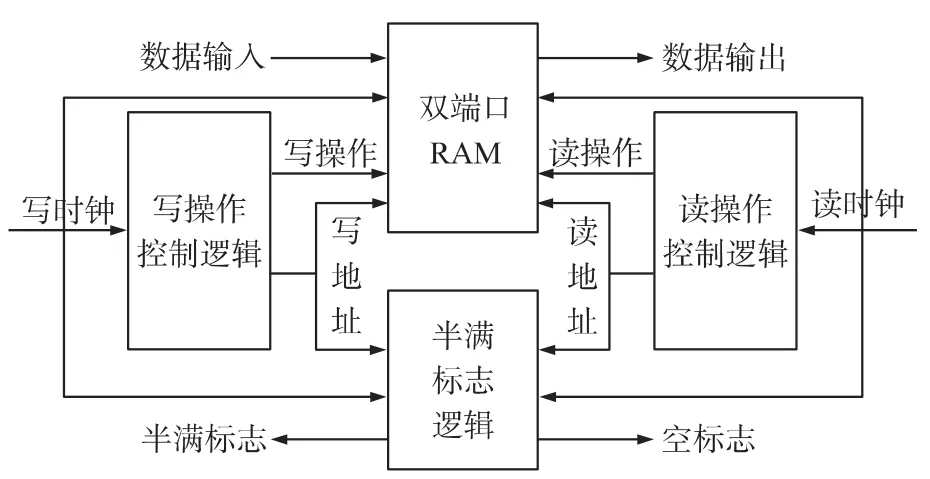

2.1.2 FPGA内部FIFO逻辑设计

本文在两级FPGA控制模块内部都开辟了位宽8 bit深度1 K的FIFO缓存模块,保证数据传输的完整性[10-11]。在设计过程中,通过读地址和写地址的差值判断FIFO的存储状态,在读取FIFO中数据之前,先对当前FIFO中已存储数据量多少进行判断。当FIFO中数据量半满后,数据可以进行读取操作。

图10 异步FIFO工作逻辑框图

2.2 系统上位机软件设计

2.2.1 通信协议

上位机在未发送操作命令时,上级FPGA处于等待状态。当接收到握手协议时,握手协议以16进制编写,FPGA将16进制的协议转换为2进制识别,根据事先规定好的通信协议,上级FPGA对下级FPGA进行相应的操作[12-13]。系统和上位机规定的握手协议:

读数命令:&17&3E&33&A3

停止读数命令:&17&3E&44&A4

擦除命令:&17&3E&55&A5

2.2.2 上位机软件设计

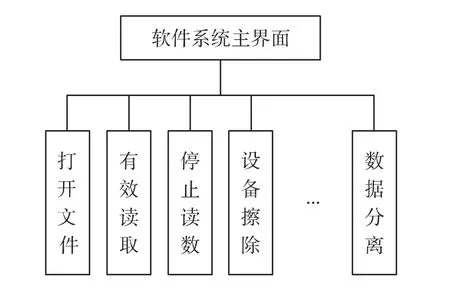

上位机软件采用VB程序开发,软件操作界面包括有效读取、停止读数、设备擦除、数据处理等。有效数据读取完后可以擦除弹载固态存储器中的数据,便于弹载测试系统再次使用;数据分离便于后续处理。系统处理软件设计的结构图如图11所示。

图11 系统处理软件设计的结构图

图12 上位机软件

3 系统验证

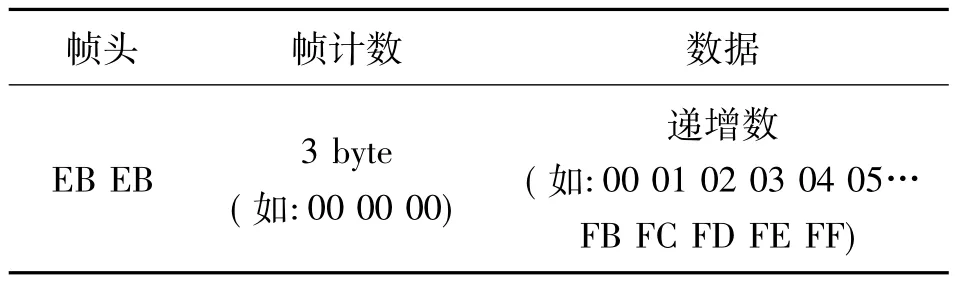

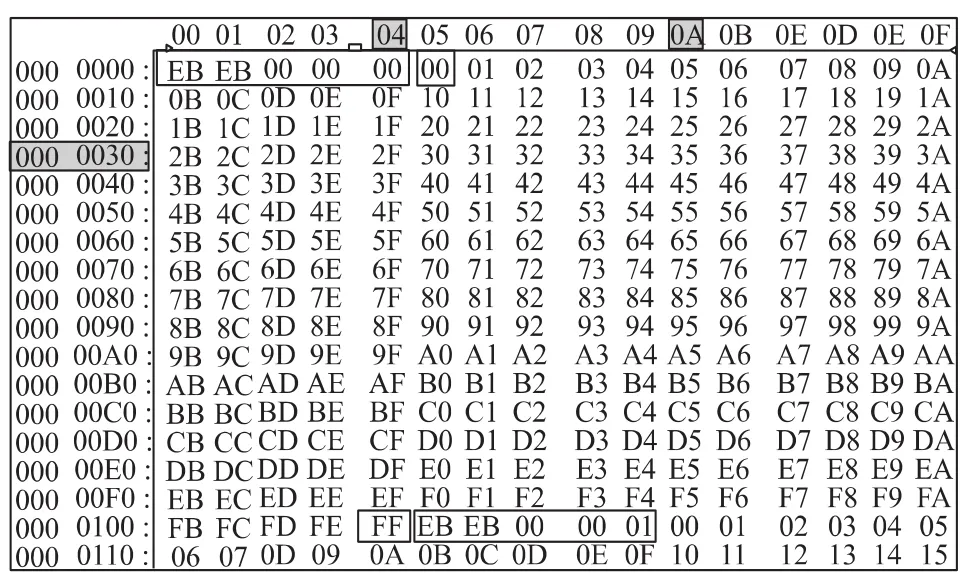

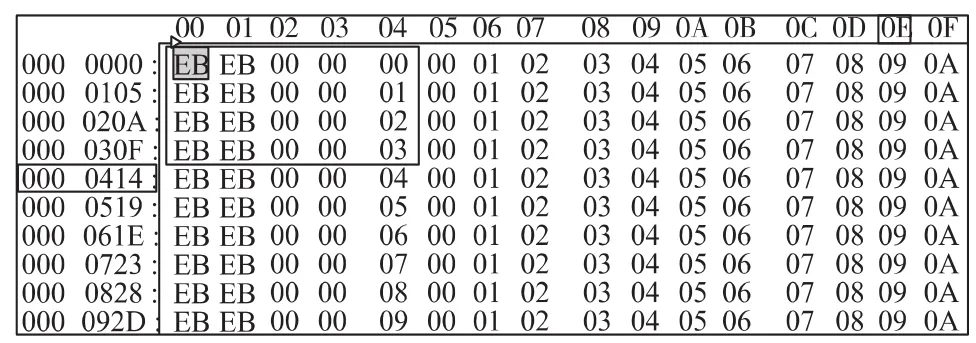

为验证所设计的系统是否可以在3 m以上的距离可靠正确的回读弹载固态存储器内的数据。在实验室中将上位机、弹载数据回读系统以及弹载固态存储装置放置在实验台上,模拟系统回收后对数据进行操作的环境。利用实验室的仪器设备,向弹载固态存储器内写入一组递增数,然后用所设计的系统将数据回读到上位机中进行验证,递增数格式如表1所示。

表1 预先写入固态存储器内递增数数帧格式

根据实际需要,系统同轴电缆的长度设置为3 m,然后用弹载数据回读系统将预先写入弹载固态存储器的数据回读到上位机中显示,显示结果的部分截图如图13所示,第1个、第2个字节为数据的帧头,第3个~第5个字节为帧计数,第6个~第261个字节为递增数。将上位机中的数据按每行261列显示,对数据进行分析可知,帧头并未错位,帧计数连续递增,递增数并未出现丢数、错数、漏数情况出现,如图13所示。因此,说明设计的弹载数据回读系统的完整性和可靠性。

图13 递增数显示结果

图14 帧计数递增结果

4 结论

本文设计了一种基于FPGA和LVDS的的弹载数据回读系统,系统选用可编程能力强FPGA作为核心控制器,并在FPGA内部开辟了FIFO作为缓存,保证了数据在系统中传输的完整性;采用LVDS芯片和驱动芯片配合,有效的保证了数据的接收和发送并且解决了并行数据传输距离短的不足。选用FTDI公司的第2代FT245BL芯片实现与上位机间的通信,设计简单。试验结果表明,所设计的的系统正确、可靠和实用性强,有一定的工程应用价值。

[1]刘俊,石云波,李杰.微惯性技术[M].北京:电子工业出版社,2005:1-78.

[2]董进龙,莫波.典型弹道下的火箭弹MEMS-INS/GNSS组合导航姿态误差可观性分析[J].兵工学报,2014,3(56):850-856.

[3]郝晓明,李杰,石玺文,等.基于FPGA的弹载数据回读系统设计[J].传感技术学报,2015,7(28):1023-1027.

[4]彭乡琳.LVDS在长距离信号传输中的应用[J].兵工自动化,2006,25(7):60-61.

[5]马志刚,朱思敏,刘文怡.基于LVDS的高速图像数据存储系统设计[J].数据采集与处理,2013,28(3):382-385.

[6]赵秋明,王龙飞,翟江辉.基于LVDS技术的高速数据传输系统设计[J].计算机测量与控制,2012,20(11):3035-3037.

[7]DS92LV1023 40-66 MHz 10 Bit Bus LVDS Serializer.National Semiconductor Corporation[Z].2005.04.

[8]DS92LV1224 30-66 MHz 10 Bit Bus LVDSDeserializer.National Semiconductor Corporation[Z].2005.04.

[9]杨翠虹,文丰,姚宗.基于LVDS的高速数据传输系统的设计[J].通信技术,2010,43(9):59-61.

[10]张松,李杰,赵诣,等.半捷联MEMS惯性测量装置数据硬回收系统设计[J].传感技术学报,2013,26(9):1219-1223.

[11]胡陈君.弹载小型抗高过载微惯性测量系统设计[D].太原:中北大学,2015.

[12]黄土琛,宫辉,邵贝贝.基于USB和FPGA的多功能数据采集系统[J].原子能科学技术,2013,47(11):2172-2176.

[13]柯艳,李杰,孔祥雷,等.基于USB 2.0的多路数据采集系统上位机软件设计[J].测试技术学报,2010,24(4):351-356.

赵阳刚(1991-),男,现在中北大学读硕士研究生,主要研究方向为惯性测量系统、智能家居系统,1005801167@qq.com;

郭涛(1971-),男,教授,硕士,现在中北大学电子测试技术国家重点实验室工作,主要研究方向为惯性测量系统、微器件的设计与制造,guotao6@nuc.edu.cn;

黄玉岗(1988-),男,河北沧州人,现在中北大学读硕士研究生,主要从事微系统集成、惯性测量方向的研究,hyg34217 @163.com。

Designing of Readout System for M issile-Loaded Data Based on FPGA and LVDS*

ZHAO Yanggang,GUO Tao*,HUANG Yugang

(Science and Technology on Electronic Test and Measurement Laboratory,North University of China,Taiyuan 030051,China)

For on-board data back to the reading process,the parallel data transmission is difficult to complete synchronization clock at the same time,and the interaction between the parallel cable crosstalks,caused the parallel data read back cable length is generally limited to a few centimeters,so itneeds to design a readout system formissileloaded data based on FPGA and LVDS.The system designed the FPGA as the core,used the FT245BL as the control chip of USB,and adopted the LVDS technique that combined interface solution string and the drive chip.The combination of effective remote data transceiver.Experiments show that the data reading system can complete data remote transmission quickly and accurately without frame error or frame losing and has engineering practical value.

data transmission;FPGA;LVDS;USB

C:1265A;6210

10.3969/j.issn.1005-9490.2017.01.022

TN108.7

:A

:1005-9490(2017)01-0113-05

项目来源:国家自然科学基金项目(50930009,51075394)

2016-01-24修改日期:2016-02-29