基于FPGA的线阵型CCD驱动电路设计*

2017-09-06程瑶周娜王荣秀

程瑶,周娜,王荣秀

(1.重庆理工大学机械工程学院,重庆400050;2.重庆工商大学,重庆400067)

基于FPGA的线阵型CCD驱动电路设计*

程瑶1*,周娜1,王荣秀2

(1.重庆理工大学机械工程学院,重庆400050;2.重庆工商大学,重庆400067)

CCD驱动电路的设计是实现CCD各种设计功能的关键性因素,只有对其驱动信号设计的严格把关,才会进一步保证CCD器件后续工作的开展。分析线阵CCD器件TCD1703C的驱动时序要求,采用QuartusⅡ软件,选用Verilog HDL语言设计了各路驱动时序信号。将程序设计下载到FPGA器件中,通过逻辑分析仪对输出信号进行了波形监测,验证了线阵CCD的驱动时序设计的可行性。将产生的驱动时序信号接入CCD器件,不同光照入射的条件下,CCD在驱动信号的驱动下,正常工作并输出了相应的视频信号。

CCD;驱动电路;FPGA;QuartusⅡ;Verilog HDL

CCD图像传感器是利用光电转换原理将图像信号转变为电信号,在各领域都得到了广泛的应用,备受人们的广泛关注[1]。CCD器件正常工作的前提是CCD驱动电路中各驱动脉冲的严格性设计。CCD的工作状态与其驱动时序密切相关。只有在严格满足驱动时序要求的基础上,CCD的转换效率、信噪比、光电转换特性等指标才能达到最佳状态[2]。这些驱动信号提供CCD正常工作的驱动时序,也可以在后续的信号处理电路中提供一些控制性信号,更可以在图像采集处理过程中提供同步信号。

因此驱动时序电路的设计是CCD器件应用的关键性因素[3]。驱动时序电路的设计重点又落脚到各个驱动信号的高低电平时间周期性的控制设计。只有对其驱动信号设计的严格把关,才会进一步保证CCD器件后续工作。CCD中各个像元对不同强度的光产生不同的模拟电荷信号,在FPGA产生的驱动时序作用下,CCD才能将模拟电荷信号串行移位输出[4]。

1 CCD驱动电路的设计方法

CCD驱动时序设计方法并不单一,不管是线阵还是面阵的CCD,它们的驱动时序都是具有周期性的特定电压电平信号。CCD的驱动时序产生方法主要有以下4种:直接数字电路(IC)驱动法、单片机驱动法、EPROM驱动法、可编程逻辑器件法等[5]。

近些年来,随着可编程器件的高速发展,FPGA因其高速并行处理方式,极强的编程灵活性,十分适合用来产生CCD的驱动时序[6]。FPGA是一种可以根据用户的自我需要自行改造相应逻辑功能的数字集成电路。利用FPGA器件设计驱动电路,可以大大缩减电路板的制作成本(需要体积小),无需外部芯片,提供软件仿真功能,适合完成各种算法和组合逻辑,可靠性以及灵活性都比较高,重新修改原理图或硬件描述语言即可完善设计。同时还可以为图像信号的采集提供时钟以及其他电路的时序匹配[7]。因此本文采用FPGA驱动法进行线阵CCD驱动时序信号的设计中,选用Verilog HDL语言对时序发生器进行了硬件描述以及QuartusⅡ软件对时序进行了功能仿真。

2 线阵CCD驱动电路的设计

2.1 TCD1703C线阵CCD驱动时序要求

TCD1703C是一款敏感度较高、暗电流较小的7500元线阵CCD图像传感器。它是典型的奇偶双沟道转移并行输出的二相CCD。主要用于图像扫描、字符识别以及复制,特别适用于检测高速运动物体图像。TCD1703C结构原理图如图1所示。CCD的驱动脉冲波形图如图2所示。TCD1703C的驱动信号由5路脉冲构成,CCD驱动电路产生的转移信号、传输信号、采样保持信号和复位信号等[8]保证CCD器件正常工作。

图1 TCD1703C结构原理图

图2 TCD1703C驱动脉冲波形图

TCD1703C的光积分时间为两个SH的脉冲间隔。电荷转移需要的时间是SH脉宽的长度,实现存储电荷转移到模拟移位寄存器的功能。Ф1E、Ф2E使得模拟移位寄存器的电荷信号移动并且输出,在转移脉冲处在高电平及上升沿、下降沿这些期间时这两个脉冲必须是反向的。RS为复位信号,复位一次即向外输出一个信号,时序设计中CP的相位较RS稍落后。并且SH为高电平时RS要保持在低电位。该线阵CCD先输出127个哑元,接着才输出7 500个有效像元,紧接着再输出23个哑元,最后输出空驱动信号(空驱动的个数是可以任意的)。

2.2 TCD1703C驱动电路程序设计

依据TCD1703C的驱动时序要求,设计时选用时钟clk频率为10 MHz,Ф1E,Ф2E,RS,CP频率均为1 MHz(周期为1μs),所以需要对时钟clk进行10分频计数。由此也可计算得到初始阶段SH为16个clk周期,Ф1E/Ф2E为26个clk周期,RS以及CP为20个clk周期。

程序设计说明:①SH初始阶段的高电平时间段选用count值为(11~26)之间,CCD驱动剩下的周期内都为低电平;②Ф1E/Ф2E初始阶段的高/低电平时间段选用count值为(5~30)之间,并且在该驱动脉冲中占空比值为1∶1(例:计数值段为(31~35)边界内设置为低电平,计数值段为(36~40)边界内设置为高电平);③RS初始阶段的低电平时间段选用count值为(6~25)之间,CP初始阶段的低电平时间要比RS落后一点,所以选用count值为(7~26)之间,两者的占空比设置为3∶7。

程序设计采用Verilog HDL语言进行描述,各路驱动信号时序图的产生主要通过5个always进程来实现[9-11]。在程序设计中有一个计数器count,TCD1703C虽然有7 500个像元输出但是是通过奇、偶移位寄存器来实现输出的,势必脉冲数的个数相应就可以减少一半,加上是对时钟clk的10分频计数,最终选定count=38 300作为CCD的完整的一次图像转换输出5路驱动信号进程的流程图如图3所示。

图3 TCD1703C驱动信号的程序设计流程图

2.3 驱动电路设计结果

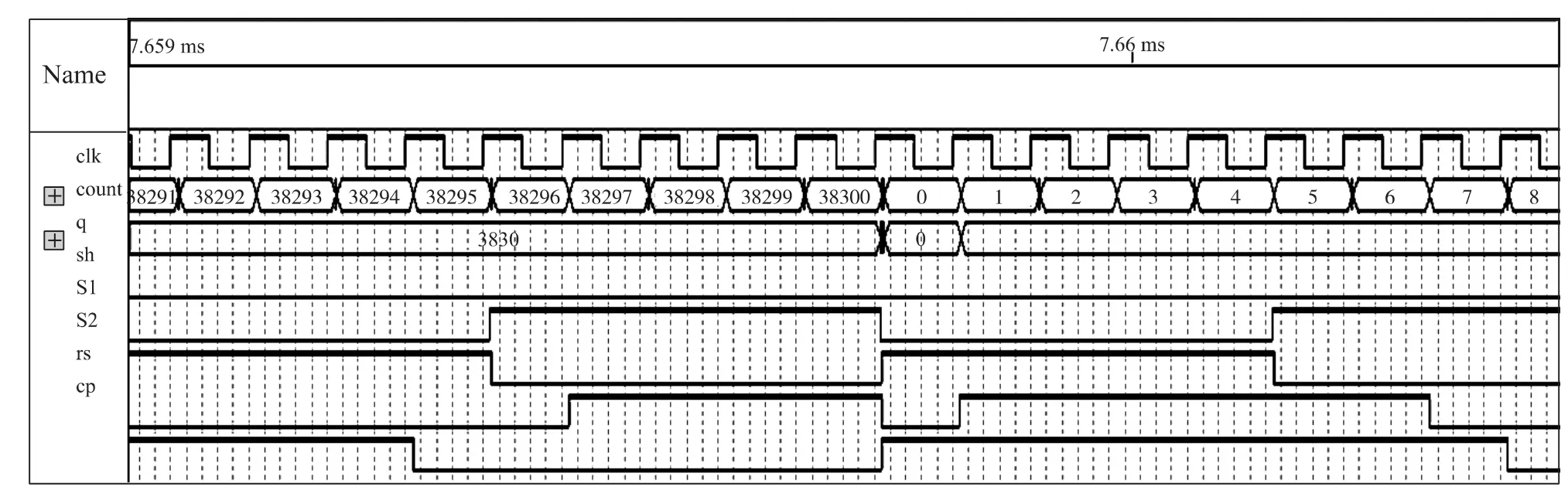

采用QuartusⅡ软件对驱动时序发生器进行了功能仿真。仿真结果如图4~图6所示。

从仿真结果来看,设计产生的5路驱动信号符合TCD1703C的驱动信号要求,从理论验证了该设计方案的可实施性。将输入输出信号进行引脚绑定之后,并通过JTAG下载光缆将程序“烧写”入实际的FPGA硬件芯片中,采用逻辑分析仪进行观察,波形输出如图7、图8所示,与仿真结果一致。

图4 驱动电路总体波形图

图5 驱动电路起始部分信号波形图

图6 驱动电路感光结束部分信号波形图

图7 感光阶段各驱动脉冲信号输出波形

图8 仿真的总体波形

逻辑分析仪观察结果,SH的高电平时间是较于Ф1E、Ф2E驱动信号高/低电平的中间,CP的相位较RS稍落后,并且SH保持在高电平时RS保持在低电平。从波形中可观察Ф1E、Ф2E、RS以及CP的周期是一致的,并且当RS处于下降沿时CP恰好处于上升沿。在一个SH周期内Ф1E、Ф2E、RS以及CP的脉冲个数是大于3 825的。由此可见各信号驱动时序是符合要求的。

3 硬件试验结果

利用FPGA设计产生的驱动信号,引入到TCD1703图像传感器的驱动输入端。将CCD的输出信号引脚连接到示波器观察。采用不同强度的光来观察示波器中采集到的TCD1703的输出波形的变化。

利用黑布将传感器表面接受光强的地方完全遮蔽住,然后将黑布沿一定的方向慢慢地从传感器上移开每次曝光其五分之一,直至该传感器全曝光,5个过程示波器观察的结果如图9(a)~图9(e)。通过实验可以观察到,一旦到达工作电压值,CCD在驱动信号的驱动下输出正常视频信号。随着光强的增加,CCD输出信号的幅度增加,直到饱和。同时验证了驱动电路设计的正确性,CCD在驱动时序电路的作用下,正确地输出了信号。

图9 不同光照强度下CCD的输出波形

[1]米本和也.CCD/CMOS图像传感器基础与应用[M].北京:科学出版社,2006:●-●.

[2]王磊,童子权.基于CPLD的面阵CCD驱动电路的设计[J].仪表技术与传感器,2010(10):66-82.

[3]谭露雯,李景镇,陆小微,等.基于CPLD工作模式可调的线阵CCD驱动电路设计[J].光子学报,2010,39(3):436-440.

[4]冉峰,黄舒平,杨辉.图像采集系统的面阵CCD驱动电路设计[J].电子技术应用,2009(11):43-45.

[5]周根荣,姜平.一种基于高速超微型单片机的CCD驱动电路设计[J].电子技术应用,2006,32(3):105-107.

[6]张林,李永新,高云山.基于IL-P3的高速CCD驱动电路的设计与实现[J].电子器件,2007,30(3):819-822.

[7]姬先举,温志渝.基于CPLD的光积分时间可调线阵CCD驱动电路设计[J].传感技术学报,2006,19(5):1781-1784.

[8]张亮,刘润民.可配置的通用线阵CCD驱动电路的研究与设计[J].电子技术应用,2013,39(12):55-60.

[9]彭晓钧,何平安,袁炳夏,等.基于CPLD的线阵CCD驱动电路设计和实现[J].光电子·激光,2007,18(7):803-807.

[10]孔渊,王世勇,崔洪洲,等.基于CPLD的面阵CCD驱动电路设计[J].半导体光电,2003,24(5):363-59.

[11]顾一,叶炜等.基于CPLD的CCD驱动时序发生器设计[J].光学仪器,2008,30(6):54-59.

程瑶(1981-),女,汉族,重庆江津,重庆理工大学,副教授,主要从事红外图像、嵌入式系统等的研究,chy_cqit @cqut.edu.cn。

Driving Circuit Designing of Linear Array CCD Based on FPGA*

CHENG Yao1*,ZHOU Na1,WANG Rongxiu2

(1.College of Mechanical Engineering,Chongqing University of Technology,Chongqing 400050,China; 2.Chong qing T&B University,Chongqing 400067,China)

The design of driving circuits is a crucial factor to realize the various design features.Only with the strict driving signals desiging,the CCD devices can perform the further work.The TCD1703C driver timing requirements for linear array CCD device were analyzed.And the driving signalswere designed by using QuartusⅡsoftware and Verilog HDL.The program was downloaded to the FPGA device,and the output signals’waveformsweremonitored by the logic analyzer.So the feasibility of the time sequence design of linear array CCD was verified.Finally,connecting the driving signals to the CCD device,the CCD was driven by the driving signals,and the corresponding video signal was output under the different illumination conditions.

CCD;Driving circuit;FPGA;QuartusⅡ;Verilog HDL

C:7230

10.3969/j.issn.1005-9490.2017.01.016

TN386.5

:A

:1005-9490(2017)01-0082-05

项目来源:国家自然科学基金项目(51505052,51505053);重庆市科委基础与前沿研究一般项目(cstc2016jcyjA0497);重庆市教委科学技术研究项目(KJ1500935,KJ1500931,KJ1500617)

2016-01-21修改日期:2016-02-29