多通道并行TD-LTE小区搜索架构设计与FPGA实现

2017-08-16江宇航

蒋 青,卢 伟,江宇航,魏 珊

(重庆邮电大学 重庆市移动通信技术重点实验室,重庆 400065)

多通道并行TD-LTE小区搜索架构设计与FPGA实现

蒋 青,卢 伟,江宇航,魏 珊

(重庆邮电大学 重庆市移动通信技术重点实验室,重庆 400065)

移动终端通过小区搜索完成与网络的接入工作。为了更快地完成时分长期演进 (time division long term evolution,TD-LTE)系统小区搜索过程,与传统数字信号处理(digital signal processing,DSP)串行模式对比,从速度和面积两方面综合考虑,提出一种基于现场可编程门阵列(field programmable gate array,FPGA)的多通道并行小区搜索架构。主要工作集中在小区搜索整体方案设计和FPGA硬件实现上,在算法上对整个小区搜索算法架构进行了改进,同时根据硬件需求,利用以时钟换取速度的思想对FPGA硬件实现架构进行了优化。采用多通道并行高速乘法器进行序列相关检测和动态门限配置的方法,大大缩短了TD-LTE小区搜索的处理时间。并以Altera的EP4SGX230KF40C2 芯片作为硬件平台进行了Modelsim功能仿真、板级验证等工作。实验结果表明,该设计方案的处理速度和数据精度均满足TD-LTE 系统测试要求,性能远优于传统的DSP架构模式,可以应用到实际工程中。

时分长期演进(TD-LTE)系统;小区搜索;多通道;并行;现场可编程门阵列(FPGA)实现

0 引 言

小区搜索是移动台在初始接入小区或移动台进行小区切换过程中,与服务小区取得时间和频率同步并获得小区组内ID(identity)的同步过程。在长期演进(long term evolution,LTE)通信系统中,小区搜索的性能直接影响整个系统的正常通信,因此,对小区搜索的研究具有重要价值。

目前,针对LTE小区搜索已有了大量的算法研究。在下行小区搜索的研究中,文献[1]提出了主同步信号的3种不同结构,利用主同步序列和辅同步序列来检测小区ID。文献[2]提出了运用匹配滤波的方法完成主同步序列的检测,以及用最大似然估计的方法完成辅同步序列的检测,利用环路进行频偏估计以及对循环前缀类型进行检测,获得了小区 ID 并实现帧同步。文献[3]利用差分运算以及对接收端信号进行累积处理的方法提出一种符号定时同步与频偏估计的算法。文献[4]根据循环前缀的自相关来完成符号定时同步和频偏估计,降低了实现的复杂度。

目前对LTE小区搜索的研究还主要集中在对同步算法的研究上,这些研究大多是关于小区搜索的某一个过程进行讨论,缺乏对小区搜索整体方案的研究,而针对小区搜索实现的研究主要集中在算法的复杂度和实现架构上,尽管也有一些以市场为导向的公司进行了小区搜索的硬件实现,但大多考虑到算法的复杂性而采用了数字信号处理(digital signal processing,DSP)实现,因此,本文的主要工作集中在小区搜索整体方案的设计和硬件电路的实现上。本文通过对小区搜索算法架构的改进,给出了一种基于现场可编程门阵列(field programmable gate array,FPGA)的多通道并行流水线架构设计方案,与传统的DSP串行处理模式相比,FPGA的下行同步设计减少了数据处理的时延,提高了整个小区搜索的速度。

1 改进TD_LTE下行同步算法设计

LTE系统采用了两级同步信号进行小区搜索的方案,即主同步信号(primary synchronous signal,PSS)进行5 ms定时和获取扇区号,辅同步信号(secondary synchronization signal,SSS)进行10 ms定时和获取小区组内 ID号[5]。

1.1 主同步信号的产生

主同步信号序列d(n)是由频域Zadoff-Chu序列[6]生成,负责携带小区ID信息,其生成方式为

(1)

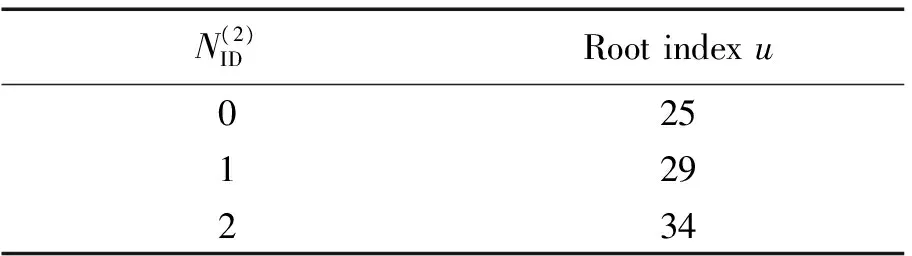

表1 PSS根序列与组内ID号对应关系Tab.1 Correspondence between PSS root sequence and group ID

进行子载波映射时,du(31)位于直流子载波,其余的点按n从大到小的顺序,放置在从低到高映射的子载波上,左右各有5个子载波的保护带。

主同步序列具有良好的自相关性,可以通过此性质完成对主同步信号的检测。

1.2 辅同步信号的产生

辅同步序列是由2个长度为31的m序列交叉级联而成,在时间上位于子帧0和子帧5,而子帧0和子帧5的产生方式不同[7],2个长度为31的序列组合为

(2)

(3)

(4)

(5)

(6)

(7)

在时域,SSS实部具有对称性,虚部具有反对称性,所以,可以利用SSS序列的共轭对称性进行SSS定时粗同步,即半帧同步。

1.3 改进TD_LTE下行同步算法设计

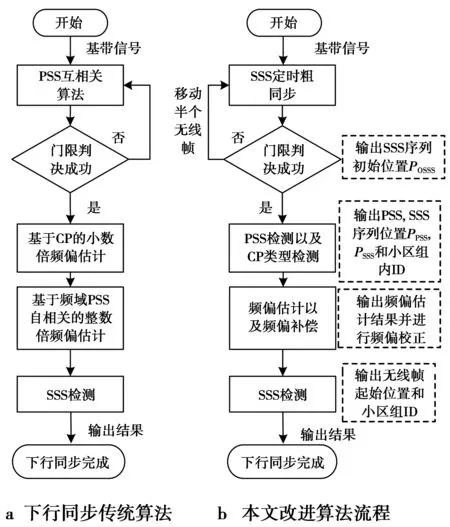

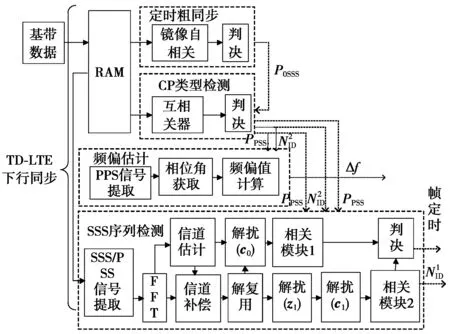

由于下行同步性能的好坏将直接影响着整个下行链路的性能,所以对下行同步的研究具有重要作用[8]。目前下行同步实现的传统方案[9-11]是先通过接收的PSS序列与本地产生的PSS序列做互相关检测得到半帧同步;然后,利用CP循环前缀自相关得到小数倍频偏;之后,利用频域PSS序列自相关得到整数倍频偏;最后,利用SSS序列检测得到无线帧同步,如图1a所示。此方法具有较好的抗噪能力,但需要分别对3组PSS序列遍历进行盲检测得到定时粗同步,运算量大,且系统的抗频偏性能差。

对于由发射机和接收机的本地振荡器频率存在误差和终端快速移动带来的多普勒频移造成系统的频率偏移,所以下行同步算法必须具备良好的抗频偏性能以及较低的运算复杂度。因此,本文对下行同步算法进行了改进,整个算法流程如图1b所示。首先,利用SSS序列的时域共轭对称性进行自相关捕获SSS序列得到定时粗同步,具有良好的抗频偏性能;然后,根据SSS序列与PSS序列的相对位置对PSS序列遍历相关,进行PSS序列检测以及CP类型检测;之后,提取出PSS序列进行频偏估计与校正;最后,通过提取SSS序列进行相关检测确定无线帧的起始位置得到下行的精同步,完成整个下行同步。

2 下行同步算法的FPGA架构设计

2.1 下行同步的FPGA架构

TD-LTE下行同步包括定时粗同步、CP类型检测、频偏估计、SSS序列检测4个子模块,如图2所示。中频输出的数据被存储到随机存取存储器模块,下行同步的各个子模块从存储器中读取数据进行处理,降低各个子模块处理数据的压力。在定时粗同步子模块中,对存储的数据进行滑动镜像自相关,然后,通过相关峰判决,输出SSS信号的初始定时位置。CP类型检测子模块也有滑动相关运算,不同的是与本地3组PSS序列做互相关,而不是自身的镜像相关。频偏估计子模块需要根据PSS序列定时位置信息提取接收信号的PSS序列,然后,经过与本地PSS序列共轭相乘、乘累加等运算,算出频偏估计值,再进行频偏校正。SSS序列检测子模块也需要提取出接收信号中的SSS序列和PSS序列,然后通过PSS序列的信道估计进行信道补偿,再通过解扰、相关运算得出SSS序列信息,就可区分TD-LTE前半帧和后半帧,得到接收信号无线帧的开始位置。

图1 下行同步算法架构设计Fig.1 Architecture design of downlink synchronization

图2 下行同步架构设计Fig.2 Architecture design of downlink synchronization

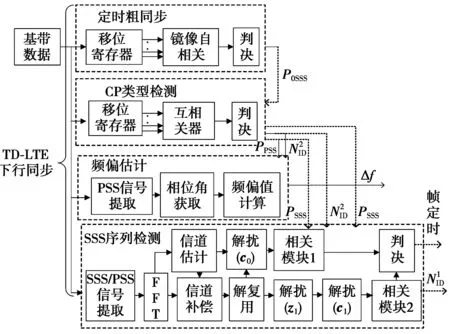

2.2 改进的下行同步FPGA架构

图2所示架构是先将数据进行本地存储,然后再进行下行同步。这种先存储后处理的方式优点是降低了后面模块处理数据的压力,不足在于需要较大的存储空间,且实时性被降低。要进行下行同步最起码要存储TD-LTE半个无线帧,即使I/Q数据以8 bit量化,也至少需要2 457 600 bit的Memory存储空间,这在大部分的FPGA芯片中不可能完成。基于对这点不足的改进,给出了另一种架构图,如图3所示。

图3 改进下行同步架构设计Fig.3 Improved architecture design of downlink synchronization

图3中,去掉了存储器模块,在定时粗同步与CP类型检测中加入移位寄存器模块。移位寄存器深度为2 048,工作在30.72 MHz时钟下,每个时钟移位一次。移位寄存器实际上存储2 048个数据,然后通过16倍抽取为128个数据输出给相关运算模块做并行运算,镜像自相关和互相关模块要在一个30.72 MHz的时钟周期内完成128个数据的镜像自相关和互相关运算。镜像自相关将128个接收数据对称分成2段进行相关运算,而CP类型检测模块中的互相关器是将接收信号与本地的3组PSS序列进行互相关。从乘法的运算量上分析,镜像自相关在一个30.72 MHz的时钟周期内要完成64个复数的乘法,而互相关器至少需要完成3×128个复数的乘法运算。为了降低这2个相关器的资源消耗,可以通过提高这2个模块的工作时钟来实现。在设计中包括镜像自相关和互相关器在内的所有模块工作时钟都为245.76 MHz,是数据速率的8倍,镜像自相关模块只需要8个复数乘法器即可完成64个复数乘法运算,互相关器也只需3×16个复数乘法器。

3 下行同步关键模块的FPGA实现

3.1 定时粗同步

定时粗同步可以分为移位寄存器、镜像自相关和判决3个部分,如图3中定时粗同步模块所示。移位寄存器并行输出128个数据到镜像自相关部分中进行相关运算,然后,将相关运算结果在判决模块中进行判决输出。

移位寄存器的目的是存储一小部分数据,供镜像自相关运算使用,判决器的作用是监测镜像自相关的输出结果是否大于预设的门限值,从而判断粗定时同步是否成功。两者的硬件结构比较简单,这里重点介绍镜像自相关的硬件结构。

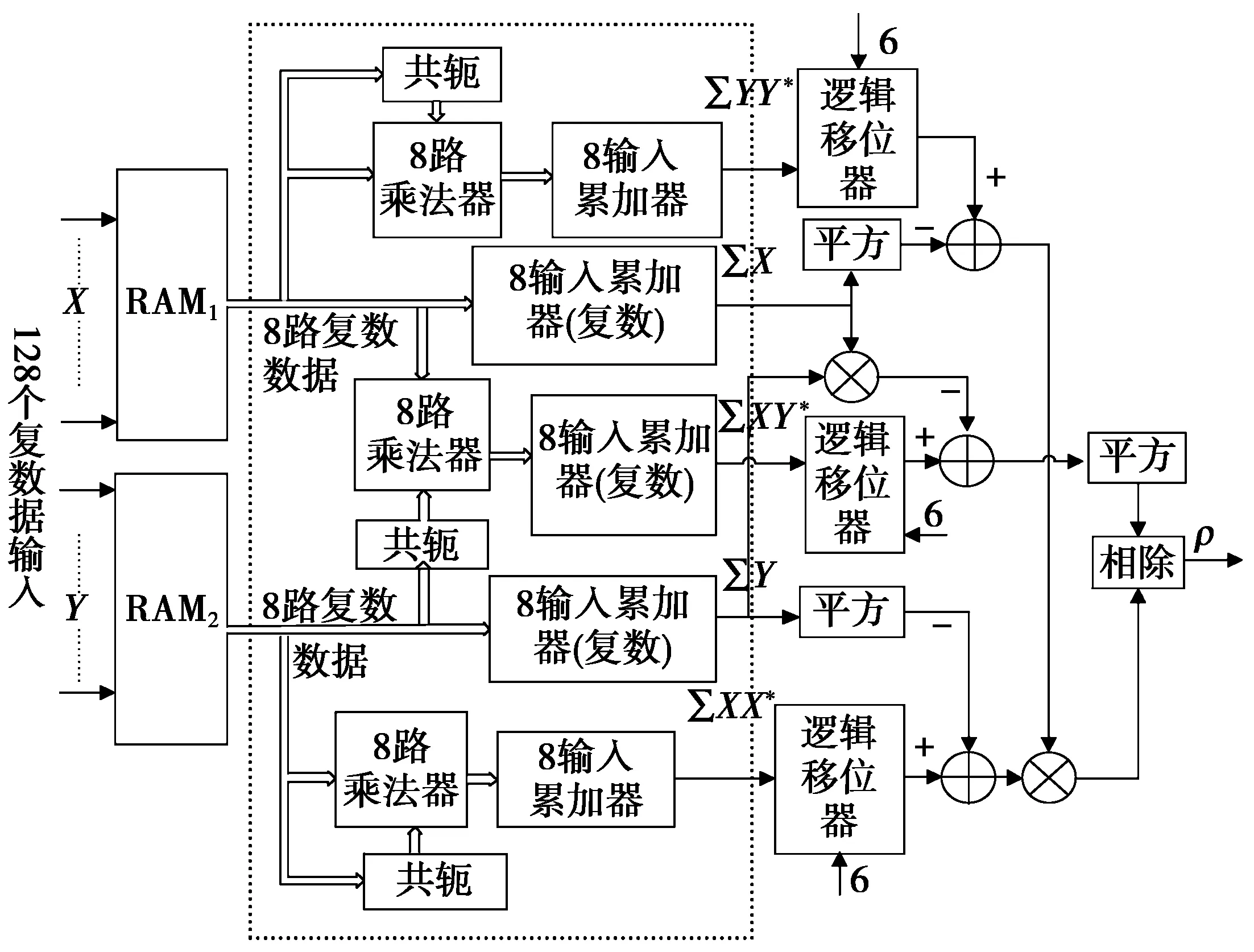

镜像自相关是定时粗同步模块的关键部分,其硬件结构如图4所示。

图4 镜像自相关硬件结构Fig.4 Mirror self-correlation hardware structure

从移位寄存器抽头输出的128个复数数据对称分成2段X和Y分别存到RAM1(random-access memory)和RAM2中,2段数据分别有64个数据,这2段长度为64的数据将被分成8次取出,每次取8个数据,这样做的目的是让后面的运算器在8个工作时钟周期内完成相关运算。图4中虚线部分的功能:每个时钟周期都分别从RAM1和RAM2中对称地不重复地取一小段数据(分别8个复数数据)进行相乘运算后累加或者直接累加,运算8次后即可将RAM1和RAM2中的X,Y数据处理完,得到∑X,∑Y,∑XY*,∑XX*,∑YY*5个累加值。再将这5个累加值进行简单的乘除就得到了X和Y的相关系数值ρ。

镜像自相关模块工作在245.76 MHz的时钟下,是移位寄存器工作时钟的8倍,X,Y这2段数据刚好在8个245.76 MHz的时钟周期更新一次。通过8路并行处理数据大大提高了数据处理的能力,减少了数据处理时间,提高了运算速度。

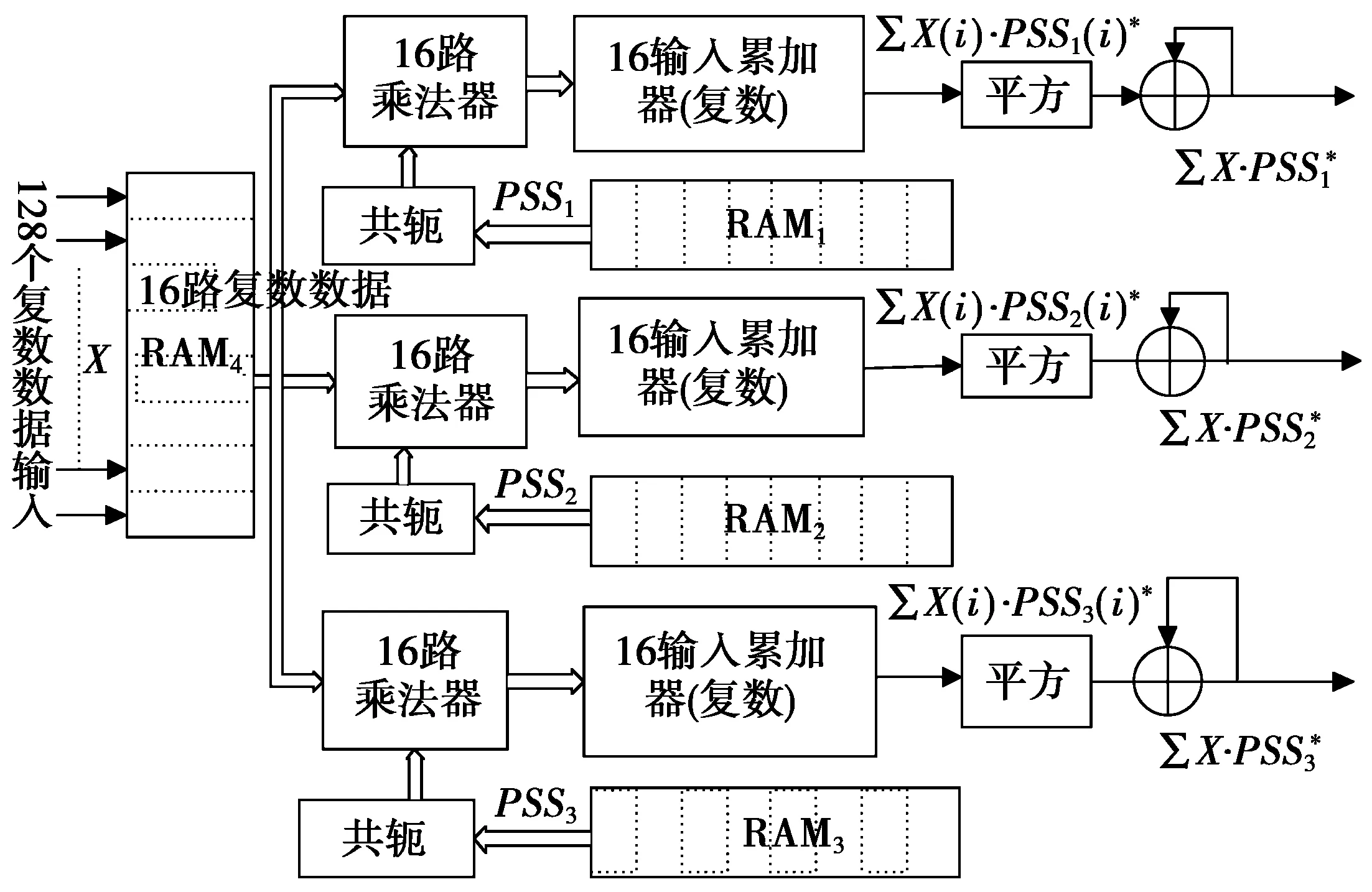

3.2 CP类型检测

在定时粗同步得到c序列的初始位置后,根据2种不同CP类型的长度,可以推算出PSS序列的2个可能位置,在这2个可能位置前后一定长度的窗口上与本地PSS序列做相关运算,找出相关峰最大值即可找到PSS序列位置,同时,确定了CP类型以及小区组内ID,根据现在的PSS位置和CP类型,再对SSS序列的同步位置做精细的调整,至此,CP类型检测完成。

CP类型检测模块,实际上是利用PSS序列的相关特性做定时同步,由定时同步位置推算出CP的类型。CP类型检测模块可以分为移位寄存器、与本地序列互相关和判决3个部分,如图3中CP类型检测模块所示。

移位寄存器和判决的硬件结构比较简单,这里重点介绍与本地序列互相关的硬件结构,如图5所示。本地序列组PSS1,PSS2,PSS3的长度均为128个复数数据,分别存储到RAM1,RAM2,RAM3中,从移位寄存器输入的128个复数数据也被存储到RAM4中,为了能在8个245.76 MHz时钟周期内做完相关运算,每次从 RAM1~RAM4中分别取出16个复数数据进行运算。图5中的16路乘法器就是为了满足一次运算16个数据的乘法而设计的,16路乘法器输出的乘积将在16输入累加器中进行累加。按照算法的要求,要将PSS1,PSS2,PSS3,X均分成4段,每段32个数据,分别求4个相关值后,再累加。则16输入累加器每完成一段乘积的累加后,输出∑X(i)·PSSn(i)*,再进行平方求模,其中PSSn(i)*为3组本地的PSS序列,并清零当前累加值,继续下一段数据的累加。4段数据的相关值将在最后一级加法器中叠加后输出。

3.3 频偏估计

在确定接收信号中PSS序列的位置与当前小区组内ID后,频偏估计模块首先从接收信号中提取出PSS信号,然后,由提取的PSS信号与本地PSS序列共轭相乘的结果求出相位角,最后,由相位角算出频偏值。频偏估计模块可以分为PSS信号提取、相位角获取、频偏值计算3个部分,如图3中频偏估计模块所示。

图5 本地序列互相关硬件结构Fig.5 Local sequence cross correlation hardware structure

3.4 SSS序列检测

SSS序列检测模块为帧定时同步的最后一步。SSS检测模块先利用接收数据中PSS信号进行频域的信道估计;然后,用信道估计的结果对SSS信号进行信道补偿;最后,通过一系列的解扰和互相关运算,得到参数m0和m1,判断当前时隙所处的帧的位置。SSS序列检测模块包括快速傅里叶变换(fast Fourier transformation,FFT)、信道估计、信道补偿、解扰等部分,如图3中的SSS序列检测模块所示。

4 软件仿真分析与硬件测试

4.1 算法仿真结果对比

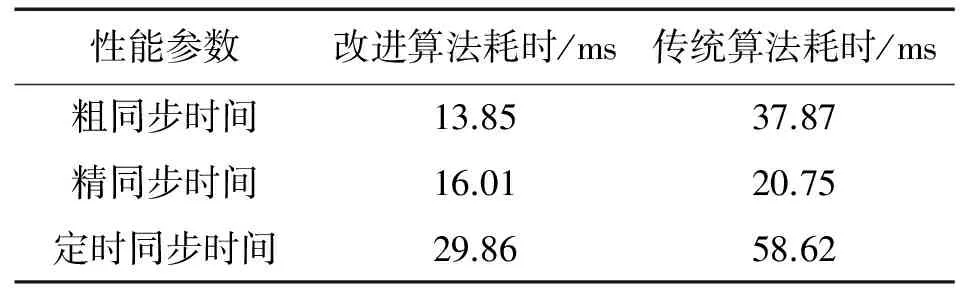

传统算法与改进算法的时间性能仿真结果对比如表2所示。

表2 传统算法与改进算法时间性能对比Tab.2 Time performance comparison of traditional algorithm and improved algorithm

从表2中可以看出,改进算法比传统LTE小区搜索算法在时间上缩短了50%,故采用改进的LTE小区搜索算法能够实现终端更快的接入LTE网络。

4.2 软件仿真

在完成各个模块的FPGA硬件实现后,要通过Modelsim进行功能仿真,验证模块功能是否正确。

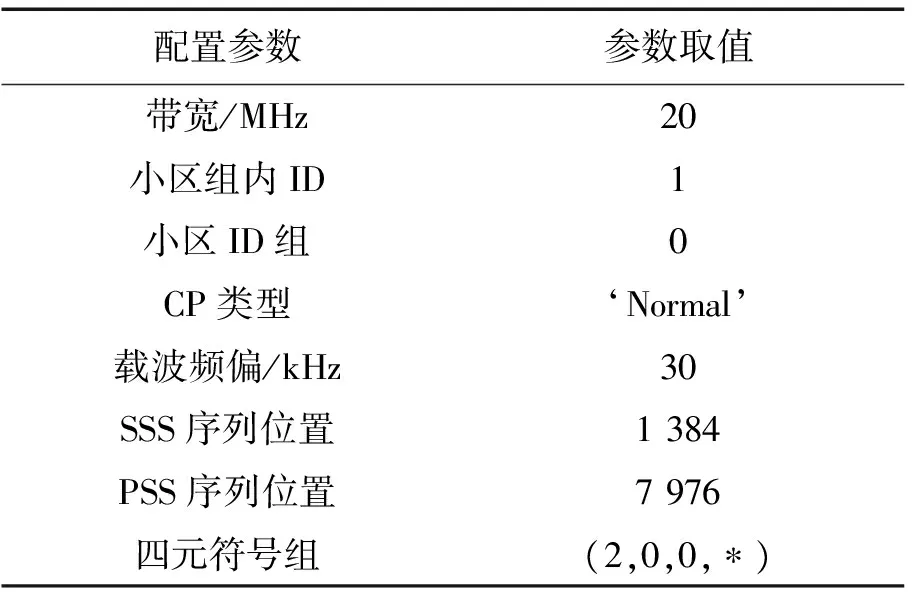

用于功能仿真的TD-LTE数据的部分参数如表3所示。通过对比参数与各个模块运算输出的结果是否一致,判断模块的功能仿真是否成功。用于测试的数据为2个无线帧的长度,即2×307 200个点。

表3 测试参数Tab.3 Test parameter

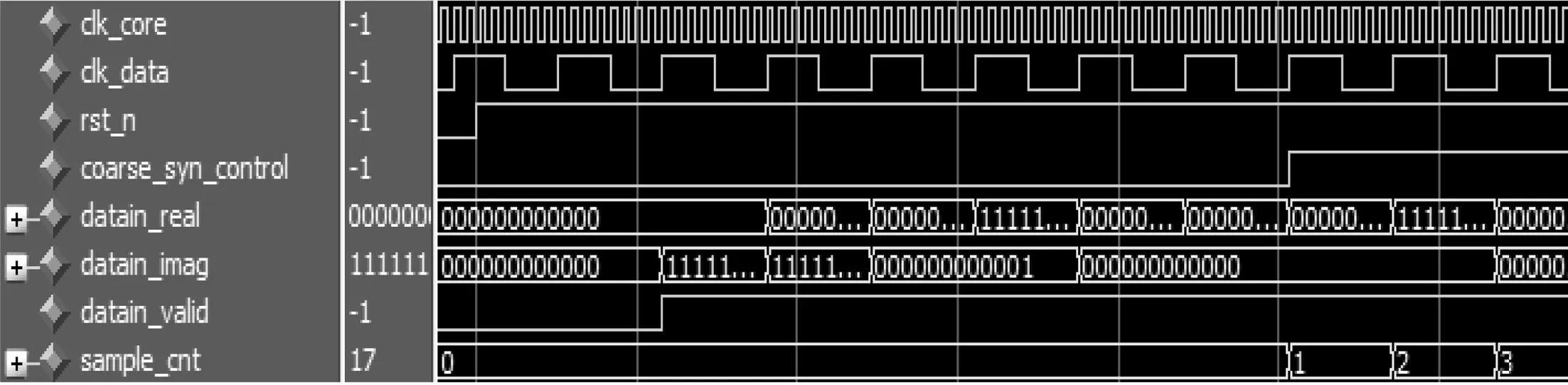

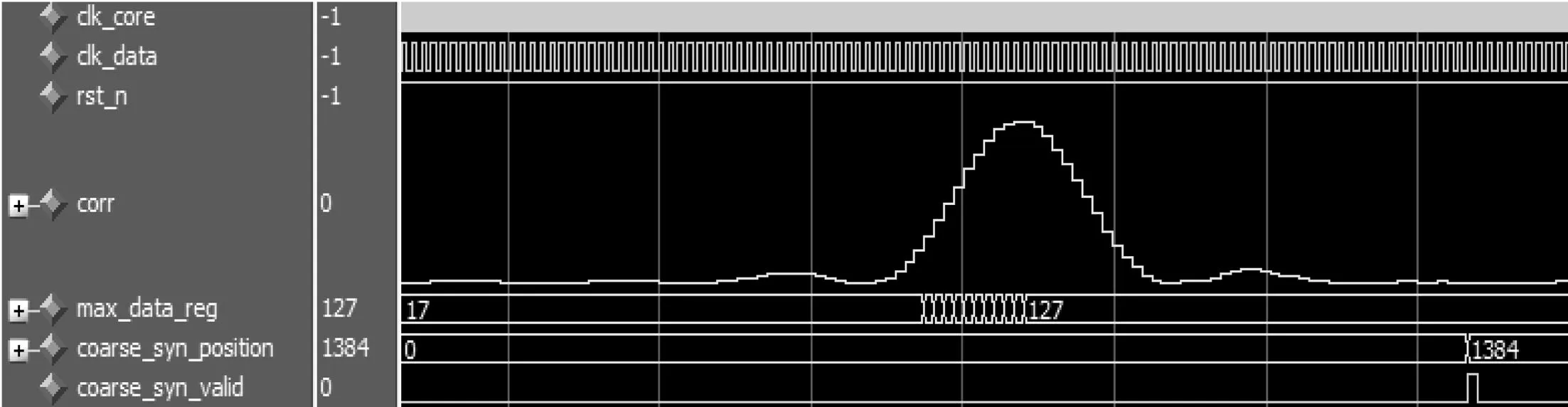

4.2.1 定时粗同步模块功能仿真

定时粗同步的Modelsim功能仿真结果如图6和图7所示。

当控制信号coarse_syn_control拉高后,定时粗同步模块开始对接收数据进行镜像自相关运算,运算时钟为高速率时钟clk_core,并行8路乘法运算1个clk_data时钟输出1个相关结果。coarse_syn_position为定时粗同步的位置输出,从图7中可以看到,相关系数corr的相关峰很明显,最后检测出的粗同步位置(SSS序列的位置)为1 384,与仿真数据参数一致。

图6 定时粗同步功能仿真图1

图7 定时粗同步功能仿真图2

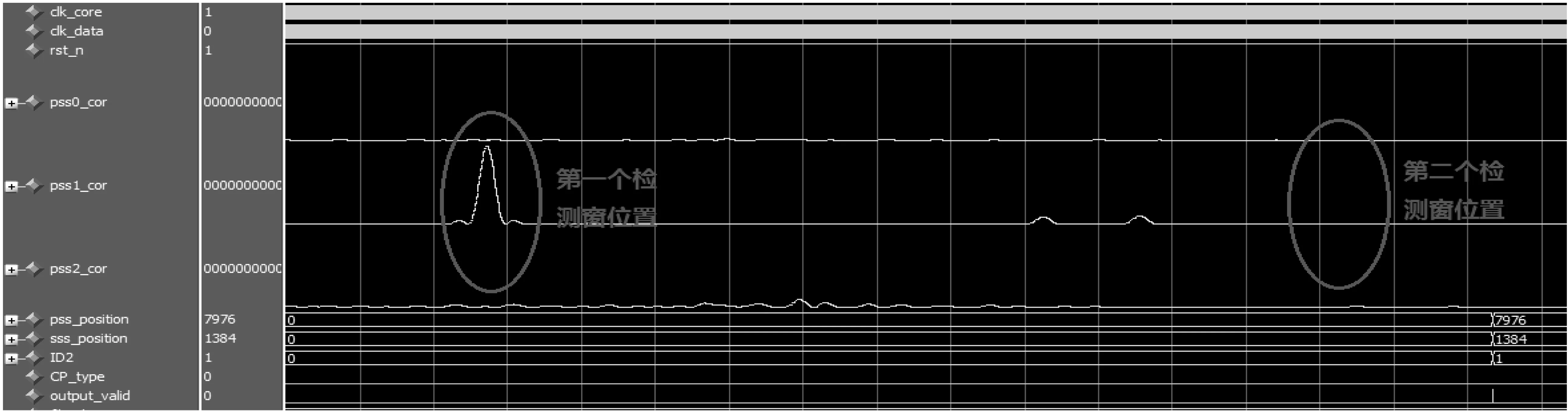

4.2.2 CP类型检测模块功能仿真

CP类型检测模块的Modelsim功能仿真结果如图8所示。pss0_cor,pss1_cor,pss2_cor分别为3组PSS序列与接收信号的相关运算结果,在第1个检测窗上,pss1_cor明显检测到有相关峰,在第2个检测窗上没有发现峰值,由此可以知道,PSS序列在第1个检测窗内,峰值所在位置即为pss_position的输出。从图8中输出结果可以看到,检测到的PSS位置为7 976,CP类型为普通CP,小区组内ID为1,这些结果都与仿真数据的设置一致。

图8 CP类型检测模块功能仿真图Fig.8 Function simulation of CP type detection module

4.2.3 频偏估计及SSS序列检测模块功能仿真

本文主要的改进在于提高定时粗同步和CP类型检测的速度,且鉴于文章篇幅的限制,频偏估计及SSS序列检测模块在科研上都已达成共识,所以在此就不详细描述。

4.3 硬件测试

定时粗同步模块、CP类型检测模块、频偏估计模块、SSS序列检测这4个模块的功能在Modelsim仿真中均正常,在这将各模块级联下载到FPGA芯片中进行测试。本系统采用实验室自主设计的射频板卡以及中频板卡作为硬件平台进行实测验证,如图9所示。

图9 硬件测试平台Fig.9 Hardware testing platform

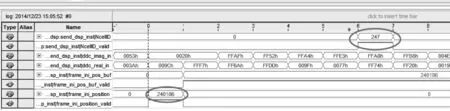

4.3.1 有效性验证

图10 下行同步硬件测试Fig.10 Downlink synchronous hardware test

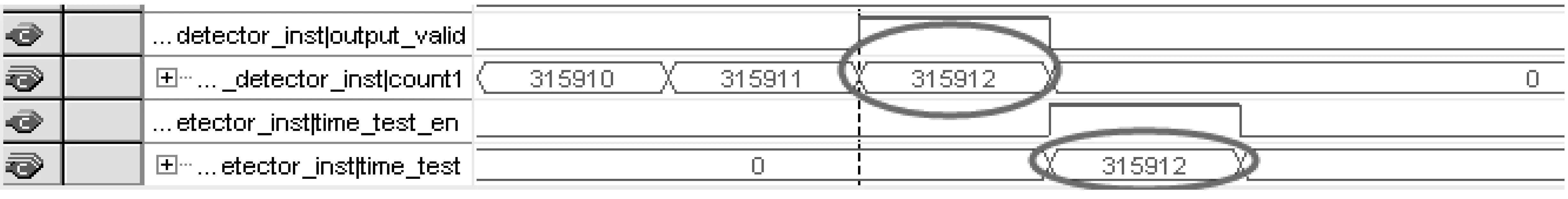

4.3.2 实时性验证

在Signal_TapII中设置好触发条件,将测试控制模块输出测试结果捕捉回计算机进行观察。Signal_TapII中观察到的测试结果如图11所示。当output_valid信号拉高后,表示下行同步完成,此时,计数器count1计数值对应的时间即为下行同步处理时延,计数器所用时钟为307.2 MHz。由time_test中的计数值可以得到下行同步处理时延为1.028 ms,远远小于协议中规定的主同步信号和辅同步信号的检测必须在80 ms之内完成的要求。

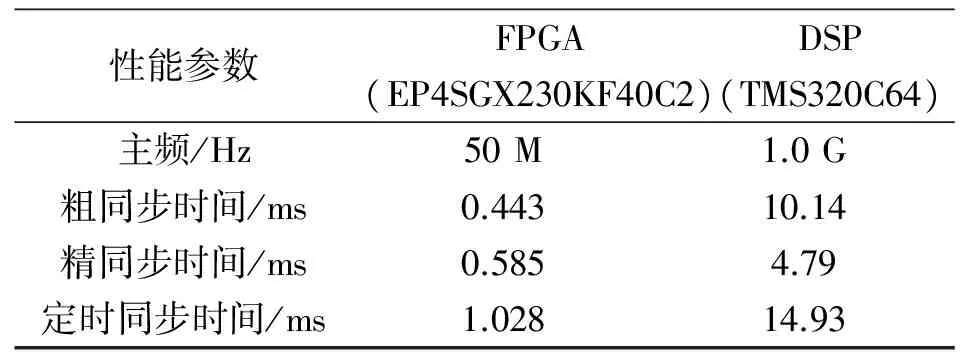

FPGA与DSP在完成LTE小区搜索时的耗时性能对比如表4所示。

图11 下行同步实时性测试结果图Fig.11 Downlink synchronous real-time test results

性能参数FPGA(EP4SGX230KF40C2)DSP(TMS320C64)主频/Hz50M1.0G粗同步时间/ms0.44310.14精同步时间/ms0.5854.79定时同步时间/ms1.02814.93

从表4可以看出,在工程实现中,本文在采用改进算法这一相同算法的前提下,FPGA完成LTE小区搜索的时间比DSP缩短了93%;DSP完成小区搜索需要1帧半的时间,且其串行处理模式要求必须将这些数据全部存储起来,这显然增加了系统的内存消耗和资源成本,且实时处理的能力降低。而FPGA采用的多级流水线结构和并行运算大大提高了数据处理的效率,使得用户终端可以更快地接入LTE网络。

5 结束语

本文在改进传统的TD-LTE小区算法的基础上提出了一种基于FPGA的多通道并行TD-LTE小区搜索的设计方案,并最终在硬件平台上实现。实验结果表明,该方案设计的准确性高,实时处理数据的能力强,性能远优于DSP串行模式。说明FPGA在算法结构固定、运算量大的前端数字信号处理中较DSP表现出先天优势,具有很好的应用场景。该设计方案能够满足LTE系统小区搜索算法的性能要求,可以用到LTE系统开发之中。

[1] SWARTS F, KENT M. Method and system for using sign based synchronization sequences in a correlation process to reduce correlation complexity in an OFDM system: U.S,Patent 8,681,730[P]. 2014-03-25.

[2] GOLNARI A, SHABANY M, NEZAMALHOSSEINI A, et al. Design and implementation of time and frequency synchronization in LTE[J].IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2015, 23(12): 2970-2982.

[3] 孙会楠,禹永植,邢彦辰,等. LTE小区搜索中定时与频偏估计算法研究[J].计算机工程与应用,2015,51(8):70-73,101. SUN Huilan,YU Yongzhi,XING Yanchen,et al. Research on timing and frequency offset estimation algorithm in LTE cell search[J].Computer Engeneering and Applications,2015,51(8):70-73,101.

[4] TSAI P Y,CHANG H W. A new cell search scheme in 3GPP long term evolution downlink, OFDMA systems[C]//IEEE.Wireless Communications & Signal Processing, 2009,WCSP 2009.International Conference on. New York:IEEE Press,2009:1-5.

[5] 张丽君.大点数FFT的二维算法FPGA并行实现[J].无线电通信技术,2013,39(3):86-88. ZHANG Lijun.Large number of two-dimensional FFT algorithm FPGA parallel implementation[J].Radio Communications Technology,2013,39(3):86-88.

[6] CHU C Y, LAI I W, LAN Y Y, et al. Efficient sequential integer CFO and sector identity detection for LTE cell search[J]. IEEE Wireless Communications Letters, 2014, 3(4): 389-392.

[7] 3GPP. TS 36.211, Physical Channels and Modulation v11.6.0 [S]. Valbonne, FRANCE:3GPP, 2014.

[8] XU W,MANOLAKIS K. Robust synchronization for 3GPP LTE system[C]//IEEE.Global Telecommunications Conference (GLOBECOM 2010).New York:IEEE Press, 2010:1-5.

[9] YAN Z,SUN G,WANG X.A novel initial cell search scheme in TD-LTE[C]//IEEE.Vehicular Technology Conference (VTC Spring),2011 IEEE 73rd.New York:IEEE Press,2011:1-5.

[10] HONG T,YANJING S,ZHAOYU L,et al. A Modified Inter-cell Interference Coordination Algorithm in Downlink of TD-LTE Trunking Communication System[C]//IEEE.Instrumentation,Measurement,Computer,Communication and Control (IMCCC), 2013 Third International Conference on.New York:IEEE Press, 2013:1630-1634.

[11] DENG B, WAZ W, LI Y. A novel low complexity cell search algorithm for TD-LTE advanced system[C]//IEEE.Wireless Communications, Networking and Mobile Computing (WiCOM), 2012 8th International Conference on. New York:IEEE Press, 2012: 1-5.

(编辑:王敏琦)

s:The National Natural Science Foundation of China (61301126);The Fundamental and Frontier Research Project of Chongqing (cstc2013jcyjA40032);The Dr. Start-up Foundation of Chongqing University of Posts and Telecommunications (A2012-33);The Young Science Research Program of Chongqing University of Posts and Telecommunications(A2013-31)

The mobile terminal is connected with the network through the cell search. In order to do the cell search efficiently in time division long term evolution (TD-LTE) networks, a multichannel based parallel cell search architecture is proposed using field programmable gate array (FPGA). Compared with the traditional processing mode of digital signal processing (DSP), the speed and area are considered in this paper whose main work is to design a systematic cell search scheme and to implement the system on hardware platform. The proposed scheme optimizes the cell search structure, and the implementation cost is reduced through a parallel multiplier based serial correlation detection and dynamic threshold configuration. Meanwhile, the Modelsim tests and corresponding experiments are conducted on Altera’s EP4SGX230KF40C2 chip. Experimental results show that the proposed scheme can well satisfy the requirement for processing speed and the accuracy of data in TD-LTE networks, and it also outperforms the traditional DSP based processing scheme. It can be applied to the practical project.

time division long term evolution(TD-LTE)system;cell search;multi-channel;parallel;field programmable gate array(FPGA)implementation

10.3979/j.issn.1673-825X.2017.04.002

2016-08-30

2017-02-27 通讯作者:卢 伟 879526709@qq.com

国家自然科学基金(61301126);重庆市基础与前沿研究计划项目(cstc2013jcyjA40032);重庆邮电大学博士启动基金(A2012-33);重庆邮电大学青年科学研究项目(A2013-31)

TN 929.5

A

1673-825X(2017)04-0433-08

Design and implementation of multi-channel based parallel cellsearch in TD-LTE networks using FPGA

(Chongqing University of Posts and Telecommunications, Chongqing Key Lab of Mobile Communications Technology,Chongqing 400065, P.R.China)

蒋 青(1965-),女,重庆人,教授,硕士,研究方向为宽带网络技术和信息理论。E-mail:jiangq@cqupt.edu.cn。

卢 伟 (1992-),男,重庆人,硕士研究生,研究方向为信号检测与估计。E-mail:879526709@qq.com。

江宇航 (1989-),男,安徽人,硕士研究生,研究方向为信号检测与估计。E-mail:120899210@qq.com。

魏 珊 (1993-),女,重庆人,硕士研究生,研究方向为信号检测与估计。E-mail:1033764762@qq.com。

JIANG Qing, LU Wei, JIANG Yuhang, WEI Shan