单粒子仿真方法研究

2017-08-07李若飞胡长清

李若飞,胡长清

(中国电子科技集团公司第四十七研究所,沈阳110032)

单粒子仿真方法研究

李若飞,胡长清

(中国电子科技集团公司第四十七研究所,沈阳110032)

在宇航级器件的设计过程中,主要考虑单粒子效应和总剂量效应。随着工艺尺寸的不断缩小,总剂量效应变得越来越不明显,而单粒子效应变得越来越显著。对于CMOS电路,单粒子效应主要包括单粒子锁定和单粒子翻转,防止单粒子锁定的方法非常成熟,单粒子翻转效应的研究是现今抗辐照研究的主流。评估单粒子效应的方法主要是实验方式,实验评估单粒子效应虽然准确,但是机时少,费用高,实验周期长,给项目研制过程造成很大障碍,因此非常有必要开展单粒子仿真技术研究。提出一种以Hspice电路网表为基础的单粒子效应评估方法,此方法采用脉冲电流模拟单粒子产生的效果,通过此方法可以有效模拟单粒子现象,并找到电路的设计敏感点,有效指导设计。

抗辐照;单粒子翻转;单粒子闭锁;比较器;仿真;冲击能量;单粒子效应

1 单粒子效应概述

运行在宇宙空间中的各类人造卫星、空间探测器等航天器的微电子器件都会受到来自空间的宇宙射线以及频谱范围较宽的电磁辐射影响,并产生不同程度的损伤。除了天然的辐射环境外,核武器爆炸所产生的辐射也会对各类电子系统及电子元器件构成严重威胁[1]。为了增强关键电子系统和武器系统中电子设备的抗核辐射能力,提高它们的生存能力,世界上许多国家都在致力于辐射对微电子器件的影响以及抗辐射加固技术等方面的研究。

目前,在宇航级器件设计过程中,主要考虑单粒子效应(SEE,Single Event Effect)和总剂量效应(TID,Total Ionizing Dose)对芯片造成的影响。随着工艺进步,总剂量效应对芯片的影响在减小,有数据表明,当栅氧厚度小于10nm时,就可以不考虑总剂量效应引起的阈值电压漂移现象[2],而当前标准0.18微米CMOS工艺下栅氧的平均厚度已经达到了3.8nm。随着氧化层以及硅界面质量的提高,总剂量效应对体硅下CMOS电路的影响将越来越小。而随着工艺尺寸的下降,单粒子效应影响将越来越严重。

据有关资料统计表明[3],自1971年至1986年,国外发射的39颗同步卫星,因各种原因造成的故障共1589次,其中与空间辐射有关的故障有1129次,占故障总数的71%。而在辐射造成故障中,由单粒子效应造成的故障有621次,占辐射总故障的55%。我国发射的航天器也发生过类似的故障。空间辐射环境中的高能质子、中子、α粒子、重离子等都能导致航天器电子系统中的半导体器件发生单粒子效应,严重影响航天器的可靠性和寿命。因此,开展单粒子效应研究刻不容缓。

2 单粒子效应理论模型

单粒子效应是指高能带电粒子在穿过微电子器件的灵敏区时,沉积能量,产生足够数量的电荷,这些电荷被器件电极收集后,造成器件逻辑状态的非正常改变或器件损坏,它是一种随机效应。除了空间高能粒子以外,各种核辐射、电磁辐射环境也是造成单粒子效应的主要原因。单粒子效应本身涉及的器件面较广,效应也是多样的。尽管注入器件的粒子是大量的,但由于这种效应是单个粒子作用的结果,通常称为单粒子效应,也叫单粒子事件。随着单粒子效应研究的不断深入,新器件的不断应用,新现象的不断出现,单粒子效应分类越来越细。表1给出了目前已经明确定义的单粒子效应类型[4]。

单粒子烧毁主要发生在功率MOSFET和双极功率晶体管中,单粒子栅穿主要出现在功率MOSFET、EEPROM以及非挥发性SRAM写入和擦除过程中。对于数模混合电路,模拟电路的瞬态可能导致数字电路的翻转。

表1 单粒子效应分类

单粒子效应产生的物理机理主要是粒子与物质发生下列四种作用:①与核外电子发生非弹性碰撞;②与原子核发生非弹性碰撞;③与原子核发生弹性碰撞;④与核外电子发生弹性碰撞[5]。

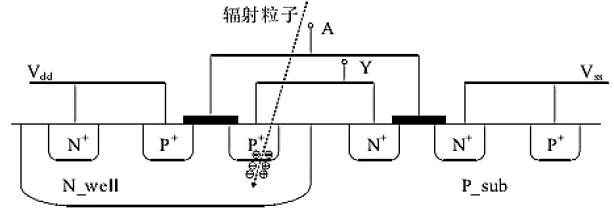

以一个CMOS结构的反相器为例,详细说明辐射环境中的粒子在穿透硅衬底后对硅材料产生的影响,如图1所示为单粒子在CMOS反相器中作用的示意图。当输入A=1时,PMOS截止,NMOS导通,此时PMOS的漏端为敏感点,单粒子会在此位置产生对电源的脉冲;当输入A=0时,PMOS导通,NMOS截止,此时NMOS的漏端为敏感点,单粒子会在此位置产生对地的脉冲。

3 评估单粒子效应的方法

一般来说,评估单粒子翻转对芯片的影响可以通过实验或者模拟的方法。实验方法也分为在轨实验和地面实验,在轨实验是指发射专用的卫星统计单粒子效应对芯片的影响;而地面实验则通过专门设备产生空间辐射环境中存在的粒子并轰击芯片中,然后对芯片的输出进行实时监测从而统计单粒子效应对芯片的影响[6]。实验方法贴近真实物理环境,可以得到很准确的结果,但是需要非常昂贵的成本和花费较多的时间。

图1 单粒子在CMOS反相器中作用示意图

对单粒子翻转的模拟可以通过多种方法完成,具体来说主要有以下几种:①基于系统级的模拟;②计算错误传播概率的软错误评估;③基于器件级的仿真;④基于晶体管的电路级仿真;⑤基于器件-电路级的混合仿真;⑥基于基本逻辑门的电路级模拟等。

基于系统级及电路级,主要是用来寻找电路薄弱点,对于数字电路的设计有一定指导意义。现在对单粒子翻转的模拟方法主要集中在器件级和晶体管电路级,现在国外对器件级的仿真一般都基于精度较高的三维模型进行单粒子翻转仿真。对于晶体管的电路级仿真,一般是先对单粒子翻转建立电流脉冲注入模型,然后通过该模型在电路SPICE网表的节点中注入脉冲电流,从而对单粒子翻转进行模拟[7]。器件级仿真需要先用TCAD软件建立器件模型,在实际应用中可行性不高,而电路级仿真非常适合在电路设计中应用。本评估方法采用基于Spice网表的器件级仿真。

4 单粒子入射量化模型

入射粒子对器件损伤的强弱通常用线性能量传输(LET,Linear Energy Transfer)来表示,确切的说,LET表示的是入射粒子在单位长度上淀积的能量,再除以硅的密度,LET值用密度归一化,单位变为MeV·mg-1·cm2。

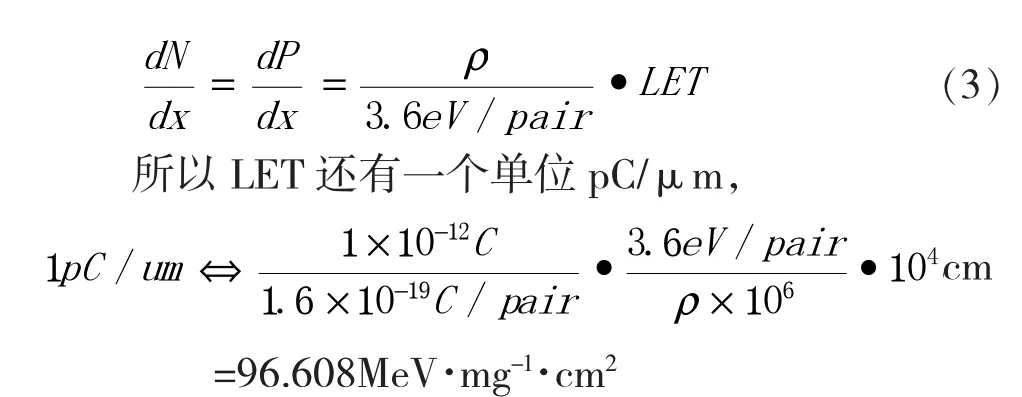

一对电子—空穴对带有3.6eV电荷,因此

对在硅材料中,单粒子效应在单位长度上产生的电子—空穴对为:

根据Mark P.Baze等人的“A Digital CMOS Design Technique for SEU Hardening”中的描述单粒子入射后产生的电荷与LET值的关系。

LETEST=96.608×Qcrit(pC)/LEST(μm)

LEST:估计电荷收集长度,单位μm。

LETEST:辐射的线性能量传输,单位MeV·cm2/mg。

Qcrit:电荷量,单位pC。

北 京 源 LET=37.3,Si中 射 程 30.8μm,即LEST=30.8μm,单粒子翻转37MeV·cm2/mg,对应的Qcrit=11.86pC。

通过实验及论文显示,单粒子的入射能量不会大于11.86pC,因此可以以此为设计边界进行单粒子特性仿真。

5 单粒子效应仿真

为考察电路在辐射环境下的表现和加固电路的设计效果,目前常见的方法是采用电流源作为单粒子对电路的影响模型[4],采用HSPICE来模拟SEE对电路的影响。

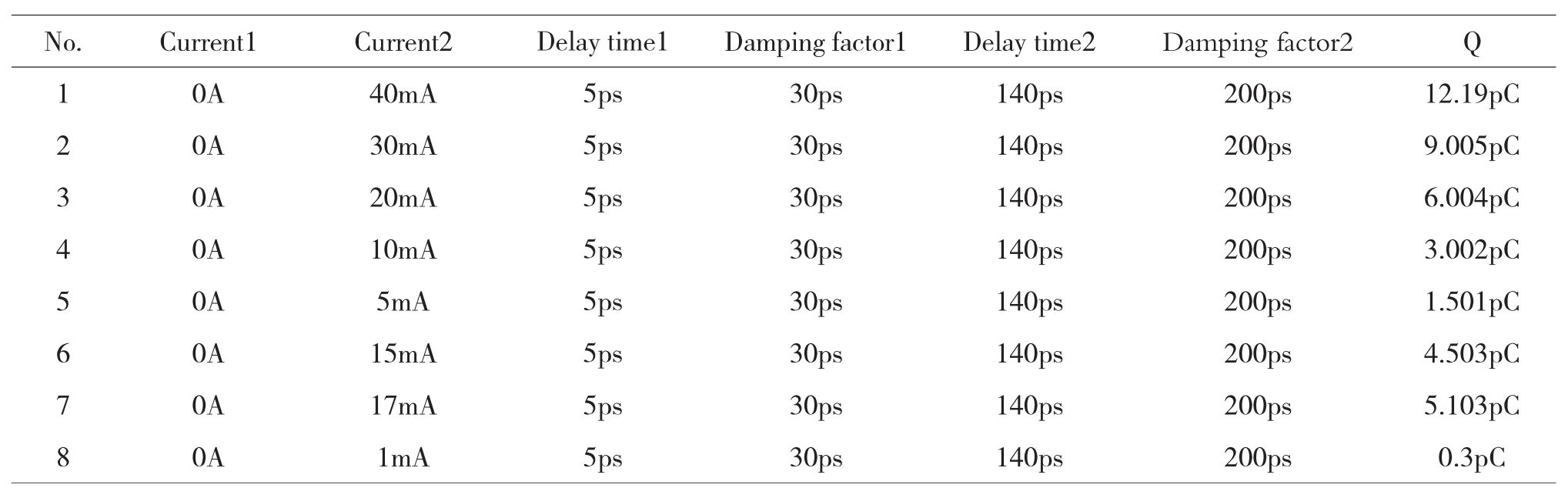

式(4)是文献[8]给出的电流源表达式,其中T是和晶体管模型及离子能量吸收(LET)有关的常量,且P管和N管的值不同,t是时间变量。针对文中所采用的0.5μm栅宽和5V工作电压,根据文献[4]所述,式(1)中的 T:对于 P 管 T=116ps,N 管 T=164ps。为了仿真方便,对于N管、P管采用相同电流源T=140ps。图2给出建模后的单粒子电流源模型(随着时间变化电流变化),其具体Hspice设置如下:

IXX (AB)isource type=exp val0=0 val1=40.00m td1=0.000005u tau1=30p td2=0.00014u tau2=200p

经计算其代表的能量为12.19pC。

图2 单粒子电流源模型波形

绝大部分设计抗辐射电路的工程师都了解单粒子效应的结果就是产生一个瞬态的电流脉冲,但该脉冲的宽度和高度该如何确定,它们与粒子能量或者LET之间是一个什么关系,包括三大EDA厂商在内的绝大部分公司的电路模拟软件都无法给出科学的合理解决方案。当然这还与具体的工艺流程参数有很大关系,相同特征尺寸不同厂家所制造出的芯片抗单粒子效应的能力在很大程度上也是不同的。针对同一工艺需要多次校准才可以得到准确的仿真模型。因此我们采用在关键节点注入不同能量的电流源,记录相应响应,再与实验现象进行拟合,在同一工艺下可以得到比较准确的仿真模型,为可以给在其他工艺上的电路设计提供一定的指导意义。采用的电流源如表1所示。

表1 仿真中用的电流源

以比较器为例分析仿真具体方法,采用两种结构的比较器进行分析。具体方法为在比较器输入端输入方波信号,在各节点根据节点电压加入单粒子电流源,通过仿真发现每个电路的关键点记为KN(N=1,2,3……)。

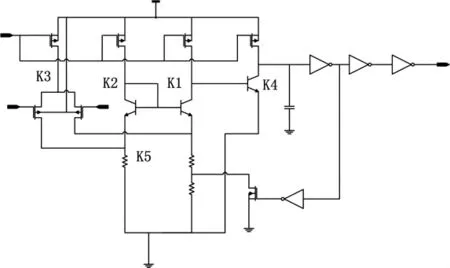

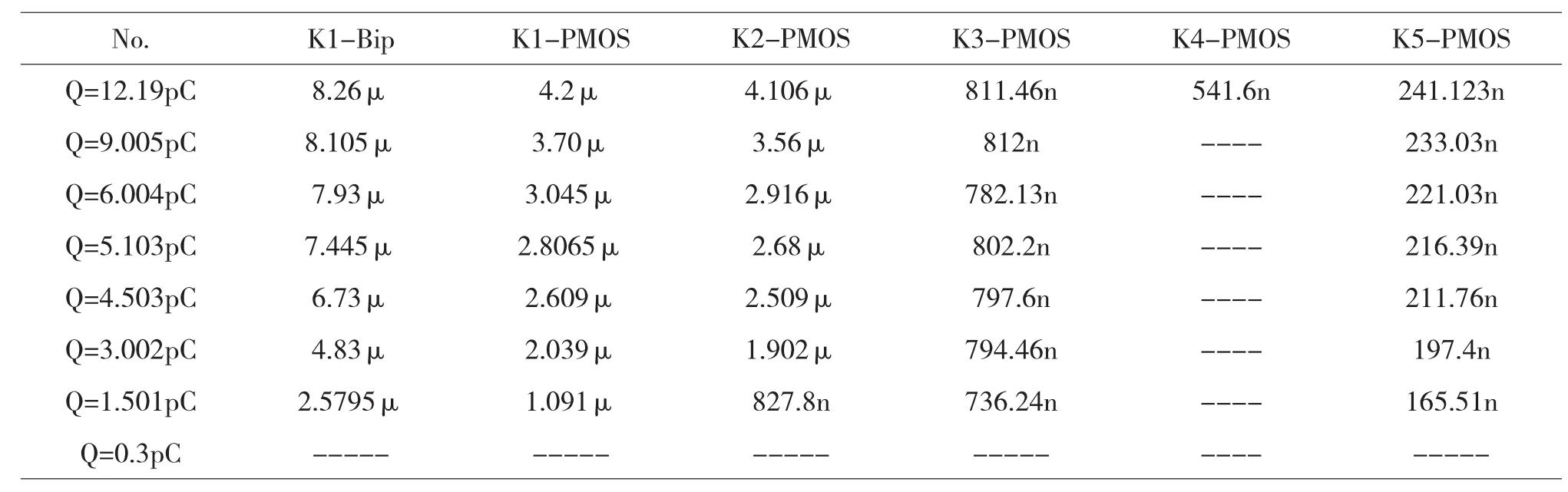

如图3所示为比较器一的电路图,比较器一的第一关键点出现在K1处Bipolar CB结冲击,第二关键点出现在K1处PMOS,第三关键点出现在K2点PMOS处,第四关键点出现在K3点PMOS处,第五关键点出现在K4点PMOS处,第六关键点出现在K5点PMOS处。表2记录了不同的冲击能量冲击关键点时,输出产生的翻转脉宽。

图3 比较器一电路图

表2 比较器一各关键节点对不同冲击能量的响应

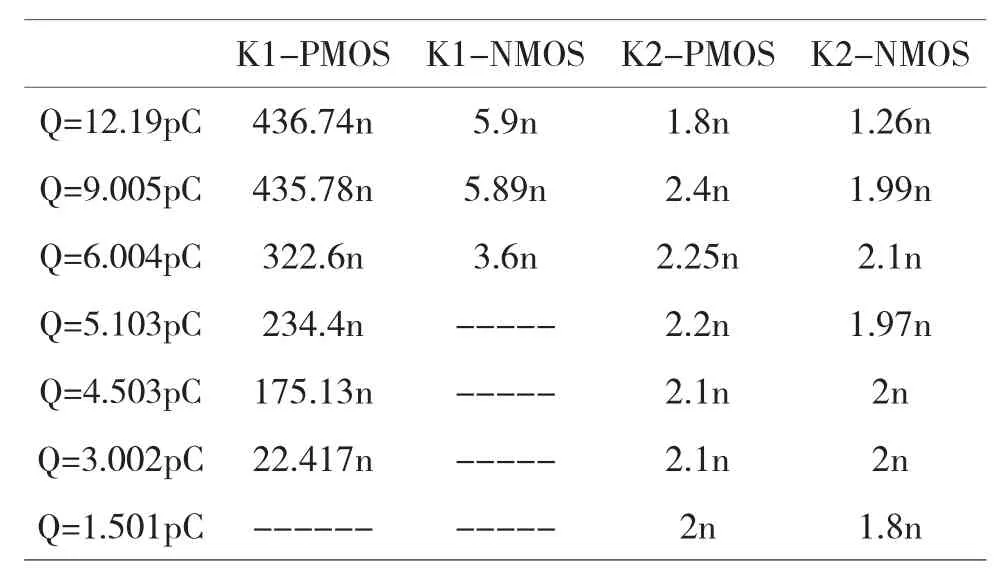

图4为比较器二的电路图,比较器二的主体结构由两个单级差分开环运放构成,加入一个正反馈来调节第一级差分运放的负载进而通过改变比较阈值引入迟滞效应。此电路的关键点出现在K1点PMOS的单粒子效应。K1点NMOS的单粒子效应及K2点NMOS、PMOS的单粒子效应对后面而言都不是问题。表3记录了不同的冲击能量冲击关键点时,输出产生的翻转脉宽。

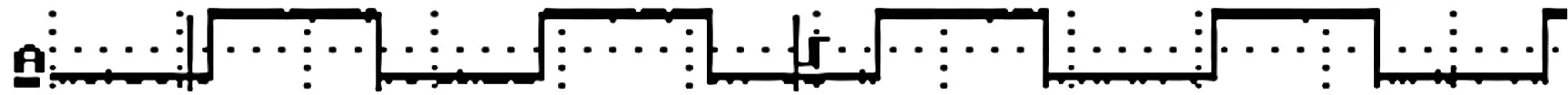

从上述分析看,比较器一比比较器二的关键节点要多,在同等能量电流脉冲的冲击下比较器二的响应明显好过比较器一。经过试验验证,比较器一在Cl离子冲击(LET=12.9MeV·cm2/mg)下已经有单粒子现象发生,如图5所示,并引起了后面电路的单粒子翻转,在 Ti离子冲击(LET=21.8MeV·cm2/mg),比较器出现频繁的单粒子现象,如图6所示。而比较器二在Ge离子冲击(LET=37MeV·cm2/mg)也没有看到单粒子现象。试验证明比较器的二抗单粒子特性要优于比较器一,与仿真结果一致。

表3 比较器二各关键节点对不同冲击能量的响应

图4 比较器二电路图

图5 Cl离子冲击下比较器一特性

图6 图6 Ti离子冲击下比较器一特性

6 结束语

经过单粒子仿真分析,采用指数电流的方法,其关键在确定电流源能量上,因此后续需要在不同的能量下采集出单粒子现象,并与仿真进行拟合,最终得到此工艺下不同离子能量对应的电流源,以便指导后续设计。

[1] J.V.Osborn,R.C.Lacoe,D.C.Mayer,G.Yabiku.Total dose hardness of three commercial CMOS microelectronics foundries[J].IEEE Trans.Nucl.Sci.1998:1458-1463.

[2] Hughes,H.L.,Benedetto,J.M.Radiation effects and hardening of MOS technology:devices and circuits[J].IEEE Trans.Nuclear Science:500-521.

[3] 王长河.单粒子效应对卫星空间运行可靠性影响[J].半导体情报,1998,35(1):1-8.Wang.Changhe,The Effect of single particle effect on the reliability of satellite space operation[J].Semiconductor Information,1998,35(1):1-8.

[4] 贺朝会.单粒子效应的研究现状和动态[J].中国科技论文在线 1996,36(4):5~9 He.Chaohui,Resecarch status and dynamics of single particle effect[J].Chinese science and Technology Papers Online,1996,36(4):5-9.

[5] P.S.Winokur,K.G.Kerris,and L.Harper,Predicting CMOS inverterresponse in nuclear and space environments[J].IEEE Trans.Nucl.Sci.1983:4326-4332.

[6] P.Eaton,J.Benedetto,D.Mavis,K.Avery,M.Sibley,M.Gadlage,T.Turflinger.Single event transient pulse width measurements using a temporal latch technique[J].IEEE Trans.Nucl.Sci.,2004,51(6):3365-3368.

[7] M.R.Shaneyfelt,J.R.Schwank,D.M.Fleetwood,and P.S.Winokur,Effects of irradiation temperature on MOS radiation response[J].IEEE Trans.Nucl.Sci.1998:1372-1377.

[8] Hazucha P Svensson C:Impact of CMOS technology scaling on the atmospheric neutron soft error rate[J].IEEE Trans.Electron Devices,1990:1467-1476.

Study on Single Event Effect Simulation

Li Ruofei,Hu Changqing

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

In the design process of aerospace-grade devices,the main consideration is SEE and TID.As the process dimension is decreased continuously,total dose effect is getting more unobvious,but single event effect becomes more serious.For CMOS circuit,single event effect(SEE)includes Single Event Latchup(SEL)and Single Event Upset(SEU).The method of avoiding SEL is mature,so SEU is the key point in anti-radiation study.Now,the experiments are mainly used for SEU evaluation,which are accurate but have less machine time and more cost,so it is necessary to carry out single event effect simulation technology.The evaluation method for single event effect,based on Hspicenetlist,employing the effect generated by pulse current simulating SEE,is proposed in this paper,which is effective and can guide design.

Radiation-hardened;SEU(Single Event Upset);SEL(Single Event Latchup); Comparator;Simulation;Impact energy;Single event effect

10.3969/j.issn.1002-2279.2017.03.002

TN495

B

1002-2279-(2017)03-0008-05

李若飞(1984-),男,辽宁省沈阳市人,工程师,主研方向:集成电路设计。

2016-07-22