双通道模数转换器AD9268的变压器耦合设计

2017-08-02杨士义

王 丽,杨士义

(中国空空导弹研究院,河南 洛阳 471009)

双通道模数转换器AD9268的变压器耦合设计

王 丽,杨士义

(中国空空导弹研究院,河南 洛阳 471009)

ADC前端是确定模数转换器接收和采样的信号质量的关键部分,基于对双通道模数转换器AD9268前端调理电路的设计、参考时钟的考虑,利用变压器进行匹配耦合设计,得到一个高性能的模拟前端ADC。

变压器;阻抗;差分模式;耦合

0 引言

在高速中频信号预处理电路系统设计中,根据需求不断追求高速模数转换器ADC的各个电路环节的优化设计来取得较高的指标;而任何一个环节的设计都应有一个恰当的目标,ADC前端耦合设计也不例外。概括来说,ADC的前端要实现以下几大目标:带宽、VSWR电压驻波比、通带平坦度、SNR信噪比、SFDR无杂散动态范围和输入驱动电平[1]。AD9268是一款双通道ADC,内核采用多级、差分流水线架构,并集成了输出纠错逻辑;每个ADC均具有宽带宽、差分采样保持模拟输入放大器;适用于高性能、低成本、小尺寸且具有多功能性的信号处理系统。

1 设计要求及器件指标

硬件系统设计从器件选型开始,选择正确的器件可以大大减少重复次数,并快速实现所需性能。AD9268是一款双通道、16位、80/105/125 MS/s模数转换器(ADC),主要性能指标如表1所示[2],有三种型号供选择,因此可以根据设计要求的采样率灵活选用。本设计中需要6路中心频率为75 MHz的中频输入,采样率为100 MHz,带宽为20 MHz,要求无杂散动态范围大于80 dBc,50 Ω输入阻抗匹配。故选用三片105 MS/s的AD9268,并且采用差分输入配置,确保高采样率条件下的高性能,同时能带来非常高的可用输入带宽,这一点对于某些中频采样或欠采样应用尤为重要,同时也有效抑制共模干扰。

表1 AD9268主要性能指标

2 差分输入考虑

AD9268架构由一个双前端采样保持电路和其后的流水线型开关电容ADC组成,这就意味着输入阻抗是时变的,而且会随着模拟输入信号的频率发生变化,要匹配这样的输入阻抗是一个十分具有挑战性的设计问题。

根据拓扑结构形式的不同[3],ADC的前端设计主要有两类:一类是放大器形式的拓扑结构;另一类是变压器方式的拓扑结构。当信号的频率很高而且ADC的输入端不允许很大的附加噪声时,变压器在保持SNR和SFDR等方面表现出相当大的优势。

变压器作为一种无源器件,可以实现阻抗匹配、隔直及单端和差分信号之间的转换等功能,因此,具有很好互阻性能的变压器是一种非常不错的选择。设计中用变压器耦合的方式代替传统的电感、电容谐振网络来实现输入、输出端的阻抗匹配和单端信号差分信号之间的转换。在输入匹配中,变压器将驱动级的输入阻抗匹配到50 Ω源阻抗,同时还可以实现单端输入到差分输出的转换。采用变压器耦合可以降低版图设计难度,实现了低成本、高效率设计。

如图1所示,在设计中,AD9268的输入配置采用差分变压器耦合,充分平衡系统的总负载;为实现模拟输入偏置,将VCM电压连接到变压器次级绕组的中心抽头处。为了保证共模电平的低噪声,阻抗匹配电路在变压器的次级端进行信号的阻抗匹配及滤波,有效地提高增益平坦度和优良的采样动态范围。

图1 差分变压器耦合配置

其次,每个输入端都串联一个小电阻,可以降低驱动源输出级所需的峰值瞬态电流。在两个输入端之间可配置一个并联电容,以提供动态充电电流。为得到最佳动态性能,必须保证驱动VIN+的源阻抗与驱动VIN+的源阻抗相匹配,并且使两输入保持差分平衡。设计中对器件进行设置,使得VCM=0.5×AVDD;芯片通过VCM引脚提供板上共模基准电压。通过VCM引脚提供模拟输入共模电压时,用一个0.1 μF电容对VCM引脚去耦到地。

本设计中采用阻抗比为1∶1,且具备独立金属壳地的RF变压器,从而在空间上有效地阻止了通道间的信号耦合。此外,选择变压器和R与L的元件值以匹配负载[4-5],在ADC与变压器次级之间建立一个能实现所需整体性能的抗混叠滤波器,表2列出了设置RC网络的参考值,在设计电路时可以参考。

表2 RC网络参考值

3 差分时钟考虑

为了充分发挥AD9268芯片的性能,利用差分信号作为采样时钟输入端(CLK+和CLK_)的时钟信号。如图2所示,设计中使用一个变压器将单端时钟信号转为差分信号,通过LVPECL电平的时钟分配器,分成多路LVPECL电平的差分时钟信号供给多片ADC芯片,这样可有效降低时钟电路产生环节,抑制共模干扰,降低时钟抖动,LVPECL电平为发射极耦合逻辑电路(差分结构)输出,具备速度快、驱动能力强、噪声小等优点,很容易满足几百兆赫兹的应用需要。

图2 时钟电路

4 测试结果及分析

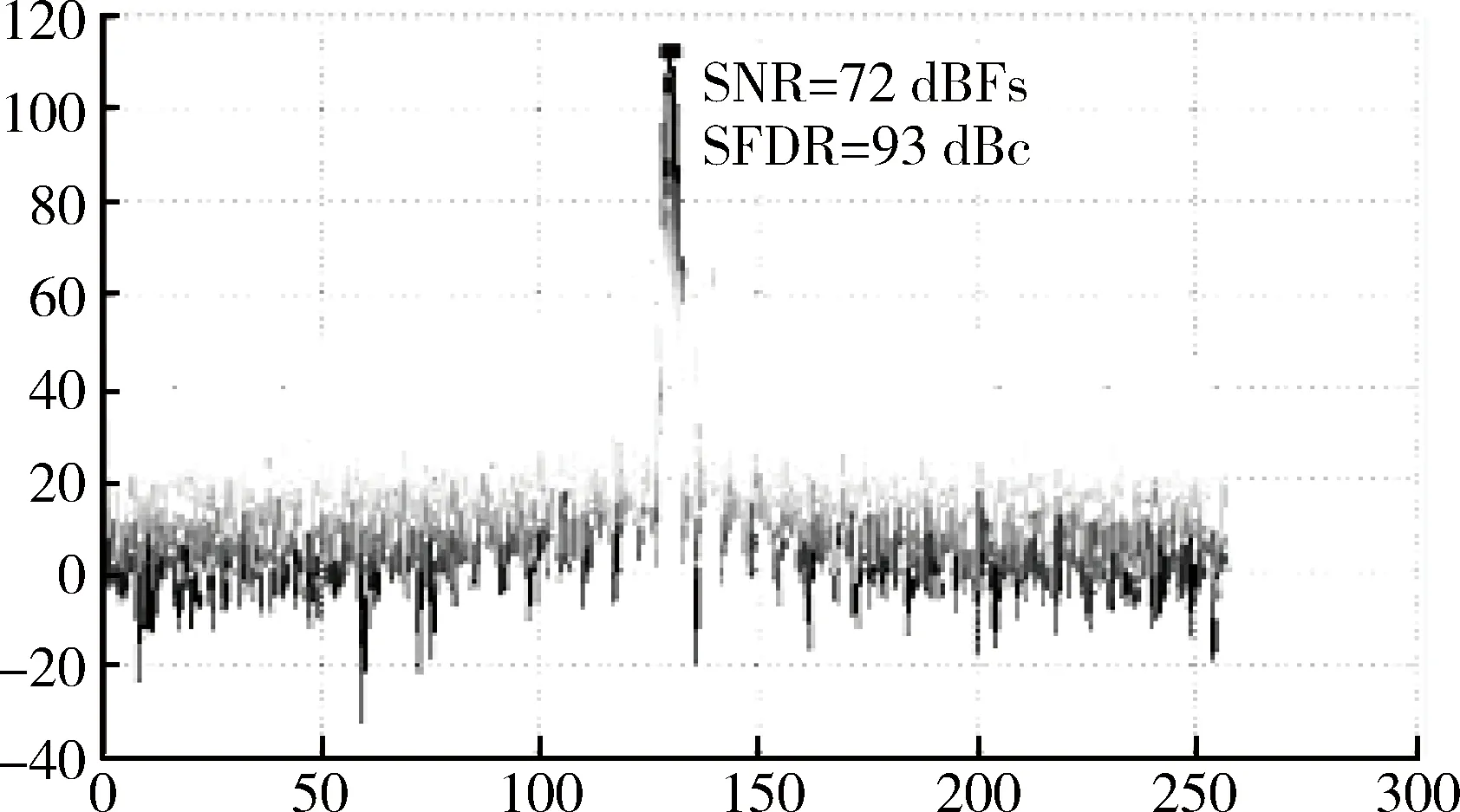

通过FPGA Chipscope观测ADC采样后的输出数据并导出,可以使用软件工具MATLAB或者VisualAnalog对数据进行分析。结合总体项目,在MATLAB中对图3所示信号频谱图做信号频谱分析,测得信噪比为72 dBFS,无杂散动态范围满足大于80 dBc的要求。

图3 信号频谱图

ADC模块单元的大动态范围、高信噪比等性能将直接影响到后续的信号处理和检测,而前端设计更是确定模数转换器接收和采样的信号质量的关键部分,对该环节的设计必须予以重视。

[1] 袁光德,李文林.电子技术及应用基础[M].北京:北京国防工业出版社,2007.

[2] Analog Devices.80MSPS/105MSPS/125MSPS,16-bit,1.8V,switched-capacitor AD9268 data sheet[EB/OL].(2009-09-xx)[2017-01-15]http://www.analog.com.

[3] NEWMAN E, REEDER R. AN-827, a resonant approach to interfacing amplifiers to switched-capacitorADCs[EB/OL].(2006-01-xx) [2017-01-15]http://www.analog.com/media/cn/technical-documentation/technical-articles/AN-827_cn.pdf.

[4] REEDER R.AN-935,Designing an ADC transformer-coupled front end[EB/OL].(2007-09-xx)[2017-01-15]http://www.analog.com/media/cn/technical-documentation/technical-articles/ AN-935 cn.pdf.

[5] 谢宏,李亚男,夏斌,等.基于ADSl299的可穿戴式脑电信号采集系统前端设计[J].电子技术应用,2014,40(3): 86-89.

Transformer coupling design of dual-channel analog-to-digital converter AD9268

Wang Li, Yang Shiyi

(China Airborne Missile Academy, Luoyang 71009, China)

ADC is the key part in signal receiving and sampling circuit of analog-to-digital converter. This article introduces how to produce a high performance ADC circuit using AD9268 with properly designed pretreatment, reference clock and transformer-mach-coupling circuit.

transformer; impedance; ddifferential mode; coupling

V19; TN79+2

A

10.19358/j.issn.1674- 7720.2017.14.009

王丽,杨士义.双通道模数转换器AD9268的变压器耦合设计[J].微型机与应用,2017,36(14):26-27.

2017-01-17)

王丽(1983-),女,硕士研究生,主要研究方向:雷达导引头信号处理研究。