基于TS201图像处理平台的链路口通信方法

2017-07-27林一楠李传传

林一楠+李传传

摘要:针对高速图像数据传输和处理的应用平台,设计了一款嵌入式图像处理系统,采用基于TS201的DSP+双FPGA的系统架构。该系统可以同时处理不同传感器来源的图像(如星敏、红外等),而且具有体积小、使用灵活、功耗低以及性能高等优点。在设计时对芯片选型进行了分析,并给出了图像处理系统总体的通信结构——关键是DSP和FPGA间的链路口通信,同时给出了数据传输具体的实现方案,最后通过仿真验证了该设计平台的功能,肯定了其实用性。

关键词:链路口;图像处理;TS201;双DSP;双FPGA

随着图像处理技术日益发展,人们需要采集的图像也越来越大,内容也更丰富,此时对图像处理平台的处理速度以及传输速度也有了更高要求。考虑到成本、性能、开发难易程度,同时基于FPGA和DSP图像处理平台的高灵活度、强实用性、高可靠性,本文设计了一种采用了基于TS201的双DSP+双FPGA系统架构的嵌入式图像处理系统。由于该DSP有着丰富的内外资源及外设接口,能够将处理器微型化专业化并且支持内部高速缓存,数据处理速度很快且基本上能够满足本应用需求。

链路口通信的使用不但能减轻DSP的总线上的传输速度和压力,同时与FPGA的有着相对较少的连接,所以链路口的使用为FPGA和DSP的实时数据通信提供了极大的便利,因而对两者间链路口通信进行设计和实现也是发挥高速图像数据处理的关键所在。

1图像处理平台的设计

本文给出一款同时具有高速图像传输及处理的图像处理平台。该嵌入式图像处理系统采用基于TS201的双DSP+双FPGA的系统架构,可以同时处理不同传感器来源的图像(如星敏、红外等),而且该平台具有体积小、使用灵活、功耗低以及性能高等优点。

FPGA的特点是完成一些非高难度而计算量又比较大的处理,在本平台中FPGA需要完成图像处理算法之外的大部分数据操作,而且本系统需要DSP和FPGA协同工作以达到优势互补的效果,因此对核心器件FPGA要求包括具有较高帧频图像传输能力,高速数据缓存能力,一定的算法处理能力,再综合功耗以及成本,最终FPGA采用XILINX公司的XC6SLXl00-3CSG484I芯片。该FPGA芯片具有338个普通I/0接口169个可编程单端或差分对,包含有101261个逻辑单元,可以说有着很好的片上逻辑资源。

系统的DSP采用ADI公司的TigerSHARC系列芯片TS201,它是ADI公司2003年分布的TigerSHARC新成员,其内核的工作频率最高可以达到600MHz,以1.6ns为一个指令周期,大大加速了芯片的处理速度,本系统中图像处理算法复杂度不高,一般DSP工作在400~500MHz就足够用。ADSPTS201的主要优点有:1)具有了一定的并行处理的能力从而满足高速处理的需求。2)具有4个链路口,能够提供额外的4位全双向10能力,并且还能以双倍速率锁存数据(因为其在CCLK时钟上升沿和下降沿都能锁存数据)。

此设计中DSP和FPGA之间的通过链路口连接,传输速率为1GB/s,普通差分I/O接口传输数据速率最高1080Mb/s,完全能够满足传输需求,所以选择LX系列。根据I/O数量的关系选择XC6SLX100-3CSG484I芯片:338个I/O口,169个可编程单端或差分对,101261个逻辑单元。

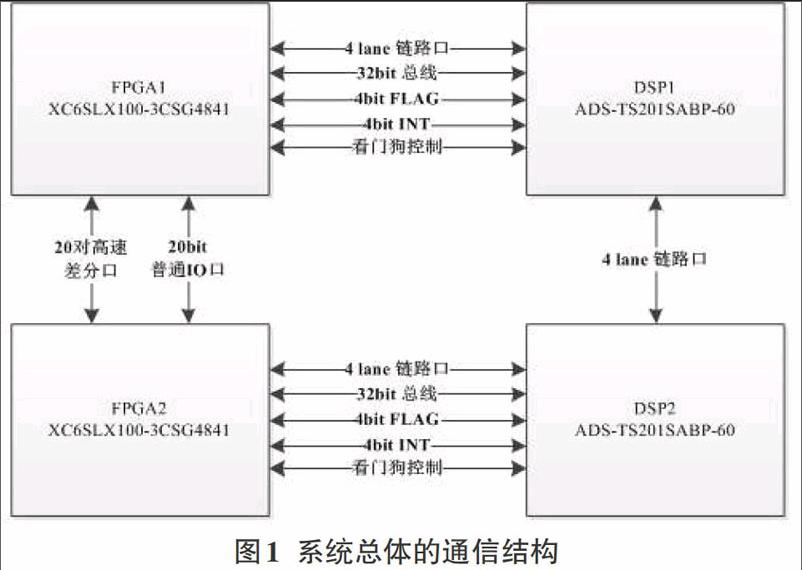

本图像处理平台的基本通信结构如图1所示。

2 DSP、FPGA间链路口通信设计

由于图像处理平台对数据的高速传输有着越来越高的需求,而链路口为数据传送提供了高速、独立的通信机制,故如何设计链路口之间的通信是高速数据传输的有力保障。

ADSP TS201TigerSHARC的每个链路口都由数据线和控制线组成的,其中数据线是4位双向的能实现双数据率传输技术的差分数据线,控制线是由3个控制信号组成的。设计选用上升沿和下降沿均对数据进行锁存与驱动的双倍数据速率传输模式。其链路口结构如图2所示。

TS201芯片的链路口传输方式可以是4位并行方式。,也可选择1位传输,其中每个通信通道都可达4位,是通过LxCLK-OUTP/N,LxACKI,LxCLKINP/N和LxACKO信号来进行控制控制,LxBCMPI和LxBCMPO则用于描述块传输已经完成。由于链路口通信为LVDS的差分连接模式,考虑到LVDS信号对走线以及器件之间的连接相当严格,为了达到匹配的目的需要在接收方内部加100Ω的端接电阻,此外印制电路板连线要匹配,保证所有数据引脚和时钟引脚有相同的延迟,其他布线原则与上述LVDS布线规则相同。

多DSP处理系统中,TS201使用链路口进行处理系统之间的互联的,按互联方式分为紧耦合和松耦合,紧耦合方式是通过外部总线来实现DSP相互之间以及DSP和其他资源之间的互联,紧耦合方式的优点是数据吞吐带宽大,软件操作简单,缺点是电路设计复杂,松耦合方式则是通过特殊端口来实现DSP之间以及DSP与其他资源之间的互联,比如说链路口、握手信号、标志等形式,优点是电路设计简单,易于实现。本图像处理平台,两个子系统DSP之间的通信则是采用了松耦合的方式,实现之间的点对点通信。

具体而言,本图像处理平台是通过链路口0进行DSP之间的互联,使得两个DSP之间可以进行数据交换,通过链路口1进行DSP与FPGA之间的连接,用于DSP与FPGA之间进行有序的数据交换,而未被用到的链路口2、链路口3做闲置处理即加高电平。并且两个独立的子系统之间FPGA与FPGA之间也建立者通信关系,他们采用的是I/O差分对之间的连接,主要实现辅助DSP通信的作用。

3 TS201链路口和DMA传输实现

ADSP TS201片上有四个完全独立的链路口,每一个链路口独立地进行接收和发送操作,每个鏈路口都是由4位双向差分数据线和另外3个控制信号组成。通信的时候可以选1bit模式或者4bit模式,链路口通信为LVDS的差分连接模式,是完全的双向通信,即在发射数据的同时可从对方接收数据,链路口的时钟最高可达核内的时钟速度,能够拥有更高的数据吞吐量。本系统外部输入时钟(SCLK)为80MHz,经过SCLKRAT2-0进行比率设置,比率为5得到最终内核时钟400MHz,DSP与FPGA之间通过链路口1进行的连接,用于DSP与FPGA之间进行有序的数据交换。

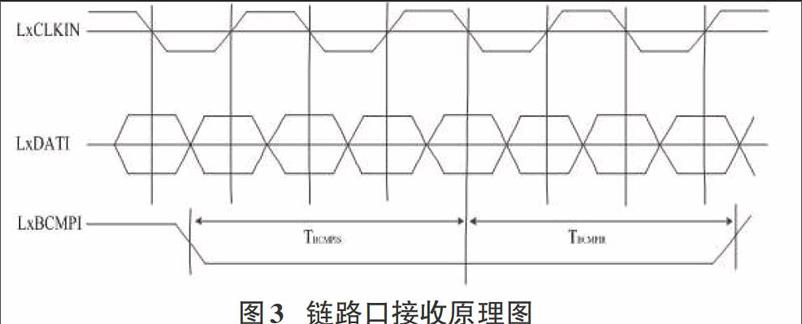

数据通信时,可以由处理器直接控制链路口,也可以用DMA控制器控制链路口,并且能够拥有双倍的数据速率,这是因为链路口在时钟的上升沿和下降沿都可对数据进行锁存和驱动。如图3为4位模式链路口通信协议,4位模式下传输4字需要16个时钟。

在本系统中图像由FPGA发向DSP的时候,FPGA需要检测两个信号,一个是设置的FLAG0握手信号,另一个则是Lx-ACKI信号,FLAG0握手信号是由DSP程序控制产生的,而Lx-ACKI信号则是链路口配置完之后,接收缓冲器为空,接收通道初始化正常后,由DSP芯片自动产生的。当这两个信号都有效时,DSP可以进行收图,此时随着LxCLKIN信号开始数据传输。

并且本系统中按照4bit进行接收,则其规则如图所示,第一个数据(4bit)在链路口时钟的上升沿进行采集,最后一个数据(4bit)在下降沿采集,而且链路口一个数据包是128bit的,也就是所谓的4字传输,当满一个数据包的时候才会接收一次,接收的时候,一般数据是接收缓冲器为空,才会将数据从接收移位寄存器完整的4字移入,如果接收缓冲器满着,会将接收移位寄存器的数据拷贝到临时接收缓冲器中,直到接收器空下来。

需要额外注意的是LxBCMPI信号,这个块传输结束标志信号是由FPGA产生的,一帧496X496的图像按照一行或者若干行进行发送的时候,可以设置此信号,表示这一块传输完成。比如在本系统中按照一行进行块传输,则FPGA需要在最后4个字传输的第一个LxCLKIN的上升沿将LxBCMPI信号拉高,这是非常重要的一个设置。如图4为FPGA和DSP之间的握手流程:

在图像进行传输的时候,可以利用TS201的DMA传输方式,将数据传输作为后台任务操作,由于不占用内核时间资源此时DSP核可以进行其他操作。此款DSP提供了14个DMA通道,链路口专用的通道8个,通道4和通道8分别对应着链路口0的发送通道和接收通道。由此也可以看出链路口的发送和接收是独立的,可以同时进行,并且DMA的传输数据流具有方向,需要对其进行设定。TS201提供了便利的设置方法,只需重点设置传输控制块寄存器(TCB),如图5所示TCB是一个128位的四字组寄存器:

DP寄存器包括了DMA传输的所有控制信息,参考TCB DP寄存器的含义选择所需要的传输方式进行设置即可。

对于链路口DMA传输,只需要设置好TCB控制寄存器,一旦建立和使能DMA模块,数据在握手信号控制下就可以自动被接收到指定位置,这个传输过程直到块传输结束,或者未设置块传输的时候,完成整个约定好长度的数据传输。如果TCB设定允许在块传输结束后产生一个DMA中断,以及正确的将DMA中断写入中断向量表,且中断被使能,则整块数据传输完成后,可以正常响应DMA中断。本系统中在一行数据传输完之后会进入DMA中断的服务子程序,由于非自动DMA根据TCB编程和请求启动只完成一次DMA传输,也就是一行数据的接收,在进人服务子程序后,需要再次对TCB进行配置,以便接下来数据的接收,直至所有数据接收完毕。

进行链路口DMA接收之前,对需要先对系统的初始化以及链路口初始化,主要依靠对系统配置寄存器(SYSCON)、链路口接收控制寄存器(LRCTLX)按照需要进行配置,特别需要注意的是对链路口接收控制寄存器(LRCTLX)配置之前,要先对其进行清零初始化操作,并且每一次响应DMA中断进入DMA中断服务函数后,进行配置之前再次清链路口。这是非常重要的一个操作,否则会导致接收数据出现错误。

如图6为系统配置寄存器(SYSCON)的位定义,以及链路口接收控制寄存器(LRCTLx)位定义:

在确定完成一帧图像接收后,系统可以开始进行图像处理操作,这是为了保证图像数据的完整性,在本系统中,设置了外部IRQ0中断,当传输结束后利用帧同步信号产生中断,用于处理附加数据和帧计数,以及对行计数进行清零操作。

4实现与仿真

ModelSim作为Mentor公司在业界最优秀的HDL语言仿真软件,它提供了友好的仿真环境,是业界唯一的单内核支持Verilog和VHDL混合仿真的仿真器。

在仿真环境搭建好以后,首先对程序进行功能级仿真,验证功能是否达到要求;功能仿真正确后再进行布局布线后仿真,根据布局布线仿真的情况再对程序进行分析,调整或者修改原先的设计,以满足设计要求。

如图7,是仿真时FPGA通过链路口给DSP传输数据的时序图,能清楚地看到图像数据在控制信号及时钟信号触发下的传输过程。

随着DSP功能越来越复杂,以及开发周期越来越短,DSP系统的设计调试工作更加倚重DSP开发系统和调试工具,AD-SP提供了很好的对应开发平台,利用开发工具Visual DSP++方便地完成对DSP软、硬件进行跟踪和调试。

如图8,我们利用Visual DSP++开发平台展示了链路口成功接收的一帧图像:

5结束语

整體而言,本文设计的图像处理平台具有一定的通用性,在图像高速传输及处理方面也颇具优势,其次,系统中给出了FPGA和DSP间链路口的通信设计和传输过程的实现方法,并通过测试和仿真得到了图像的传输结果。另外,结构图中两DSP之间进行了链路口通信,虽然只是作为备用,如果有处理效率大幅度提升的需要,可以将两片DSP芯片进行并行度提高,完成2片互联从而进一步提高图像处理平台的处理性能。