双通道可重构14 bit 125 MS/s流水线ADC

2017-07-26张惠国陈珍海孙伟锋周德金于宗光魏敬和

张惠国 陈珍海 孙伟锋 周德金 于宗光 魏敬和

(1东南大学国家ASIC工程技术研究中心,南京210004)(2常熟理工学院物理与电子工程学院,常熟215500)(3中国电子科技集团第五十八研究所,无锡214035)

双通道可重构14 bit 125 MS/s流水线ADC

张惠国1,2陈珍海1,3孙伟锋1周德金3于宗光3魏敬和3

(1东南大学国家ASIC工程技术研究中心,南京210004)(2常熟理工学院物理与电子工程学院,常熟215500)(3中国电子科技集团第五十八研究所,无锡214035)

提出了一种双通道可重构14 bit 125 MS/s流水线模数转换器(ADC).该双通道14 bit ADC可工作在并行双通道14 bit 125 MS/s、时间交织14 bit 250 MS/s以及求和15 bit 125 MS/s三种模式.为抑制通道间失配误差的影响,提出一种数模混合前台校准技术.为减少ADC输出端口数目,数据输出由高速串行数据发送器驱动,并且其工作模式有1.75, 2, 3.5 Gbit/s三种.该ADC电路采用0.18 μm 1P5M 1.8 V CMOS工艺实现,测试结果表明,对于相同的10.1 MHz的输入信号,该ADC电路在14 bit 125 MS/s模式下的SNR和SFDR分别为72.5 dBFS和83.1 dB,在14 bit 250 MS/s模式下的SNR和SFDR分别为71.3 dBFS和77.6 dB,在15 bit 125 MS/s模式下的SNR和SFDR分别为75.3 dBFS和87.4 dB.芯片总体功耗为461 mW,单通道ADC内核功耗为210 mW,面积为1.3×4 mm2.

流水线模数转换器;可重构;时间交织;电流模发送器

高速高精度流水线模数转换器(ADC)是现代无线通信系统的必需模块[1-4].随着无线电接收技术不断朝着软件无线电技术迈进,新一代无线电接收系统所需要处理的频段和模式同步增加,其对所采用的硬件芯片电路的适用灵活性或者可重构性要求日益提高.对于接收系统的硬件可重构设计,针对收发天线、模拟滤波器和处理器的可重构设计研究已相当多[5-7],然而对于高速高精度ADC的可重构研究还鲜有文献报道.

对于高速高精度ADC的可重构设计,现有的实现方式主要是采用单通道ADC功能和性能重组的方式进行[8-9].该类方法通过在固定分辨率和采样速率的ADC中关闭和调整部分模块的方式实现ADC功能和性能的调整,以适应不同应用场合的需求.由于该类方法采用的是单通道ADC,整体电路重构得到的性能无法超过单通道ADC电路的性能.本文采用多通道ADC的方式进行可重构设计,所得到的可重构ADC电路的总体性能可以高于单通道ADC电路的性能.

本文采用双通道14 bit 125 MS/s流水线ADC设计了一种可工作于3种不同模式的可重构ADC电路,以适应不同的采样需求.当2个ADC内核各自独立工作时,电路为双通道的14 bit 125 MS/s流水线ADC;当2个ADC内核工作于求和模式时,电路为15 bit 125 MS/s流水线ADC;当2个ADC内核工作于时间交织模式时,电路为14 bit 250 MS/s流水线ADC.对于求和与时间交织模式来说,如何保障两通道ADC之间的参数一致性是难点,本文为解决该问题提出了一种数模混合前台校准技术,可对失调电压和增益误差的失配进行补偿.该双通道ADC电路采用1.8 V 1P5M 0.18 μm CMOS工艺进行设计并流片验证,测试结果显示其具有非常好的综合性能.

1 可重构ADC 系统结构

图1(a)为本文所设计的双通道可重构ADC系统框图.电路包括:2个14 bit 125 MS/s流水线ADC内核电路ADC 1#和ADC 2#,产生2组14 bit 量化输出数据D1和D2;一个可重构控制模块,根据配置模式对D1和D2进行交织/求和处理或者直接并行输出;一个可配置成1.75, 2, 3.5 Gbit/s三种工作模式的电流模串行输出发送器;时钟接收及产生模块,根据外部输入125 MHz采样时钟产生14 bit ADC内核所需的125 MHz非交叠多相时钟和串行输出发送器所需倍频时钟;基准电压产生及驱动模块, 提供各种偏置.

(a) 总体结构框图

(b) 单通道14 bit 125 MS/s ADC结构框图

由于所设计的可重构ADC中使用了双通道14 bit ADC,为保证时间交织和求和模式下的ADC总体性能,必须保证所使用的2个14 bit ADC的匹配一致性,因而需要对2个14 bit ADC之间的各类失配误差进行校准.通常,影响时间交织或者求和结构ADC的主要匹配误差包括:采样时钟、失调和增益误差失配.对于失调和增益误差失配,提出了一种数模混合前台校准方法,在电路上电后根据两通道ADC数字码之间的误差,计算得到误差补偿量,通过调整控制寄存器来调整ADC模拟电路的偏置参数,进而调整2个通道间的匹配一致性,在完成校准调试后固定寄存器值,电路进行正常的模数转换功能.对于采样时钟的匹配未采用校准技术,而是采用时钟占空比稳定电路(DCS)对采样时钟的上升/下降沿进行精确控制,以达到减小时钟失配误差的目的.

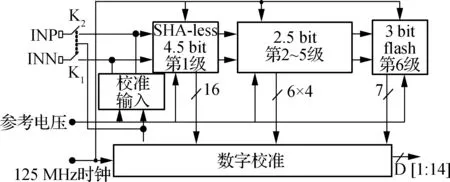

1.1 单通道14 bit 125 MS/s ADC结构

图1(b)为单通道14 bit 125 MS/s流水线ADC电路的系统结构图,图中各级流水线子级电路的具体实现见文献[10].在校准模式时,输入信号控制开关K1和K2将会断开,隔断输入模拟信号,由基准电压输出的校准输入模拟电压信号就会被连接到第1级电路的输入端,校准结束后开关导通.

1.2 可重构工作模式

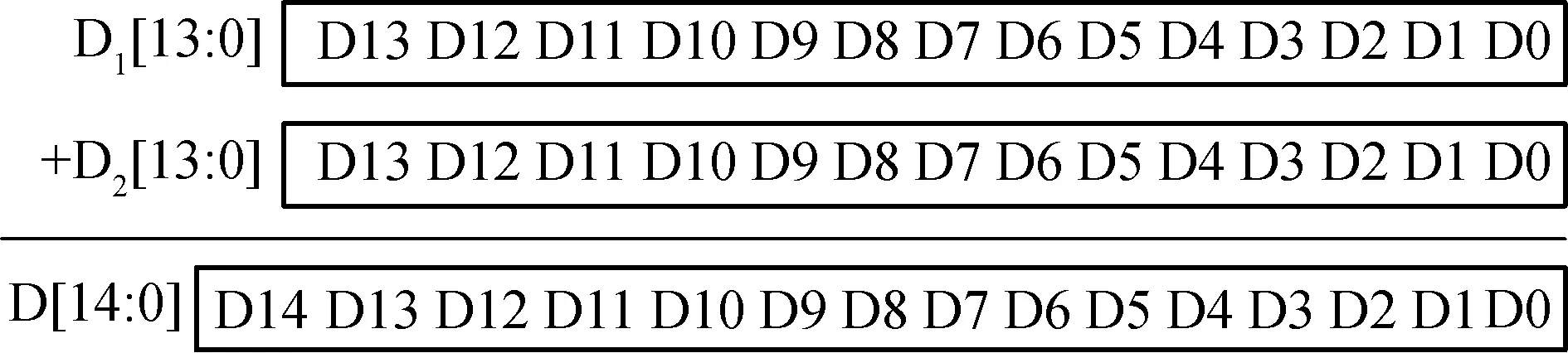

本文所设计的双通道可重构14 bit 125 MS/s流水线ADC可工作于3种不同模式,以适应不同的采样需求.当电路为双通道的14 bit 125 MS/s流水线ADC模式时,2个14 bit ADC内核各自对不同的模拟输入信号进行模数转换,对应的数据输出发送器工作在1.75 Gbit/s输出模式.当2个ADC内核工作于求和模式时,电路为15 bit 125 MS/s流水线ADC.如图2(a)所示,2个14 bit ADC内核以同相时钟对同一个输入模拟信号同时进行采样处理并得到2组14 bit 125 MS/s数据D1[13:0]和D2[13:0],再通过一个加法器求和,即可产生一个15 bit 125 MS/s数据D[14:0],此时数据输出发送器对应地工作于2 Gbit/s输出模式.当2个ADC内核工作于时间交织模式时,电路为14 bit 250 MS/s流水线ADC.如图2(b)所示,2个14 bit ADC内核以互补的相位不交叠时钟对同一个输入模拟信号进行交织采样处理,并得到2组交织的14 bit 125 MS/s数据D1[13:0]和D2[13:0],再通过一个MUX选择电路对其进行采样,产生14 bit 250 MS/s数据,此时数据输出发送器对应地工作于3.5 Gbit/s输出模式.

(a) 求和15 bit 125 MS/s模式

(b) 时间交织14 bit 250 MS/s模式

2 可重构数据发送器

由于采用了多通道ADC集成,ADC数据输出端口的数量应越小越好.为最大限度减少输出端口数量,本文所设计的可重构ADC的数据输出采用电流模(CM)输出技术,并且采用了14倍速率的串行输出数据格式,在交织模式下ADC速率达到250 MS/s,因此数据输出接口模块的最大速率达3.5 Gbit/s.由于采用serdes技术的发送器功耗较大[11-12],本文采用了简化的serdes技术,图3是发送器结构及数据的时序关系.

图3(a)为发送器的结构框图,在双通道普通模式下,校准逻辑输出的14 bit数据经过并串转换模块,转换为1.75 Gbit/s的串行数据Din,最后由CM驱动器转换成差分电流输出信号.在双通道求和模式下,由1 GHz时钟对15 bit数据进行双采样,得到2 Gbit/s的串行数据Din;在时间交织模式下,由1.75GHz时钟对14 bit数据进行双采样,得到3.5 Gbit/s的串行数据Din.

(a) 结构框图

(b) 14 bit模式输出时序图

(c) 15 bit模式输出时序图

图3(b)为14 bit数据发送器的输出数据时序示意图,串行输出数据采样时钟SCKP和SCKN为7个周期;图3(c)为15 bit数据发送器的输出数据时序示意图,串行输出数据采样时钟SCKP和SCKN为7.5个周期.

图4为ADC工作于双通道并行14 bit 125 MS/s模式下的并/串转换电路的系统框图,14 bit并行输入数据经采样后分为2组7 bit并行数据分别进入移位寄存器,再进行合并得到1.75 Gbit/s的串行数据.在时间交织模式下,时钟采样改为1.75 GHz,移位寄存器位数不变;在双通道求和模式下时,时钟采样改为1 GHz,7 bit移位寄存器被设置为8 bit.

图4 并/串转换模块结构图

3 通道一致性误差校准

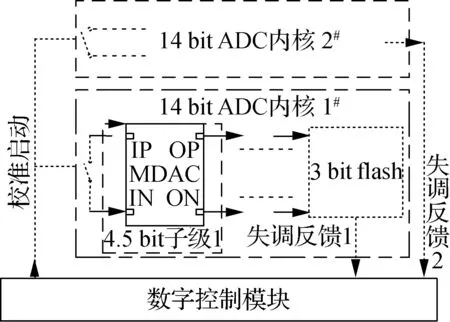

为改善时间交织和求和模式下的ADC总体性能,必须保证所使用的两通道14 bit ADC的匹配一致性,本文提出一种数模混合前台校准技术对2个14 bit ADC之间的失调和增益失配误差进行校准.2个14 bit ADC在芯片上电时在数字控制模块控制下,采用一个公用的片上基准信号进行失调和增益失配误差校准,从而具有更好的一致性,使两通道ADC之间的失配误差最小化.

3.1 失调误差校准

本文中ADC内核的失调误差校准的思想是通过人为地在ADC量化输出码上补偿一个相反的失调码来补偿,失调误差前台校准的原理如图5(a)所示.前台校准开始时,数字控制模块首先将两通道ADC中第1级子级电路的输入端短接,并连接到共模电平,此时ADC差分信号幅度应该为0.若不存在失调电压,则14 bit ADC的量化输出码应该为0,实际电路中由于失调电压的影响,ADC输出码的低几位为随机状态.数字控制模块通过多次检测ADC输出码和信号之间的差值,并将各次的差值求和求取平均值,得到两通道ADC各自的失调误差量,再将该2个平均值作为失调误差补偿量存储在对应寄存器中,在ADC正常转换模式时分别对各自通道的量化码进行补偿.由于失调校准输入都是相同的共模电压,校准的结果都是差分输入为0时数字输出也为0,因此可以保持两通道ADC的失调误差一致性.

(a) 失调误差校准

(b) 增益误差校准

3.2 增益误差校准

本文中ADC内核增益误差校准的思想是先检测两通道ADC的增益误差,然后以一个通道ADC增益为基准人为地调整另外一个通道ADC的比较器量化参考基准电压,从而调整另外一个通道ADC的增益.本文所设计的增益误差前台校准的原理如图5(b)所示.前台校准开始时,数字控制模块首先将两通道ADC中第1级4.5 bit子级电路的输入端并连接到校准信号输入模块,数字控制模块控制2个校准信号输入模块同时给两通道ADC的4.5 bit 子级电路的输入端提供校准信号.本设计中,校准电压信号为16种,最小为0,最大为满幅基准电压Vref,步进电压幅度为Vref/16.若不存在增益失配误差,对于任何一个校准输入电压,2个ADC通道输出数字量化码应该完全一样,但实际电路的输出为随机状态.

对于任何一种校准输入电压,数字控制模块通过检测2个通道ADC输出量化码和理想输出码之间的差值(增益误差反馈1和2),来判断两通道ADC的增益失调误差,再以二分法分别对2个失调校准模块中的寄存器进行调整,通过改变Vrp1和Vrn1的电压值来改变ADC内核1#的增益,通过改变Vrp2和Vrn2的电压值来改变ADC内核2#的增益,当判断增益误差反馈1和2的误差为最小时,该寄存器值将会在数字控制模块内部记录下来.当完成16种输入电压的校准过程之后,数字控制模块将会得到16组10 bit 寄存器的值,并对16组数据进行计算,得到一组最终寄存器值,然后将其写入校准信号输入模块的10 bit 寄存器中保持不变,完成增益失配误差校准.

4 测试结果

图6为本文所设计双通道14 bit 125 MS/s流水线ADC芯片电路的版图照片,电路采用0.18 μm 1P5M 1.8 V CMOS工艺.左边的模块为带隙基准(bandgap)电路,上端为基准电压缓冲驱动电路,中间部分为6级流水线子级电路,最右端为PLL、时钟占空比产生电路和3.5 Gbit/s数据发送器模块.单通道ADC面积为1.3×4 mm2,内核有源面积为1.3×2.5 mm2.

图6 ADC芯片布局

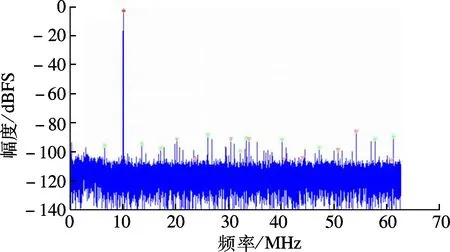

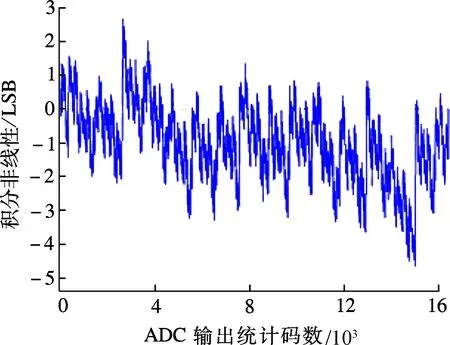

图7为本文设计的ADC的典型测试曲线,其中fin为输入信号频率.图7(a)为单通道14 bit ADC工作在125 MS/s采样率,正弦输入信号频率10.1 MHz时的测试结果,测得信噪比(SNR)为72.5 dBFS,无杂散动态范围(SFDR)为83.1 dB.图7(b)为15 bit 求和模式下的FFT结果,可以看出SNR为75.3 dBFS,SFDR为87.4 dB,失调和增益失配误差的影响得到较好抑制.图7(c)为ADC工作在14 bit 250 MS/s模式下的FFT测试结果,可看出ADC输出谐波有一定增大,SFDR下降为77.6 dB,原因在于本设计未采用时钟失配校准技术,250 MHz时钟失配相对明显.图7(d)和(e)为14 bit ADC工作在125 MS/s采样率下的线性度曲线,DNL为-0.72~+0.65 LSB,INL为-4.6~+2.7 LSB,INL的最大误差发布位置与前端4.5 bit 子级电路采用的16个比较器的量化区间对应.

(a) fin=10.1 MHz@14 bit 125 MS/s

(b) fin=10.1 MHz@15 bit 125 MS/s

(c) fin=10.1 MHz@14 bit 250 MS/s

(d) INL @14 bit 125 MS/s

(e) DNL@14 bit 125 MS/s

图8(a)、(b)为本文所设计3.5 Gbit/s串行输出接口的眼图及时钟抖动统计图.由图8(a)可看出差分信号摆幅为800 mV,“眼眶”清晰,由图8(b)可知抖动峰峰值为100 ps.ADC样片在250 MS/s采样率时总体功耗为461 mW,单通道ADC内核功耗为210 mW,其中3.5 Gbit/s串行数据发送器的功耗为32 mW.

(a) 3.5 Gbit/s时的眼图

(b) 3.5 Gbit/s时的抖动

表1总结了本文所设计ADC在3种不同工作模式下的性能测试结果.表2为近年来文献报道的14 bit 高速流水线ADC与本文设计的流水线ADC性能的对比,可看出,本文的ADC有较好的的动态性能,功耗适中.

表1 ADC不同模式下性能总结

表2 ADC性能对比

5 结语

本文采用双通道14 bit 125 MS/s流水线ADC设计了一种可工作于3种不同模式的可重构ADC电路.该双通道14 bit ADC可工作在并行双通道14 bit 125 MS/s、时间交织14 bit 250 MS/s以及求和15 bit 125 MS/s三种模式;为抑制通道间失配误差,采用了一种数模混合前台校准技术;为减少ADC输出端口数目,数据输出由高速串行数据发送器驱动.该ADC电路采用0.18 μm 1P5M 1.8 V CMOS工艺实现,对于相同的10.1 MHz的输入信号,在14 bit 125 MS/s模式下的SNR为72.5 dBFS,在14 bit 250MS/s模式下的SNR为71.3 dBFS,在15 bit 125 MS/s模式下的SNR为75.3 dBFS.测试结果表明,所设计的可重构ADC在不同的工作模式下均可以实现良好的性能,实现了比单通道ADC性能更高的可重构ADC.

References)

[1]Ali A M A, Dillon C, Sneed R, et al. A 14-bit 125 MS/s IF/RF sampling pipelined ADC with 100 dB SFDR and 50 fs jitter[J].IEEEJournalofSolid-StateCircuits, 2006, 41(8): 1846-1855. DOI:10.1109/jssc.2006.875291.

[2]Ali A M A, Morgan A, Dillon C, et al. A 16b 250 MS/s IF-sampling pipelined A/D converter with background calibration[C]//2010IEEEInternationalSolid-StateCircuitsConference. San Francisco, CA, USA, 2010:292-293. DOI:10.1109/isscc.2010.5433923.

[3]Bogner P, Kuttner F, Kropf C, et al. A 14b 100 MS/s digitally self-calibrated pipelined ADC in 0.13 μm CMOS[C]//2006IEEEInternationalSolid-StateCircuitsConference. San Francisco, CA, USA, 2006: 224-225.

[4]Devarajan S, Singer L, Kelly D, et al. A 16-bit, 125 MS/s, 385 mW, 78.7 dB SNR CMOS pipeline ADC [J].IEEEJournalofSolid-StateCircuits, 2009, 44(12): 3305-3313.

[5]Wu Jigang, Srikanthan T, Schroder H. Efficient reconfigurable techniques for VLSI arrays with 6-port switches[J].IEEETransactionsonVLSISystems, 2005,13(8): 976-979.

[6]Weedon W H, Payne W J, Rebeiz G M. MEMS-switched reconfigurable antennas[C]//IEEEAntennasandPropagationSocietyInternationalSymposium. Boston, MA, USA, 2001:654-657.

[7]Brown E R. RF-MEMS switches for reconfigurable integrated circuits[J].IEEETransactionsonMicrowaveTheoryandTechniques, 1998, 46(11): 1868-1880. DOI:10.1109/22.734501.

[8]Chandrashekar K,Corsi M,Fattaruso J,et a1.A 20-MS/s to 40-MS/s reconfigurable pipeline ADC implemented with parallel OTA scaling[J].IEEETransactionsonCircuitsandSystemsⅡ:ExpressBriefs, 2010, 57(8):602-606. DOI: 10.1109/TCSII.2010.2050948.

[9]Taherzadeh-Sani M, Hamoui A A. A reconfigurable and power-scalable 10-12 bit 0.4-44 MS/s pipelined ADC with 0.35-0.5 pJ/step in 1.2 V 90 nm digital CMOS[J].IEEETransactionsonCircuitsandSystemsⅠ:RegularPapers, 2013, 60(1): 74-83. DOI:10.1109/tcsi.2012.2215712.

[10]陈珍海, 于宗光, 魏敬和, 等. 采用1.75 Gbps串行发送器的低功耗14位125 MSPS ADC[J]. 电子测量与仪器学报, 2017, 31(1): 132-138. DOI:10.13382/j.jemi.2017.01.019. Chen Zhenhai, Yu Zongguang, Wei Jinghe, et al. Low power 14-bit 125 MSPS ADC with 1.75 Gbps serial transmitter[J].JournalofElectronicMeasurementandInstrumentation, 2017, 31(1): 132-138. DOI:10.13382/j.jemi.2017.01.019.(in Chinese)

[11]Fukuda K, Yamashita H, Ono G, et al. A 12.3-mW 12.5-Gb/s complete transceiver in 65-nm CMOS process[J].IEEEJournalofSolid-StateCircuits, 2010, 45(12): 2838-2849. DOI:10.1109/jssc.2010.2075410.

[12]Kossel M, Menolfi C, Weiss J, et a1. A T-coil enhanced 8.5 Gb/s high-swing SST transmitter in 65 nm bulk CMOS with <-16 dB return loss over 10 GHz bandwidth [J].IEEEJournalofSolid-StateCircuits, 2008,43(12):2905-2920. DOI:10.1109/jssc.2008.2006230.

[13]Zhao N, Luo H, Wei Q, et al. A 14-bit 100-MS/s 85.2-dB SFDR pipelined ADC without calibration[J].JournalofSemiconductors, 2014, 35(7): 075006. DOI:10.1088/1674-4926/35/7/075006.

[14]Ao K, He Y J, Li L, et al. A 14-bit 100 MS/s pipelined A/D converter with 2b interstage redundancy[C]//2014InternationalSymposiumonIntegratedCircuits. Singapore, 2014:83-86. DOI:10.1109/isicir.2014.7029486.

[15]Li W T, Li F L, Yang C Y, et al. An 85 mW 14-bit 150 MS/s pipelined ADC with a merged first and second MDAC[J].ChinaCommunications, 2015, 12(5): 14-22. DOI: 10.1109/CC.2015.7112040.

[16]Zheng X Q, Wang Z J, Li F L, et al. A 14-bit 250 MS/s IF sampling pipelined ADC in 180 nm CMOS process[J].IEEETransactionsonCircuitsandSystemsⅠ:RegularPapers, 2016, 63(9): 1381-1392. DOI:10.1109/tcsi.2016.2580703.

Dual-channel reconfigurable 14 bit 125 MS/s pipelined ADC

Zhang Huiguo1,2Chen Zhenhai1,3Sun Weifeng1Zhou Dejin3Yu Zongguang3Wei Jinghe3

(1National ASIC System Engineering Technology Research Center, Southeast University, Nanjing 210004, China) (2School of Physics and Electronic Engineering, Changshu Institute of Technology, Changshu 215500, China) (3No.58 Research Institute, China Electronic Technology Group Corporation, Wuxi 214035, China)

A dual-channel reconfigurable 14 bit 125 MS/s pipelined ADC(analog to digital converter) is presented.The dual channel 14 bit ADC can work in parallel dual 14 bit 125 MS/s mode, time interleaved 14 bit 250 MS/s mode, and sum 15 bit 125 MS/s mode. To reject the influence of the channel mismatch error, a mix-signal for-ground calibration technique is proposed. To reduce the digital output pins, the high speed serial transmitter is introduced to drive the digital output code, which can work in 1.75, 2 and 3.5 Gbit/s modes. The ADC is fabricated with 0.18 μm 1.8 V 1P5M CMOS(complementary metal oxide semiconductor) technology.Test results show that the ADC achieves the signal to noise ratio (SNR) of 72.5 dBFS and spurious free dynamic range (SFDR) of 83.1 dB for parallel dual 14 bit 125 MS/s mode, the SNR of 71.3 dBFS and SFDR of 77.6 dB for time interleaved 14 bit 250 MS/s mode, the SNR of 75.3 dBFS and SFDR of 87.4 dB for sum 15 bit 125 MS/s mode, with 10.1 MHz input at full sampling speed. The ADC consumes the total power of 461 mW, while the single 14 bit ADC core consumes the power of 210 mW and occupies an area of 1.3×4 mm2.

pipelined analog-to-digital converter; reconfigurable; time-interleaved; current mode transmitter

10.3969/j.issn.1001-0505.2017.04.004

2016-11-15. 作者简介: 张惠国(1978—),男,博士,副教授;孙伟锋(联系人) ,男,博士,教授,博士生导师, swffrog@seu.edu.cn.

国家自然科学基金资助项目(61474092)、安徽高校自然科学研究重点资助项目(KJ2017A396)、教育部留学回国人员科研启动基金资助项目.

张惠国,陈珍海,孙伟锋,等.双通道可重构14 bit 125 MS/s流水线ADC[J].东南大学学报(自然科学版),2017,47(4):649-654.

10.3969/j.issn.1001-0505.2017.04.004.

TN453

A

1001-0505(2017)04-0649-06