基于ARM内核的计时器设计

2017-07-25张先波奥托尼克斯电子嘉兴有限公司

张先波 奥托尼克斯电子(嘉兴)有限公司

基于ARM内核的计时器设计

张先波 奥托尼克斯电子(嘉兴)有限公司

本设计所涉及的是一款计时器产品,其基于ARM内核,构建了计时器共用一个端口读写控制器与FPGA中央控制器进行数据通信。计时器内部工作是相互独立的,通过使用地址映射存储器使得计时器的指令执行更加高效;本设计还对中央控制器与计时器的通信时序和通信格式进行了优化,便于中央控制器对计时器的控制与测试。

ARM内核 计时器 读写时序

ARM内部资源包括内部继电器、专用继电器、数据存储区、计时器、保持继电器等。中央控制器主要用以完成对双口RAM内部ARM写入的数据进行读出、处理、整理和写入操作。多操作位逻辑运算控制模块主要用以实现逻辑运算指令。输入存储与读取控制模块主要用以读取外部开关量的状态信息。数据输出控制模块主要用以将程序执行结果处理后驱动外部负载。

1 计时器功能分析和设计

基于FPGA的可重构技术,就是利用FPGA可以多次重复编程配置的特点,通过分时复用的方式利用FPGA内部的逻辑资源,使在时间上离散的逻辑电路功能模块能在同一FPGA中顺序实现的技术。

设计的计时器为可重构的设计,最多可设计有256个计时器,235个内部计数器。可以根据具体工程应用来设计其内部计时器的数量,以达到FPGA资源的灵活配置。

2 计时器与FPGA的通信端口设计

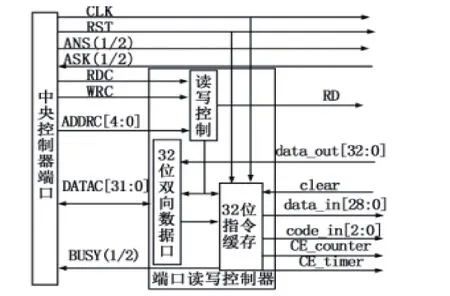

计时器通过总线的形式与FPGA中央控制器进行数据的交互,它们的工作是相互独立的,能并行地工作,相互之间不影响。它们使用相同结构和功能的端口读写控制器与中央控制器进行数据交互,在相同的时刻只能有一个模块占用总线与中央控制器进行通信。计时器与FPGA通信框图如图1所示。

图1 计时器与FPGA通信框图

端口读写控制器主要实现与中央控制器的接口,计时器根据读写时序,通过端口读写控制器实现与中央控制器的数据交换。RST复位线使用低电平复位;ADDRC是模块地址线;RDC和WRC为低电平使能;ASK(1/2)与ANS(1/2)线均为低电平有效。读写控制模块通过判断RDC和WRC以及ADDRC的状态,控制组合逻辑三态门构成的32位双向I/O口DATAC进行数据的输入或输出。端口读写控制器的32位指令缓存可以存储一条指令,由29位data_in线输出对D28-D0即指令数据,由3位code-in线输出D31-D29即指令类型。CE指令执行标志线。当存储有指令时,置BUSY(1/2)线和CE线为低电平。

图2 端口读写控制器结构图

3 计时器模块设计

由ARM与FPGA协同构建的PLC控制系统,ARM作为PLC主控制器通过数据总线、地址总线、控制总线向FPGA发送指令命令,FPGA接收到ARM的指令命令之后,通过FPGA中央控制器与计数器进行通信。

3.1 计时器设计

计时器总体结构图设计如图3所示,其中主要包含以下模块:端口读写控制器,计时器地址映射存储器,计时器存储器,计时器指令执行器,计时器控制器,1kHz脉冲生成器。

图3 计时器总体结构图

3.1.1 计时器地址映射存储器

计时器当前值和设定值在相应存储器中的存储位置与计时器本身的编号对应。当进行计时器操作或者进行计时器结果上传操作时,只需要从计时器地址映射存储器中的第一个地址开始顺序读取被使用的计时器的编号,以此编号为地址,便可以迅速地在定时存储器中找到使用了的计时器的相关数据进行操作,达到了提高系统执行效率的目的。

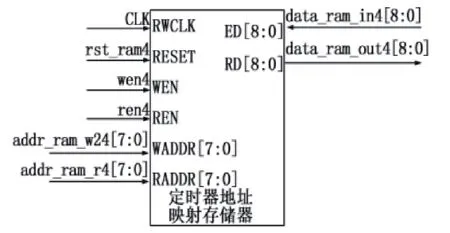

计时器地址映射存储器的封装如图4所示。RWCLK为读写时钟输入端口,读与写共用一个时钟;RESET为复位信号输入端口;WEN为写使能信号输入端口;REN为读使能信号输入端口;WADDR为写入地址输入端口;RADDR为读出地址输入端口;WD为写入数据输入端口;RD为读出数据输出端口。计时器地址映射存储器使用Libero8.3IDE提供的双端口存储器IP核生成。

图4 计时器地址映射存储器封装图

3.1.2 计时器控制器

当1kHz脉冲上升沿到来时定时控制器将会启动,当指令写入标志CE为高电平即计时器内没有指令且定时操作结束标志寄存器K1为0时,定时控制器将会执行定时操作。先通过从地址映射存储器中读取被使用了的计时器的编号;两个时钟周期后,从定时存储器中读取出的计时器的信息;第3个时钟周期后,对计时器的定时数据进行判断。操作完毕后将相关信息写入定时存储器。计时器控制器程序流程图如图5所示。

图5 计时器控制器程序流程图

4 结语

本文对ARM的计时器设计进行了阐述,并对设计所使用的软件和硬件平台及编程语言进行了说明。同时对端口读写控制器及中央控制器与定时和计数控制模块的时序进行了设计,可以根据需要来增减计时器的数量和种类。