ATCA平台中FPGA组件的可视化管理设计实现

2017-07-19李婉婉刘拥军

李婉婉,高 博,刘拥军

(信息工程大学 信息系统工程学院,河南 郑州 450000)

ATCA平台中FPGA组件的可视化管理设计实现

李婉婉,高 博,刘拥军

(信息工程大学 信息系统工程学院,河南 郑州 450000)

针对软件无线电系统中FPGA上组件的管理及与SCA架构的兼容性问题,设计了ATCA平台可视化应用开发环境中对于FPGA组件管理的框架和统一的数据传输协议。利用MFC在可视化开发界面中集成用于捕获和分析网络数据包的WinPcap,实现了ATCA平台中FPGA组件与CPU组件的互联互通。测试结果表明,可实时监测并捕获原始发送数据和经FPGA处理之后的接收数据,实现FPGA组件的便捷化、可视化管理。

数据传输协议;可视化;组件管理;FPGA;容器

软件无线电 (Software Defined Radio,SDR)正在向硬件标准化、模块化、平台化,软件通用化的方向发展[1]。为在基于软件通信架构(Software Communication Architecture,SCA)的SDR系统中使用专用处理器,同时保证软件的可移植性、互操作性,JPEO(Joint Program Executive Office)在2004年提出了(Hardware Abstraction Layer Connectivity,HAL-C)的概念。HAL-C定义了波形和平台之间的通信接口协议,但是通信环境仅是波形运行环境的一部分,因此HAL-C仅部分解决了FPGA上波形移植的问题。在2005年5月,JPEO发布了专用处理器组件移植的补充协议(CP289,Change Proposal 289)提出了容器的概念[2]。容器可以为波形提供一致的运行环境,通过实现容器可以达到波形可移植的目的。但是,如何设计容器的结构以及如何提供标准的运行环境仍然是一个问题,而CP289还没有解决这一问题。2007年,JPEO又颁布了MHAL(Modem Hardware Abstraction Layer)规范,解决了硬件处理器之间的通信问题,但并未能使专用硬件处理器上运行的软件组件与SCA兼容,即SCA框架难以对这些组件进行管理控制。基于SCA 的软件无线电系统常常要求在由GPP、DSP和FPGA共同组成的多处理器环境中运行[3]。但目前只有CPU能够提供完整的CORBA(Common Object Request Broker Architecture)运行环境,FPGA、DSP等专用处理器难以有效的支持CORBA。这就使得基于FPGA的波形组件无法通过一种简单、规范的方式与系统中其它组件建立通信,并以此为基础,将FPGA中组件的管理纳入到整个SCA架构中。

本文基于MHAL规范与容器模型,在ATCA平台上针对SDR系统对FPGA的应用需求,提出了解决专用处理器FPGA组件与通用处理器CPU组件互联互通的方法。同时,实现了对FPGA组件在CPU上的可视化管理。该方法通过在FPGA上设计容器,屏蔽了处理器之间的差异,为组件提供了标准的运行环境,使得核心框架能够对FPGA上的组件进行统一的管理和控制。

1 FPGA组件管理的框架设计

ATCA作为新一代计算平台标准,具备高吞吐量和高可靠性,其主要目标是为电信级应用提供标准化、开放化的平台体系架构。ATCA具有复杂的拓扑结构,平台中可插入多块板卡,每块板卡上最多可插入4块AMC子卡,子卡上可嵌入FPGA、DSP等专用处理器。

SCA要求使用CORBA中间件来实现各波形组件之间的通信,从而能够屏蔽底层硬件平台的差异,实现波形组件的模块化、可重用性和可移植性。而在轻量级软件通信架构中,受FPGA资源限制,实现CORBA的难度较大。因此,本文首先设计了FPGA中基于容器的组件运行环境、然后设计数据传输协议,以实现控制和数据的互联互通,并以此为基础设计了FPGA组件的管理框架。

1.1 FPGA中基于容器的组件运行环境

容器为FPGA组件提供了标准的运行环境,通过在FPGA上实现容器,可以解决不同处理器上波形组件的通信问题,提高组件的可移植性,使FPGA组件尽可能地与GPP组件一致。

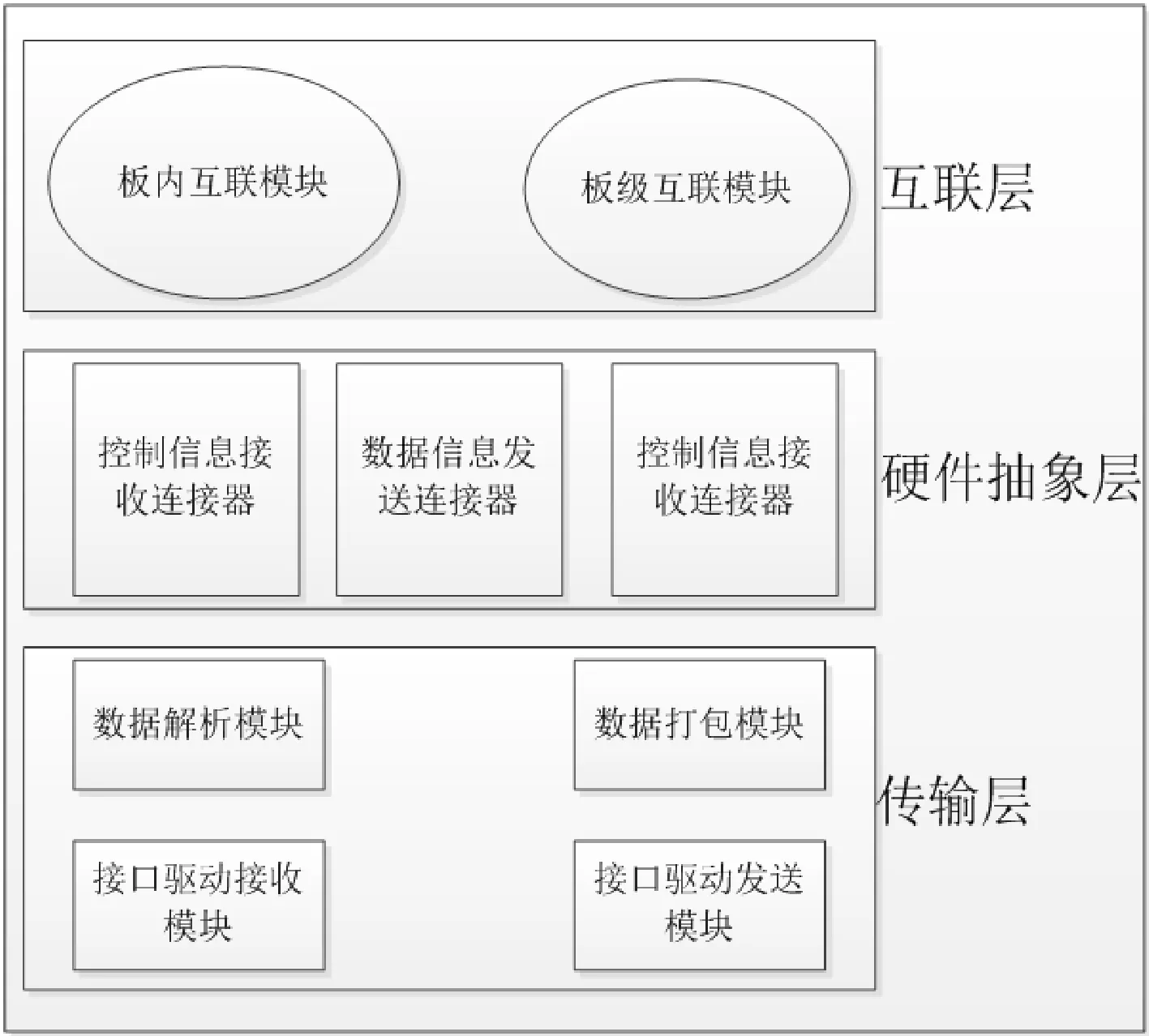

容器采用层次化方法实现,结构如图1所示,主要由互联层,硬件抽象层以及传输层构成[4]。传输层的接口驱动[5]接收模块从物理通道接收消息,不同的物理通道响应不同的驱动接收模块,数据解析模块解析从接口驱动模块接收到的消息,并将其发送到硬件抽象层[6]。控制信息接收连接器控制数据的流向,判断接收到的数据的目标地址是否为本处理器。互联层内包含板内互联和板级互联模块,板内互联模块采用直接映射的方式实现数据交换。互联层控制同一处理器或者不同处理器上不同组件间的通信,数据打包模块从硬件抽象层接收消息,并将已打包好的消息交给接口驱动发送模块。

图1 容器结构图

1.2 数据传输协议

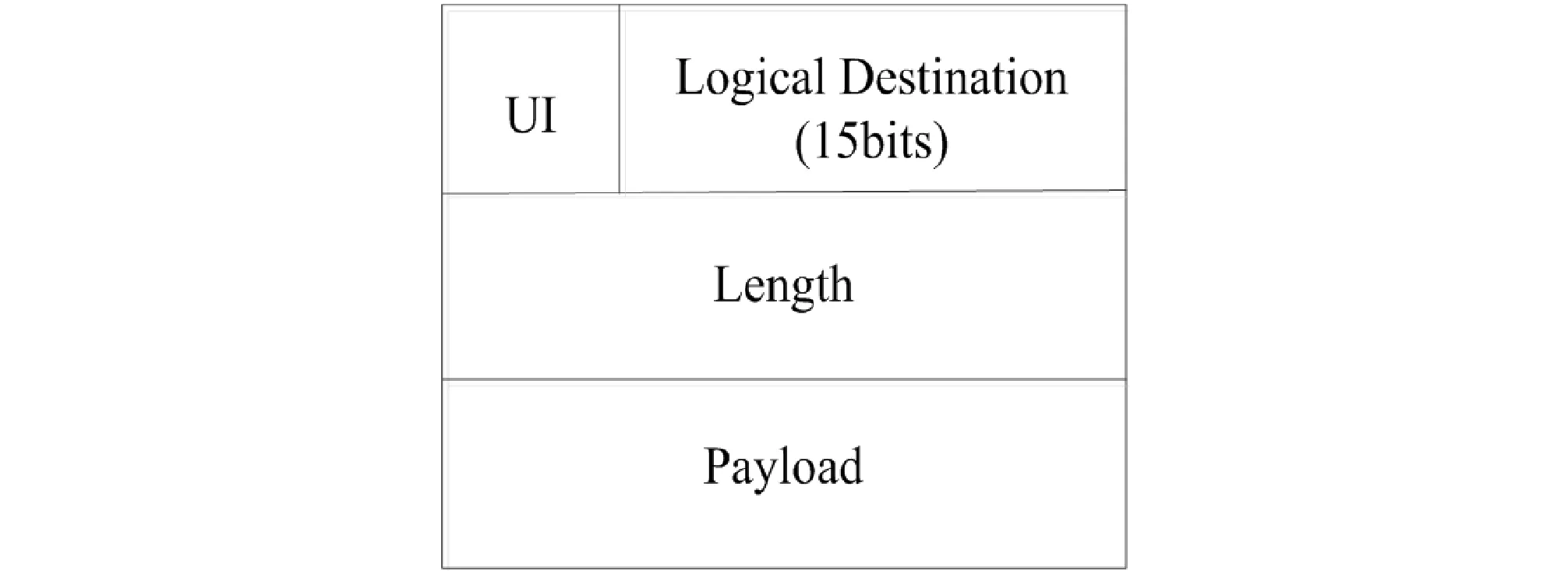

为实现不同处理器的互联,必须要有统一的数据传输协议[7-8]。平台采用层次化的数据传输协议,如图2所示。物理层位于数据传输的最底层,实现由一个处理器向另一个处理器的数据包传输。传输层和传输控制层对应于OSI的7层模型中的传输层、网络层和数据链路层,完成数据重传、路由机制、流量控制、拆包与组包等功能。传输控制层报头分为长格式数据包和短格式数据包,需根据传输层报头中状态位的值判断传输控制层报头是长格式数据包或者短格式数据包。

图2 数据传输协议结构

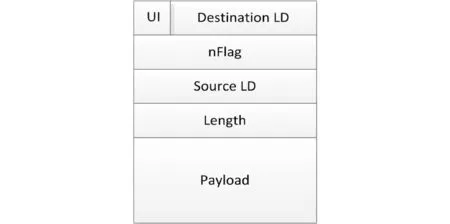

为便于不同处理器间消息的路由,实现对消息的分类管理,容器的硬件抽象层MHAL中设计了控制接收连接器,数据接收连接器和数据发送连接器。图 3是文献[9]提供的专用处理器(Specialized Hardware Processors,SHP)之间消息传输的标准格式。

图3 标准消息格式

消息UI位是内部消息流控制位,用于标识信源和信宿共享内存进行通信时消息是否处理。逻辑目的地址占15位,用于路由消息到信宿,每一个组件端口都对应一个逻辑目的地址。Length用来说明整个消息的长度,Payload是消息的数据载荷部分。

标准消息格式没有考虑到信源和信宿分别在不同处理器这一情况,也没有区分不同的消息类型,而不同组件间不仅需要数据消息通信,也需要控制消息通信[5]。为弥补标准消息格式的缺点,实现不同处理器上组件间的通信,对标准消息格式进行了扩展定义,如图 4所示,在原有的基础上增加了源逻辑地址字段和状态字段。源逻辑地址由组件所在的域号、平台号、板卡号以及处理器号共同决定,nFlag字段与传输层协议中状态标志位具有相同的定义,表明消息的类型是控制消息或者数据消息,该消息是否需要应答响应。

图4 自定义消息格式

1.3 FPGA组件管理框架

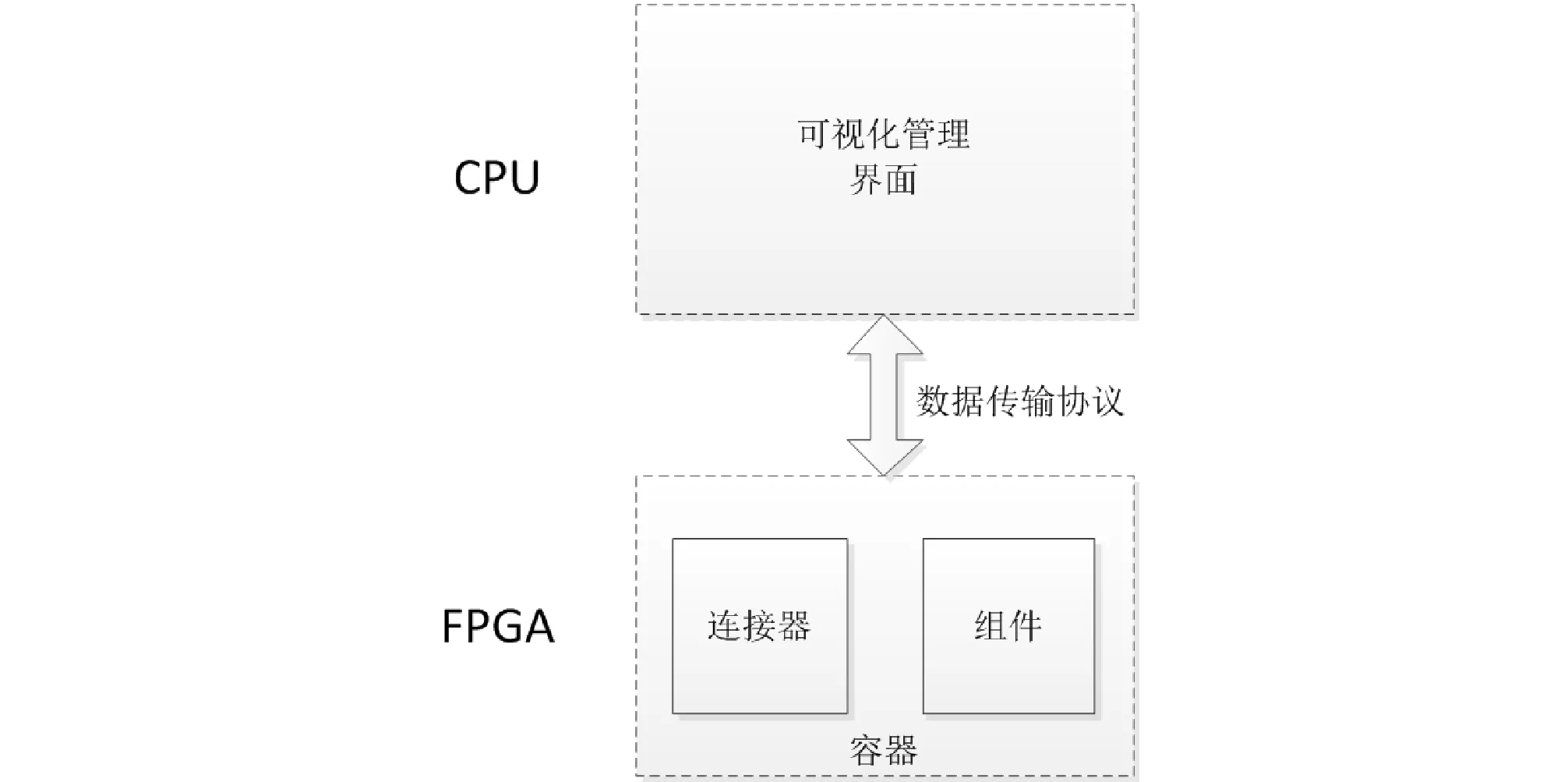

FPGA上的容器屏蔽了硬件之间的差异,为FPGA组件提供了标准的运行环境,数据传输协议为CPU组件与FPGA组件提供了标准的通信协议。在此基础上,在CPU端设计可视化管理界面,通过数据传输协议控制和配置FPGA容器中的连接器和组件。整个框架如图 5所示。

图5 FPGA组件管理框架

为便于对FPGA上组件的进行管理,主要设计3种消息:组件控制命令、应用装配消息和数据消息。

组件控制命令主要用来对组件进行控制,包括组件的初始化、启动、释放、停止等。组件控制消息使用短消息格式,且只有报头没有数据;组件端口间数据传输使用短消息格式,后面紧跟传输的数据;命令收到后均发送应答包。

应用装配消息主要是指在应用的加载和卸载过程中的一些消息,主要采用长消息格式。应用消息主要包括创建组件、设置组件端口参数、创建连接器、设置连接器参数等。

数据消息是应用组件间数据传递使用的信息,使用短格式报头,是含有数据的完整包。

连接器主要完成对组件间连接关系的配置,通过配置连接器参数,可改变FPGA上组件的目的地址,实现组件的路由转发功能,使得FPGA组件与CPU组件可互联互通。

2 可视化组件管理的实现

ATCA平台中,承载板上的FPGA处理器和计算刀片上的CPU处理器之间的物理通道采用万兆网[10]。因此,在可视化开发界面中集成用于捕获和分析网络数据包的WinPcap,实现对FPGA组件的可视化管理[11]。

如图 6所示,界面实现了FPGA组件可视化的管理,可在界面上进行FPGA程序的加载、FPGA寄存器的读写以及万兆网数据的收发等操作,并通过上述3种消息实现对FPGA上组件的管理。

图6 可视化界面

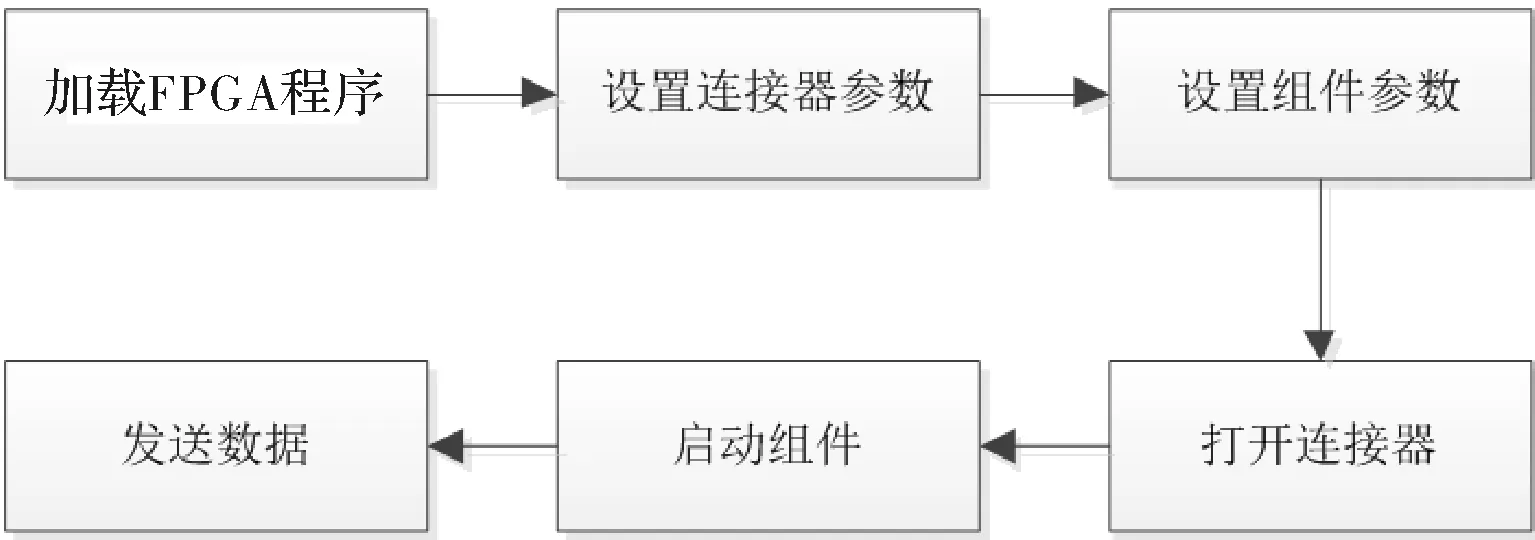

通过可视化管理软件对FPGA的示例组件进行测试,具体流程如图 7所示。

图7 应用测试流程

首先加载FPGA程序,然后利用应用装配消息配置相应组件工作模式及其对应连接器的关键参数。参数配置完成后,利用组件控制命令打开连接器,并启动组件。此时,组件可以开始接收和发送数据,实现其通信功能。最后,通过数据消息发送数据。可以通过Wireshark抓包软件实时监测捕获到的原始发送数据和经FPGA处理后的接收数据[12-14]。

基于以上的设计和流程,FPGA组件管理软件可实现CPU与FPGA组件的互联互通,同时,可视化的管理界面使得对FPGA组件的管理更加灵活、便捷。

3 结束语

本文以FPGA中用于组件管理的容器为基础,针对整个系统对于FPGA上组件的管理及与SCA架构的兼容性问题[16],基于SCA整体架构和专用处理器组件移植的补充协议CP289中的建议,设计了ATCA平台可视化应用开发环境中对于FPGA组件管理的框架和统一的数据传输协议,在实现ATCA平台中FPGA组件与CPU组件的互联互通基础上,实现了应用开发环境中FPGA组件的便捷化、可视化管理。使得FPGA芯片的管理及其应用组件的管理能够方便快捷地纳入到基于SCA的整个平台的管理系统中。

[1] González C R A, Dietrich C B, Reed J H. Understanding the software communications architecture[J]. IEEE Communications Magazine,2009,47(9):50-57.

[2] Liu Q, Cao K, Lai Y Y. FPGA software architecture for software defined radio[J].Procedia Engineering,2012(29):2133-2139.

[3] Ulversφy,Tore.Software defined radio: challenges and opportunities[J].IEEE Communications Surveys & Tutorials,2010,12(4):531-550.

[4] 孟凡惠.基于SCA的FPGA局部重配置系统的设计与实现[D].长沙:国防科学技术大学,2010.

[5] 常济崧.基于SCA的可移植FPGA波形结构及组件接口设计[D].长沙:国防科学技术大学,2009.

[6] 谭翔.基于SCA架构的SoPC设计与实现[D].长沙:国防科学技术大学,2011.

[7] 韩君妹,施峻武.软件无线电异构处理器平台互连架构设计[J].现代电子技术, 2013(15):41-44.

[8] 曹政,李磊,陈明宇.万兆以太网MAC层控制器设计与实现[J].小型微型计算机系统,2007,28(6):974-978.

[9] Joint Program Executive Office. Joint tactical radio system standard modem hardware abstraction layer application program interface[S].USA:Joint Program Executive Office,2007.

[10] 温宇辰.嵌入式光纤万兆以太网系统设计[D].大连:大连理工大学,2014.

[11] 董传刚,刘卫荣.可视化技术在雷达侦察信号分析中的应用[J].电子科技,2015,28(7):15-17.

[12] 袁阳,孟李林.基于FPGA的千兆以太网数据传输设计[J].电子科技,2016,29(2):156-158.

[13] 张诚,罗丰.基于千兆以太网的高速数据传输系统设计[J].电子科技,2011,24(1):44-46.

[14] 雍婷.基于SCA规范的PCI设备驱动设计与实现[D].长沙:国防科学技术大学,2006.

[15] 宋安.SCA平台硬件设备驱动设计与实现[D].长沙:国防科学技术大学,2005.

[16] 赵秋明,林志堂,杨莹莹,等.基于SCA的小型化核心框架研究[J].计算机测量与控制,2010,18(5):1145-1147.

Design and Implementation of Visual Management of FPGA Components in ATCA

LI Wanwan,GAO Bo,LIU Yongjun

(School of Information Systems Engineering,Information Engineering University,Zhengzhou 450000,China)

The management of FPGA components and its compatibility with SCA architecture are big problems in SDR. In this paper, based on the suggestion of CP289, a framework to manage FPGA components and standard data transfer protocol has been designed in visual application development environment of ATCA platform to achieve communication between FPGA and CPU, which integrates WinPcap by using MFC. Then this paper presents a simple and visual way to control FPGA components.

data transfer protocol;visualization;component management;FPGA; container

2016- 10- 12

国家科技支撑项目(2013BAH56F00)

李婉婉(1992-),女,硕士研究生。研究方向:电子与通信工程。高博(1972-),男,博士,副教授,硕士生导师。研究方向:平台技术。刘拥军(1979-),男,讲师。研究方向:信息与通信工程。

10.16180/j.cnki.issn1007-7820.2017.08.007

TN915.04;TP311

A

1007-7820(2017)08-024-04