基于FPGA的千兆以太网实现

2017-07-12李磊,刘宇,于帅

李 磊,刘 宇,于 帅

(西安应用光学研究所 陕西 西安 710065)

基于FPGA的千兆以太网实现

李 磊,刘 宇,于 帅

(西安应用光学研究所 陕西 西安 710065)

随着技术的迅速发展,越来越多的工程应用对以太网嵌入式设备提出了需求,因此对以太网MAC层数据处理系统的研究具有重要的现实意义。本文介绍利用以太网物理层(PHY)芯片和FPGA实现的硬件千兆网模块。其中PHY芯片作为数据传输的高速节点,处理物理层数据,而FPGA完成对MAC层数据的处理。本文研究的方法结合了FPGA的强大处理能力和PHY芯片的驱动能力,比常规CPU+MAC层模块+PHY芯片的方式有更高的效率。本文通过实验测试验证了设计的可靠性与快速性。

MAC层;PHY层;FPGA;千兆网

千兆以太网技术和如今已广泛应用的10 Mbps和100 Mbps技术一样,都使用以太网所定义的技术规范,成熟的技术规范保证了其发展的可能性。比如:CSMA/CD协议、以太网帧、全双工、流量控制以及IEEE802.3标准中所定义的管理对象等[1]。

随着技术的不断发展,千兆以太网技术作为一种高速数据传输技术,越来越多地被应用于工程之中[2-4]。同时FPGA由于其具备成本低、资源丰富以及灵活性高等特点,被广泛应用于各类应用领域的电子系统设计中。FPGA厂商为其产品提供了许多具备专用功能的核,诸如存储器、PLL、DSP核以及特定算法功能核。

使用PC平台的千兆以太网设计发已十分成熟,而嵌入式芯片的性能在近年来迅速提升,基于它们的千兆以太网设计也正处于迅速发展阶段[5]。将千兆以太网的MAC层操作使用硬核实现,可以有效提高传输性能,缩小电路面积。而目前国内外工程应用中千兆以太网主要以面向特定应用而设计的,并不通用,而cpu+软核配置MAC的方式本身又类似于PC端的开发。因此,本课题研究的全硬件实现的千兆以太网将具有很好的应用前景。

1 系统结构

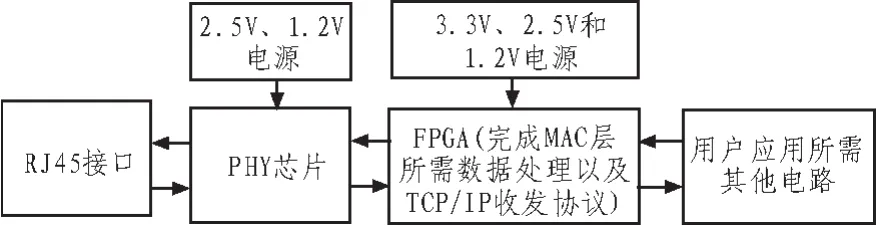

本文研究内容是基于FPGA的千兆网实现方案,主要包含以下内容:

1)MAC层数据处理;

2)PHY层数据处理;

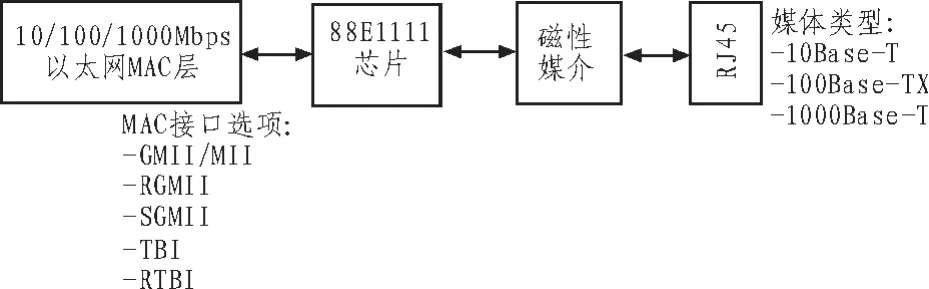

其中MAC层数据处理和TCP/IP协议采用FPGA实现,PHY层数据处理以及RJ45接口采用专用物理层芯片实现。因为物理层芯片的功耗较大,所以本文设计中为PHY层设计了独立的电源电路。系统结构图如图1所示。

图1 系统结构图

2 器件选择及其功能实现

2.1FPGA

基于FPGA的开发设计中,FPGA的选取十分重要[6]。通常需要考虑的因素有:开发工具、电气接口标准、硬件资源、封装形式、价格等方面[7]。本文使用的FPGA选取了Altera公司Cyclone IV系列的EP4CE115F23I7。具体考虑因素如下:

1)开发工具

Xilinx公司的ISE和Altera公司的QuartusⅡ两款开发工具,功能强大、操作简单,同时可以支持其所有器件的设计开发和很多第三方软件的应用,如ModleSim等,为设计者提供了便捷的设计环境。而Altera公司的QuartusII智能程度要稍微高一些。

2)价格

Altera Cyclone系列其自身定位为以更低的价格实现最强的性能。

改善独立微网频率动态特性的虚拟同步发电机模型预测控制//陈来军,王任,郑天文,司杨,梅生伟//(3):40

3)硬件资源

Cyclone IV的I/O接口众多,足以支持大部分工程设计接口需求,11万逻辑单元也可以支持较大规模的HDL代码[8]。

故本文选取了BGA封装的EP4CE115F23I7。

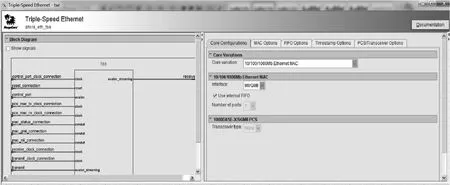

本文设计中FPGA功能包括MAC层功能实现以及TCP/IP收发协议实现。本文采用的是Quartus II 13.1开发工具,其工具MegaWizard_Plug-In提供了许多IP核[9],本文采用了三速以太网 IP核,即TSE(triple speed Ethernet)[10],实现 MAC 层数据处理。 其配置界面如图2所示。

图2 TSE核配置界面

主要配置包括以下3个配置页面:

1)Core Configuration:核类型选择,包括传输速率以及小模块组成,如MAC、PCS。接口类型,以及是否使用内部FIFO。本文选择了三速自适应MAC以及MII/GMII接口。

2)MAC Options:MAC配置选项,配置MAC模块功能,本文使用了自带的MDIO模块[11];

3)FIFO Options:FIFO存储器选项,根据应用需求的吞吐量选择深度与位宽。

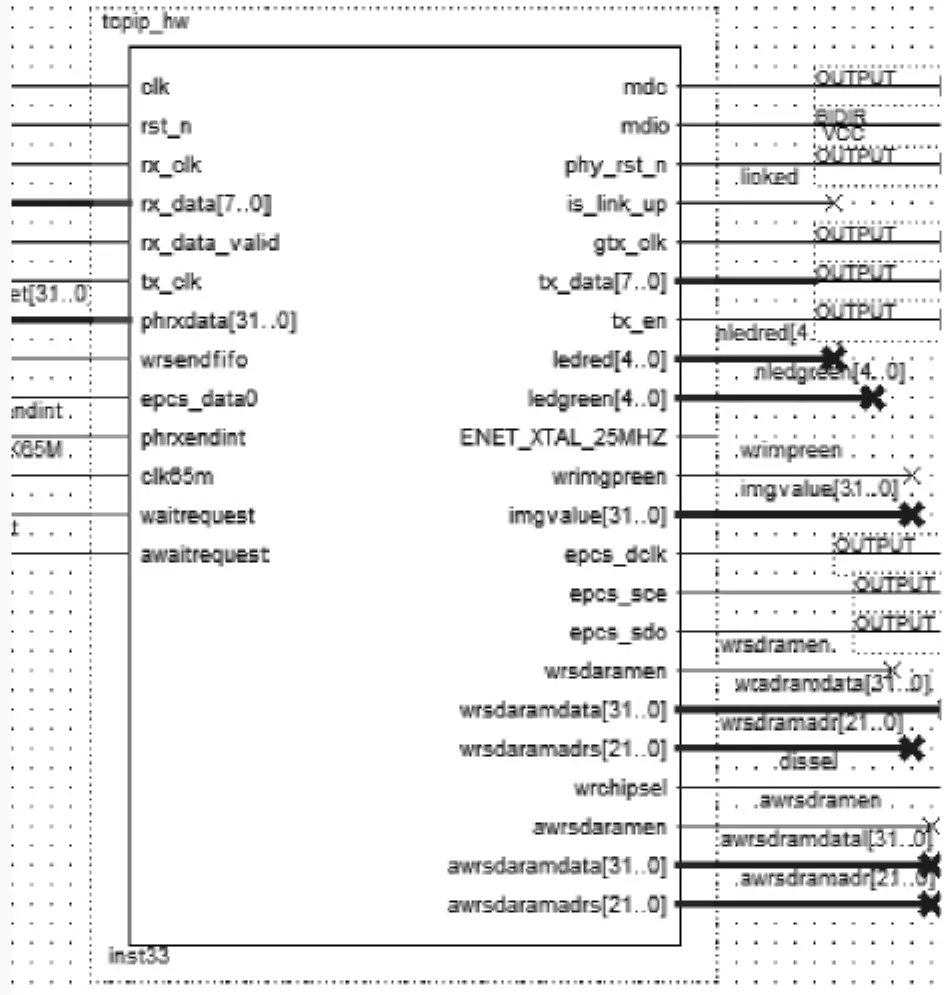

本文编写了HDL代码对PHY模块和TSE核进行了初始配置,同时设计了收发代码模块执行TCP/IP协议[12],方便用户进行数据处理。

FPGA网络模块接口如图3所示:

2.2 物理层芯片

物理层芯片的生产商有Marvell、Broadcom公司等,其主流产品为100/10 M和1000 M物理层芯片,国内虽然也有相关厂商,但技术相对滞后一些,有待发展[13]。

文中选取了Marvell公司的88E1111芯片[14],它是一款千兆以太网收发器,支持10Base-T、100Base-TX、1000Base-T的网络应用,同时可以实现多种MAC接口模式,如GMII/MII、RGMII等。88E1111具备强大的混合信号处理能力,满足去反射、去串扰、误码纠正等功能的需求。88E1111可以支持RJ45和SFP接口,即双绞线和光纤标准接口,本文选择了RJ45接口。本文组建的数据通路如图4所示。

图3 顶层模块及接口

图4 88E1111接入双绞线网络

3 系统实现与验证

本文设计的硬件平台如图5所示,其中SDRAM和PAL接口为具体应用所需。

图5 硬件平台

通过设置Loopback结合Modelsim进行仿真验证[15],可通过 TCPUDPDbg、WireShark等工具对该系统硬件进行测试。本文首先使用TCPUDPDbg工具按照640个字符“W”一包进行数据发送,对系统的可靠性进行了测试,未发现丢包。最终经背景项目实验测试可得本文设计千兆网硬件平台可稳定工作在600 Mb传输速率下。

4 结束语

千兆网系统越来越多地应用于工程设计当中,使用FPGA+PHY芯片的方案不仅提高了系统的灵活性,也加强了系统的可靠性和适用性,尤其接口更具扩展性。实验证明,本文的千兆以太网设计有效的实现了全硬件电路工作,是一种高效的传输方案。

[1]高展.以太网介质访问控制器(MAC)的研究[D].西安:西北工业大学,2004.

[2]IEEE LAN/MAN Standards Committee[R].IEEE Standard 802.3 Part 3:Carrier sense multiple access with collision detection (CSMA/CD)access method and physical layer specifications,2005:149-250.

[3]李璇,敖光良.基于FPGA的千兆以太网设计[J].网络安全技术与应用,2008(5):63-64.

[4]孙守昌.网络光功率计的研究[D].哈尔滨:哈尔滨工程大学,2004.

[5]柳利军,熊良芳.基于FPGA的千兆以太网交换芯片的设计[J].微电子学与计算机,2006,23(3):80-82.

[6]童鹏.FPGA器件选型研究[J].现代电子技术,2007:20.

[7]叶祎恒.基于FPGA的UDP/IP硬件协议栈的研究与实现[D].西安:西安电子科技大学,2010.

[8]Altera Corportion.Cyclone IV Device Handbook[DB/OL].2014.http://www.altera.com.cn.

[9]关可,梁文家,张晓博,等.EDA技术与应用[M].北京:清华大学出版社,2012.

[10]Altera Corportion.Triple speed ethernet mega core function user guide[DB/OL].2008.http://www.altera.com.cn

[11]NS,LVDS Owner’s Manual Low-Voltage DifferentialSignaling[DB/OL].2008..http://www.national.com.

[12]W.Richard Stevens,范建华.TCP/IP详解(卷 1:协议)[M].北京:机械工业出版社,2007.

[13]徐洪波,余成芳.基于FPGA的以太网MAC子层协议设计实现[J].复旦学报:自然科学版,2004(2):50-53.

[14]Marvell.Marvell-Alaska-Ultra-88E1111-GbE[DB/OL].2013.http://www.marvell.com.

[15]于斌.ModelSim电子系统分析及仿真[M].北京:电子工业出版社,2014.

Realization of gigabit ethernet based on FPGA

LI Lei,LIU Yu,YU Shuai

(Xi’an Institute of Applied Optics, Xi’an 710065,China)

With the rapid development of technology,more and more engineering applications have put forward the requirement of embedded Ethernet device.It is of great importance to research the data processing system of the Ethernet MAC layer.This paper describes a method which make use of PHY chip and FPGA to achieve the hardware gigabit network module.In this paper,PHY chip and FPGA respectively completes the data processing of PHY layer and the MAC layer.The method researched in this paper combines the powerful processing capabilitiy of FPGA and drive capability of PHY chip,which bring higher efficiency compared with the method using CPU,MAC layer module and PHY chip.In this paper,the reliability and rapidity of the design are verified by experiments.

MAC;PHY;FPGA;Gigabit ethernet

TN91

A

1674-6236(2017)12-0186-03

2016-04-07稿件编号:201604068

李 磊(1991—),男,四川成都人,硕士研究生。研究方向:光电系统测控。