基于IRIG-B码的测控时间系统的设计

2017-07-12贾振华许晓冬吕德东朱晓辉

贾振华,许晓冬,吕德东,2,张 阁,2,朱晓辉,2

(1.中国空间技术研究院通信卫星事业部 北京 100094;2.北京市卫星移动宽带通信工程技术研究中心 北京100094)

基于IRIG-B码的测控时间系统的设计

贾振华1,许晓冬1,吕德东1,2,张 阁1,2,朱晓辉1,2

(1.中国空间技术研究院通信卫星事业部 北京 100094;2.北京市卫星移动宽带通信工程技术研究中心 北京100094)

时间系统对于测控设备的正常运行和故障诊断起着至关重要的作用。IRIG-B码是国际靶场试验通用的同步时间码。本文基于IRIG-B码对某测控设备的时间系统进行设计,并在该设备中成功实现时间同步,精度可达级。与以往的各种方法相比,在解码的方案中作出了改进,利用移位寄存器实现帧同步和码元边沿提取,使得设计简单易行,具有较强的容错能力和抗干扰性。同时,本地时间的正常工作使得设备在B码异常的情况下仍然可以获得准确的时间信息,从而为数据处理、存储及事后分析提供精确的时间定位,具有灵活性,开放性,简单实用,功耗低的优点。

IRIG-B码;时间系统;VHDL;移位寄存器;解码

对于航天测控来说,时间统一系统的主要作用有[1]:标志航天实验中重要事件的时刻;统一航天测试系统的时间频率;提供对航天飞行控制所需的精密时刻。

通常时间振荡器会随着时间的产生而出现漂移,需要标准的授时系统做校准。IRIG-B码具备传输比较容易的串行码格式,速率适中,编码信息量丰富,因而得到了广泛的应用。文章介绍了一种B码的解码方案,结合本地晶振精度可达μs级。该方案在XILINX公司Virtex-7系列FPGA平台上实现,最终成功应用在某测控设备中。

1 IRIG-B格式时间码

IRIG[2]的全称为Inter Range Instrumentation Group(靶场仪器组),负责制定美国靶场定时系统的时间码标准,为靶场中的卫星导航、航天发射、导弹制导等提供标准时间。

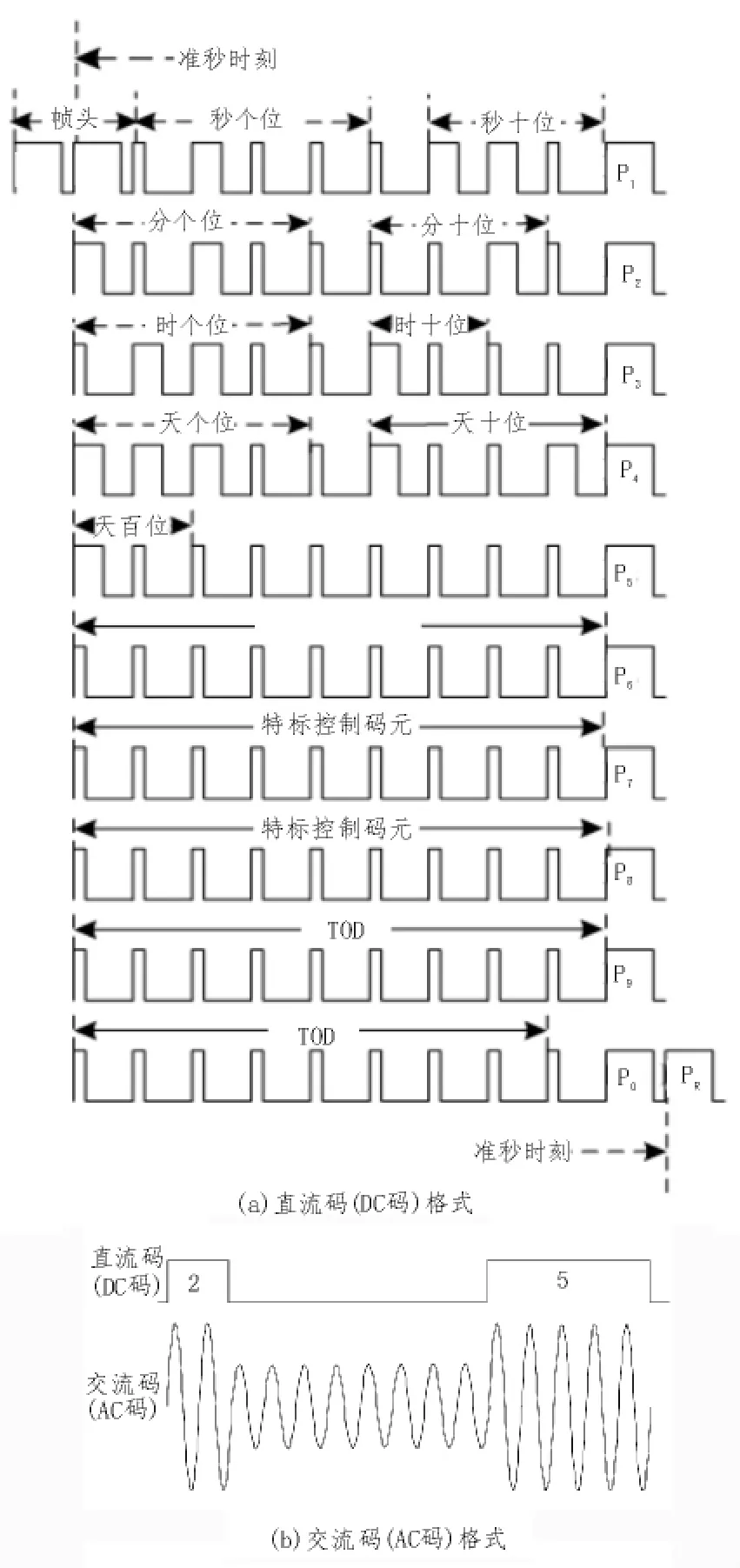

IRIG-B格式时间码[3](简称B码)包含直流码(DC码)和交流码(AC码)两种格式,是每秒一帧的时间串码,每帧包括100个码元。直流码每个码元宽度为10 ms[4]。其中,二进制“l”的脉冲时宽为5 ms;二进制“0”的脉冲时宽分别为2 ms;位置识别标志的脉冲时宽分别为8 ms。连续的两位置识别标志为准秒时刻。如图1(a)所示,表示197天16时45分32秒。交流码(AC码)是直流码(DC码)对1 kHz正弦信号进行幅度调制后形成的,如图1(b)所示。

图1 B码格式

2 时间系统总体方案设计

时间系统为设备提供绝对时间和同步脉冲信号。设备能够对交流B码和直流B码进行解码处理,准确提取出和主站同步的帧参考点,向各单元送出同步脉冲,最终将时、分、秒等时间信息以串行BCD码的形式送入计算机。在传送过程中,如果B码信号中断或者出现错误,则通过切换本地时间,将时、分、秒、毫秒信息输入计算机和其它单元模块。时间系统的总体方案设计如图2所示。

图2 时间系统总体方案设计

由于B码解调需要整个秒周期,在对IRIG-B码信号进行检测时,如果1.1 s仍未检测到帧头或找到帧头后没有电平反转 ,则认为B码信号中断或者出现错误,将解码程序复位,同时切换到本地时钟;若检测到B码后脉宽不在1ms~9ms之间,则认为B码信号出现毛刺,上报给监控系统。为了达到监测的作用,由FPGA独立产生一个计数器[5],计时1.1 s。

输出时间数据可作为时间戳打在每帧遥测数据的后面。在遥测数据接收过程中,时间信息可实时显示在上位机界面,能够为数据存储、处理和事后分析提供精确的时间定位[6],便于观察分析。

3 B码解码设计

3.1 直流码(DC码)解码方案

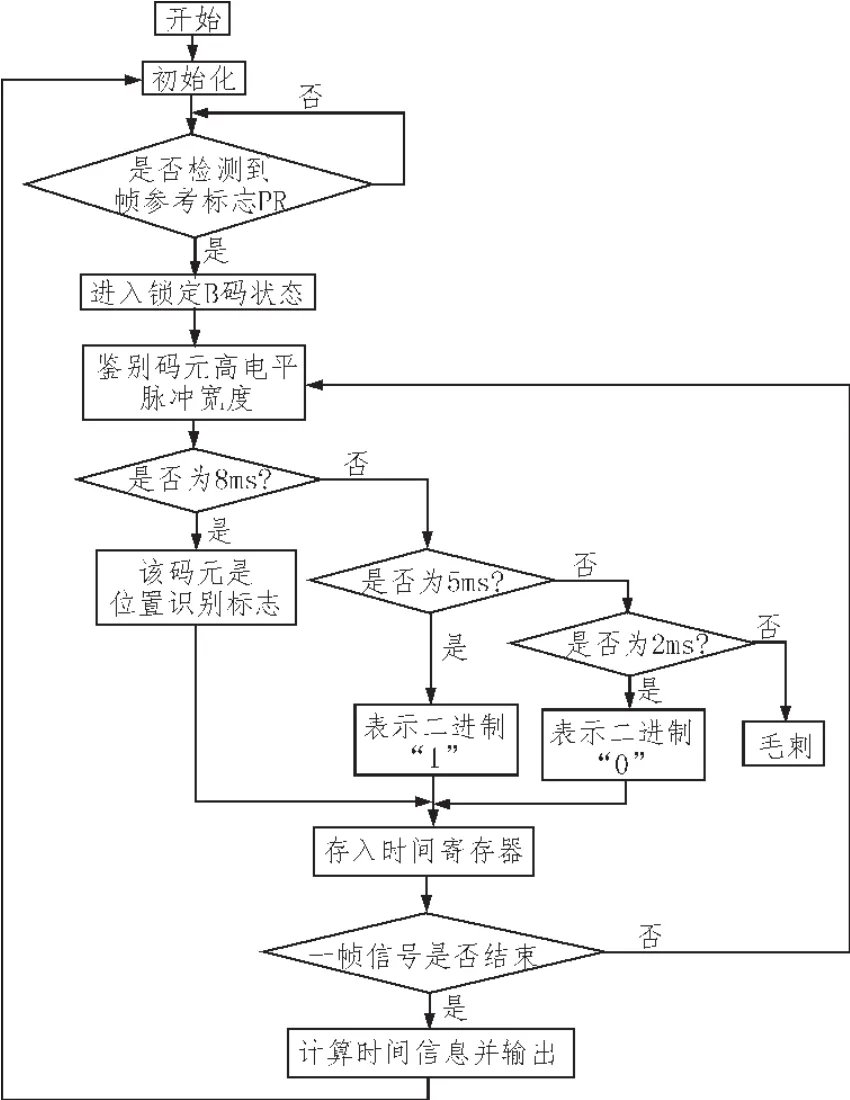

直流码解码主要包括脉宽鉴别模块,提取边沿脉冲模块,提取秒脉冲模块以及提取时间信息模块[7-8]。解码流程如图3所示。

图3 直流B码解码程序流程

1)脉宽鉴别模块

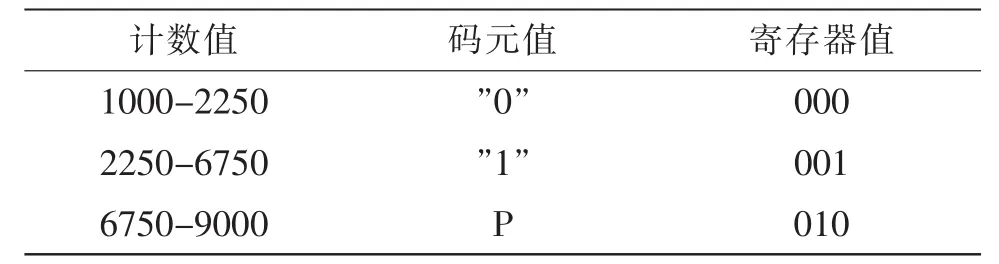

脉宽鉴别模块用于检测直流码信号的脉冲宽度[9]。计数器counter_pulse_wide在1MHz的时钟的上升沿对每个码元进行计数,在码元上升沿处清零,在码元下降沿处根据计数器的值对该码元进行判断。为避免时钟同步误差及传输或解调中受到噪声影响或外部干扰而产生毛刺或抖动,保证码元值判断的准确性,将检测门限留有一定裕度。码元值存储在寄存器pulse_width_dc_in(2 downto 0)中。 计数值、码元值与寄存器值的关系如表1所示。

表1 计数值、码元值与寄存器值的关系

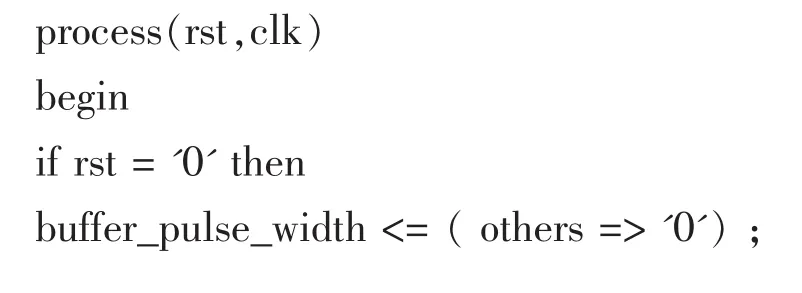

2)提取边沿脉冲模块

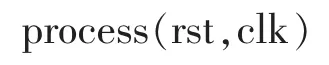

文章采用同步提取码元边沿窄脉冲的方法代替码元上升沿或下降沿等触发条件实现码元计数。为消除直流码传输过程中的毛刺、干扰造成的边沿误判,增强解码过程的容错能力,使用移位寄存器提取边沿窄脉冲。移位寄存器是一个具有移位功能的寄存器,即寄存器中所存的二进制数据或代码能够在移位脉冲的作用下依次左移或右移一个比特。提取上升沿的VHDL程序如下:

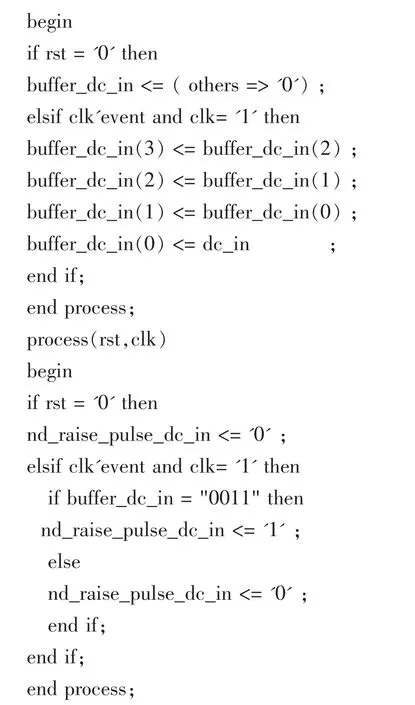

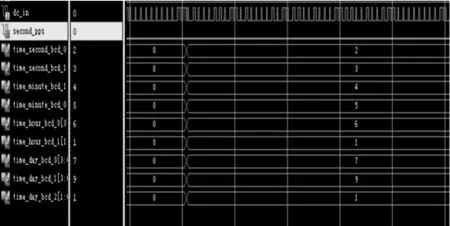

Modelsim仿真时移位寄存器的变化情况如图4所示:

3)提取秒脉冲模块

图4 边沿提取移位寄存器的变化

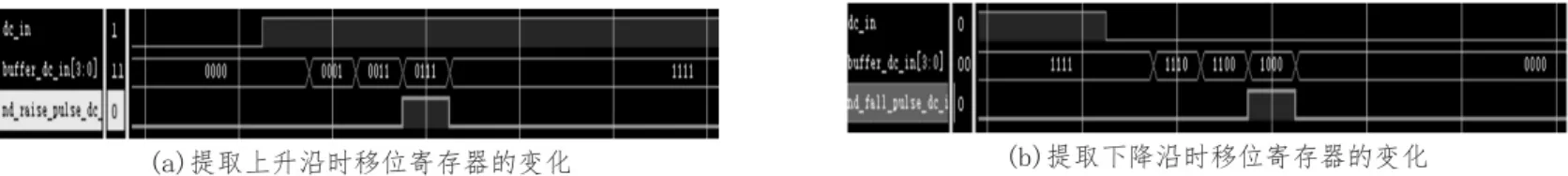

文中采用移位寄存器的方法查找帧参考标志PR,进而提取准秒时刻信号PPS。设计一个两位移位寄存器buffer_pulse_width(1 downto 0),在移位脉冲nd_fall_pulse_dc_in的作用下,依次左移,并将pulse_width_dc_in(1)赋给寄存器的最低位。当移位寄存器buffer_pulse_width=”11”时,即检测到两个连续的8ms码元,产生B码锁定的标志信号flag_lock_PP_dc_in,该信号高电平有效。VHDL程序如下:

4)提取时间信息模块

由B码的码制原理可知,B码的每一帧中第1-41个码元用来表示时间信息和位置标志信息。其中蕴含时间信息的秒、分、时、天时间信息的码元有30个[10]。定义九个寄存器分别存储秒个位,秒十位,分个位,分十位,时个位,时十位,天个位,天十位,天百位的信息。为直流解码后的Modelsim仿真时序图如图5所示,可以准确解得197天16时45分32秒,与输入的时间信息一致。

图5 直流信号解码功能仿真时序图

3.2 交流码(AC码)解码方案

由于直流IRIG-B码不适合于长距离传输,所以一般时统站与接收端距离比较远的时候,都使用交流码来传输[11-12],论文选用了Matlab7.6.0版本的软件来实现仿真设计。

交流B码是由幅度不同的正弦波组合而成的波形,直接去判断码元信息比较困难,因此对交流B码解码的核心思想,首先要把交流B码首先转换成较为整齐的直流B码,再通过对直流B码脉宽的检测,判断码元中包含的时间信息。对交流码信号进行解调时,用与调制时同幅度、同相位的l kHz正弦波与接收到的信号相乘,得到如下结果:

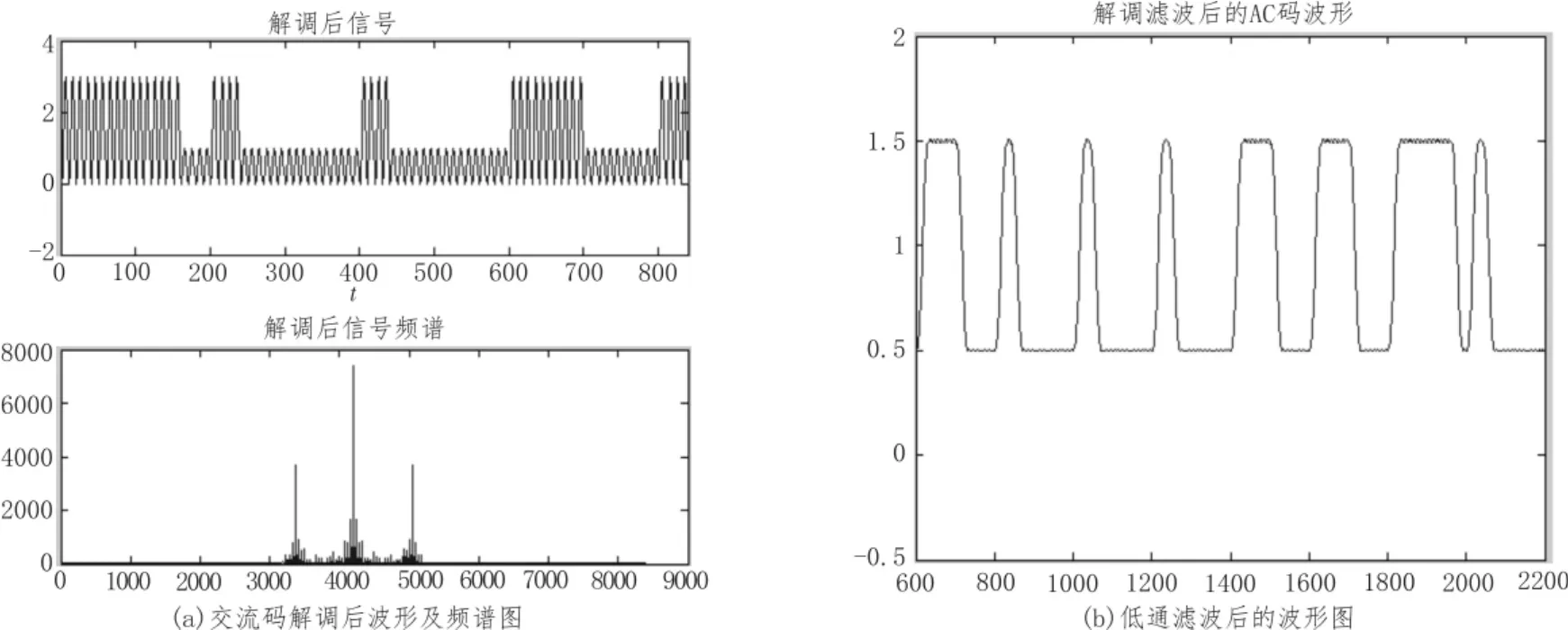

由上式可得,ω(t)信号由原来的调制信号 x(t)和频率被搬移到±2ω0附近的信号组成。因此通过低通滤波器滤除频率为±2ω0的部分,保留原来调制前的信号频谱[13]。图6(a)为交流码信号与正弦波相乘后的波形及其频谱图。正负2 kHz处的频谱分量幅度为中心频率的一半,与理论结果一致。图6(b)为通过64阶、截止频率为1 kHz的低通滤波器[14-15]后的波形。在2 ms脉冲处出现尖峰状,通过合理设置幅值门限,然后对高于门限的时刻计数,从而判断脉冲宽度,得到码元信息。

图6 交流码解调及滤波图

4 结束语

文章介绍了一种基于IRIG-B码测控设备时间系统的设计方案。论文采用容错技术来判定码元宽度,并对B码传输过程中可能出现的毛刺进行了容错设计,保证时间系统具有更好的抗干扰能力。该测控设备时间系统方案可根据不同的应用进行扩展,进一步增强了系统在其他领域应用的灵活性。

[1]江涛,孙昕.GPS与IRIG-B在电网授时系统中的应用[J].继电器,2007,35:333-335.

[2]周国平,邢灿华.IRIG-B格式时间编码电路的设计[J].电气技术与自动化,2005,34(2):88-90.

[3]史玉琴.基于EPLD的IRIG-B编/解码器的分析与设计明[J].现代电子技术,2007,14:79-81.

[4]CILETTI M D.Advanced digital design with theVerilogHDL[M].Publishing House of Electronics Industry,2005.

[5]张斌,张东来,王超.基于FPGA的IRIG-B(DC)码同步解码设计[J].测控技术,2008,27(2):45-47

[6]陈源,刘明波,侯孝民.基于IRIG-码的软件化测控系统时间同步方法研究[J].遥测遥控,2012,33(2):53-57.

[7]平步青.基于FPGA的I R IG—B编解码系统设计与实现[D].苏州:苏州大学,2012.

[8]冯培伦,邢晓楠,赵建文.基于FPGA的IRIG-B码(DC码)解码器设计[J].火力与指挥控制,2014,39:184-185.

[9]吴炜,周烨,黄子强.FPGA实现IRIG-B(DC)码编码和解码的设计 [J].电子设计工程,2010(12):162-164.

[10]郗海燕,王娟.基于FPGA的IRIG-B(DC)解码设计[J].电子设计工程, 2014,2(3):182-184.

[11]陈利.基于FPGA的IRIG-B码基带产生电路的设计与实现[D].苏州:苏州大学,2014.

[12]张明迪.基于FPGA的IRIG-B码解码设计[D].哈尔滨:哈尔滨工程大学,2011.

[13]乐正友.信号与系统[M].北京:清华大学出版社,2004.

[14]刘庆良,卢荣军,李建清.FIR数字滤波器的FPGA实现研究[J].电子设计工程,2010,18(3):59-62.

[15]杜勇,路建工,李元洲.数字滤波器的MATLAB与FPGA实现[M].北京:电子工业出版社,2012.

Design of measurement and control time system based on IRIG-B

JIA Zhen-hua1,XU Xiao-dong1,LV De-dong1,2, ZHANG Ge1,2,ZHU Xiao-hui1,2

(1.China Academy of Space Technology Institute of Telecommunication Satellite, Beijing, 100094,China;2.The Satellite Mobile Broadband Communication Engineering Technology Research Center of Beijing, Beijing 100094,China)

Time System plays very important role in formal function and trouble checking of measurement and control device.IRIG-B is the current synchronization time code in international shooting range.The paper designs the time system of measurement and control device based on IRIG-B,and has realized the time synchronization.It can fully satisfy most measurement and control system requirement.Compared with other methods before, it improves in decode scheme, which makes the design easy to realize.Local time system can ensure the equipment acquire correct time information,and provide time orientation for data processing,storage and analysis afterwards.

IRIG-B;time system;VHDL;shift-register;decode

TN764

A

1674-6236(2017)12-0077-04

2016-05-28稿件编号:201605272

贾振华(1991—),女,山西大同人,硕士研究生。研究方向:航天器电子与信息系统。