基于FPGA的AES算法硬件实现优化及IP核应用

2017-07-12龚向东

龚向东,王 佳,张 准,王 坤

(1.深圳大学 电子科学与技术学院,广东 深圳518060;2.深圳大学 光电工程学院,广东 深圳518060)

基于FPGA的AES算法硬件实现优化及IP核应用

龚向东1,王 佳2,张 准2,王 坤2

(1.深圳大学 电子科学与技术学院,广东 深圳518060;2.深圳大学 光电工程学院,广东 深圳518060)

根据AES算法的特点,从3方面对算法硬件实现进行改进:列混合部分使用查找表代替矩阵变换,降低算法实现的运算复杂度,采用流水线结构优化关键路径-密钥拓展,提升加密速度,利用FPGA定制RAM (BRAM)预存查找表进一步提升加密速度。优化后的AES算法在Virtex-6 xc6vlx240T(速度等级 -3)FPGA上实现,结果发现,AES算法共占用1 139个Slice,最大频率达到443.99 MHz,通量达到 56.83 Gbit/s,效率达到 49.89 (Mbit/s)/Slice;然后,对 AES算法进行接口逻辑声明,将优化后AES算法封装成自定制IP核;最后,采用基于NIOS II的SOPC技术,构建了一个嵌入式AES算法加密系统,实现了数据通信中的高速加密。

AES;流水线结构;通量;效率;自定制IP核;加密系统

数据加密标准(DES-Data Encryption Standard)[1]是密码学历史上第一个广泛用于商用数据保密的密码算法,随着计算机性能的不断提升,DES的密钥长度和分组长度显得过短,易被穷举攻破。为了更好的保护数据,2001年更安全的数据加密标准 (AESAdvancedEncryptionStandard高级加密标准)正式公布。

AES[2]算法的分组长度为128 bit,密钥长度支持128、192和256 bit。不同的密钥长度对应不同的加密轮数,分别为10,12,14轮。如密钥长度为128位的AES算法需要10轮迭代实现,前9轮迭代过程是一致的,包括字节替换、行移位、列混合、轮密钥异或,最后一轮包括字节替换、行移位和轮密钥异或,解密过程则是逆向轮迭代运算。AES算法可以通过硬件或软件的方法有效的实现。软件实现消耗较少的资源,获得有限物理安全保障和慢的加密速度;硬件实现则消耗更多的资源,获得极大的物理安全和很快的加密速度(达到Gbit/s)。

近些年网络和通信的快速发展,对通信速度和信息安全的要求越来越高,为了保证用户传输的信息在网络或通信中不被盗取和篡改,用户对信息进行加密后传输,这样就要求更高的加密速度。因此,硬件电路实现的加密算法受到更加广泛的关注。基于FPGA的加密算法具有安全性高、加密速度较快、开发周期短、可重配、成本低、可靠性高以及可移植性好等特点[3-4],在加密中得到广泛应用。

基于FPGA的AES算法实现的研究中,部分研究侧重AES算法加密速度的优化,并不关心其逻辑资源消耗:文献[5]为了提高算法加密速度,使用了多核128-AES技术,一次处理多个128 bit数据,以达到提升加密速度的目的,这种硬件实现方式以牺牲大量可编程逻辑资源为代价。文献[6]使用CTR模型来实现AES,加密速度很快,但可编程逻辑资源消耗非常大。另一部分研究虽然使用了较少的可编程逻辑资源,但其实现速度较慢:文献[7]仅仅使用了轮内流水线结构来提升加密速度,资源消耗较少,但每10个时钟周期输出一个加密结果,加密速度很低。文献[8]为了减少可编程逻辑资源的消耗,对S盒进行了优化,设计的S盒在有限域GF(24)2上取乘法逆,原S盒的仿射函数不变,并且与AES算法S盒的仿射函数相复合生成新的S盒,并未在其他方面优化,其整体加密速度较慢。

设计并实现一种基于FPGA的AES加密算法,以较少的逻辑资源消耗获得快的加密速度。从降低算法运算复杂度,优化关键路径提高加密速度(通量),利用BRAM进一步提升加密速度等方面对算法的硬件实现进行优化,以获得更高的加密速度和效率。优化后的AES算法封装成IP核,并在SOPC上使用自定制IP核,实现数据通信中的高速加密。

1 AES算法的硬件实现优化

1.1 行移位与列混合的优化降低资源使用

明文分成16个字节,组成状态矩阵[2]A。AES算法轮迭代包括4个部分:字节替代,行移位,列混合,轮密钥异或。字节替代使用查找表(S盒)实现,替代后的输出矩阵B行移位。为减少逻辑资源的使用,行移位与字节替代组合实现,矩阵A进行字节替代后输出结果不再按照原始顺序,而按行移位后的顺序,节省行移位所需可编程逻辑资源。

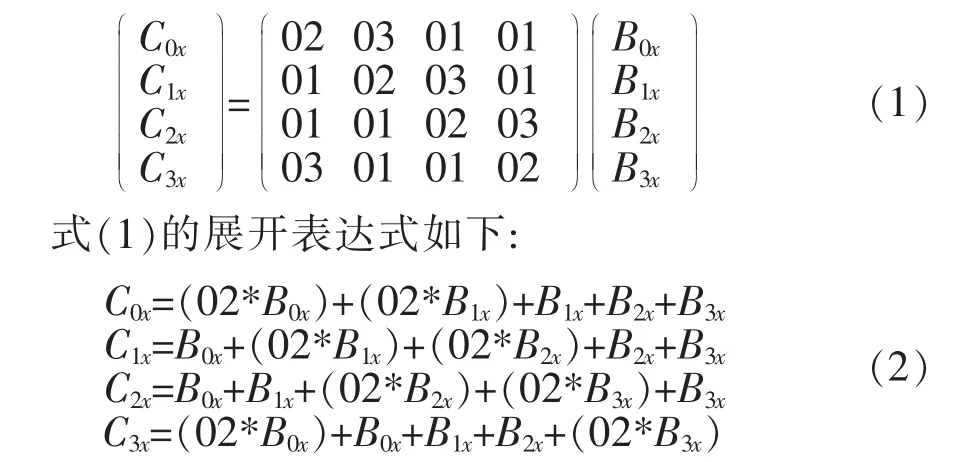

列混合运算如式(1)所示,其中Bij是状态矩阵B的元素,下标x=0、1、2、3表示状态矩阵的不同列。

上述运算都在有限域GF(28)域[1]上进行的,硬件实现时,加法运算等价于异或;*运算则分为两种情况[2]:如果二进制数Bij最高位为1,与2做*运算时,则先左移一位,然后与00011011进行异或运算;如果二进制数Bij最高位为0,与2做*运算时,则只左移一位。用查找表方式替代组合逻辑实现的*运算,将8位二进制数进行*运算的256种可能结果用一个查找替换表(M盒)进行存储,输入的8位二进制数为M盒的元素地址,取出对应地址的M盒元素,可以降低列混合的运算复杂度,减少可编程逻辑资源消耗。

1.2 关键路径(密钥扩展)的优化提升加密速度

AES系统的通量和效率定义如下:

通量=分组长度×最大频率/所需时钟周期数 (3)

效率=通量/所用可编程逻辑单元(Slice)个数(4)

标准AES经过10轮迭代,即每10个时钟周期获得一个加密结果[10],通量低。一般会将10轮迭代完全展开并在每一级加入流水线,每一个时钟周期获得一个加密输出,加密速度提升为原来的十倍。

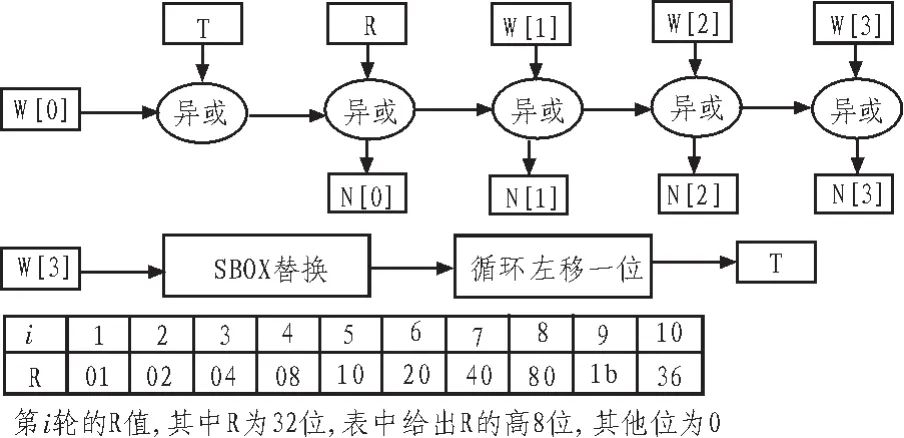

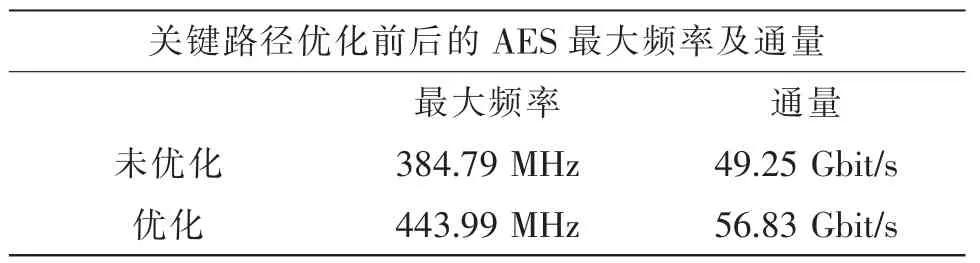

为了进一步提高AES算法通量,需找出关键路径,对轮迭代中的每一个变换进行测试并获得其最大频率,将字节替换,行移位,列混合组合实现,得到最大频率1 205.13 MHz;对密钥拓展部分实现,获得最大频率为384.79 MHz。在AES算法的轮迭代中,密钥拓展部分与另外3部分相对独立。AES算法最大频率由密钥拓展和轮迭代的另外3部分组合实现的最大频率中的较小者决定。而字节替换,行移位,列混合的组合实现的最大频率远高于密钥拓展部分的最大频率384.79 MHz,得出决定AES算法最大频率的关键路径是密钥扩展部分。

密钥扩展部分为AES的关键路径,如图1所示密钥扩展流程图,W为第i轮128位密钥,N为第i+1 轮 128 位密钥,W[i]、N[i](i=0,1,2,3)分别为 W 和N的32位分组,T、R为32位。

图1 密钥扩展流程图

为了进一步提高AES算法的通量,需提高密钥扩展部分的最大频率。引入6级流水线结构,每次异或运算之后均加入寄存器,这样一个时钟周期之间的组合逻辑运算只有一次异或运算,与其他情况下的一个时钟周期内多次异或运算相比较,最大延迟降低,最高频率提高。插入流水线后单独的密钥扩展部分最大频率提高到515.38 MHz。

1.3 利用BRAM进一步提升加密速度

FPGA内嵌RAM(BRAM)的读写操作具有延迟固定,低延时和访问时间固定的优点。利用BRAM代替LUT实现S盒和M盒可以进一步提高算法的加密速度(通量)。

AES算法在FPGA上实现的最大频率为443.99 MHz,消耗1 139个Slice,通量为56.83 Gbit/s,效率为49.89(Mbit/s)/slice。表1为关键路径优化前后的对比。

表1 关键路径优化前后的对比

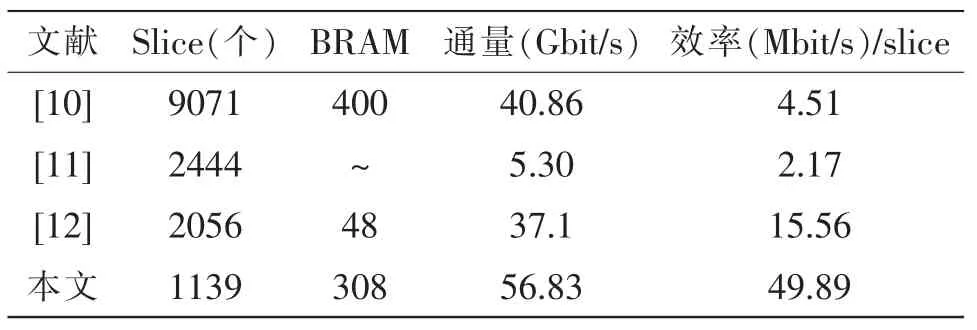

表2为本设计结果与相关文献(文献均在Virtex 6实现AES算法)所报道的同类设计结果的比较。

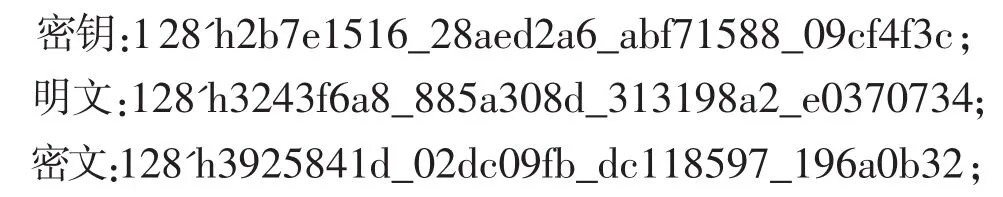

本设计效率最高,为了验证优化后加密算法的功能正确性,选取测试向量[13],其相关数据如下:

采用Modelsim进行功能时序仿真验证,结果显示优化后算法实现了预定功能。

表2 本设计与同类设计的比较结果

2 AES算法自定制IP核

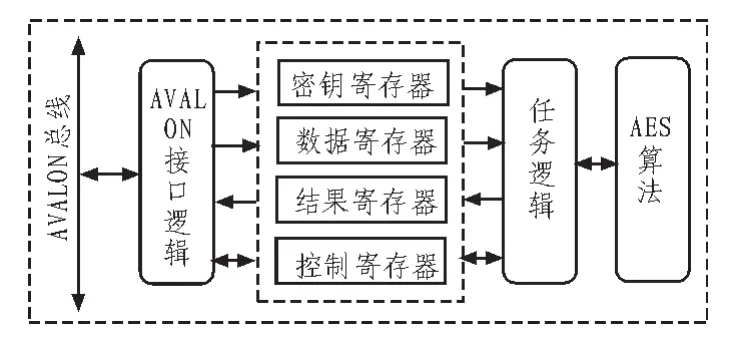

优化后的AES算法封装为自定制IP核,需要对接口进行声明。自定制IP核硬件结构[14]如图2所示,主要由AVALON接口逻辑部分,寄存器逻辑部分,任务逻辑部分和AES算法部分构成。

图2 AES算法IP核硬件结构

4个模块中,AVALON接口逻辑模块声明与总线通信的接口,调用寄存器逻辑模块和任务逻辑模块。寄存器逻辑模块定义工作寄存器组,因为NIOS CPU是32位RISC软核处理器,所以AVALON总线定为32位,设置的寄存器字长也为32位,包括4个32位的密钥寄存器,4个32位的明文数据输入寄存器,4个32位的结果寄存器和1个32位控制寄存器。为寄存器设定地址偏移量,密钥寄存器地址偏移量为0x00~0x03,数据寄存器地址偏移量为0x04~0x07,结果寄存器地址偏移量为0x08~0x0b,控制寄存器地址偏移量为0x0c。控制寄存器用于控制AES算法,其格式如下:控制寄存器第0位为AES算法状态位,用于判断AES算法完成与否(完成则为1);寄存器第1位为AES算法启动位,当启动位为1时,AES算法启动;寄存器第2位为加解密选择位,选择位为1,则AES进行加密,为0,则进行解密;寄存器第3位则为状态复位位,复位位为1时,状态机复位,进入休眠初始态,其余为保留位。

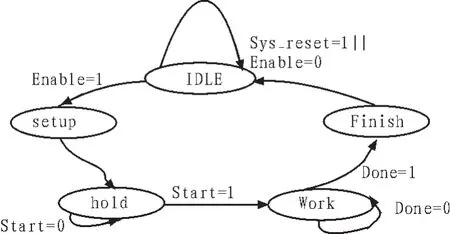

任务逻辑模块用于状态转换,即状态机的描述:状态机复位后进入初始休眠态Idel,密钥和明文输入后,发送使能信号Enable,状态机转入建立态Setup,将明文和密钥送入AES算法部分,之后状态机自动跳入保持态Hold(加入保持态是为了确保明文和密钥完全送入AES算法部分),等待AES算法启动信号,像控制寄存器写入启动信号Start,状态机进入工作态Work,AES算法开始工作,加/解密完成后,AES算法发出完成标志信号,状态机进入完成态Finish,最后自动跳入休眠态Idel,如图3所示。

图3 任务逻辑状态转换图

3 AES算法加密系统

基于NIOS II的可编程片上系统(SOPC),其硬件和软件均可现场编程实现,从而为设计提供了极大的灵活性,并得到了越来越广泛的应用[15-16]。

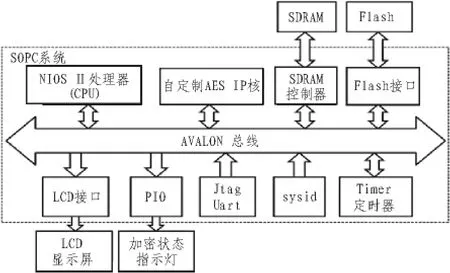

AES算法加密系统的SOPC结构如图4所示,其中包括NIOS II处理器,自定制AES IP核,SDRAM控制器,FLASH接口等。AES IP核用于数据加密,SDRAM用于数据的存储,FLSAH用于系统程序的运行,PIO用于显示加密完成的标志,LCD用于显示加密结果。

图4 AES算法加密系统

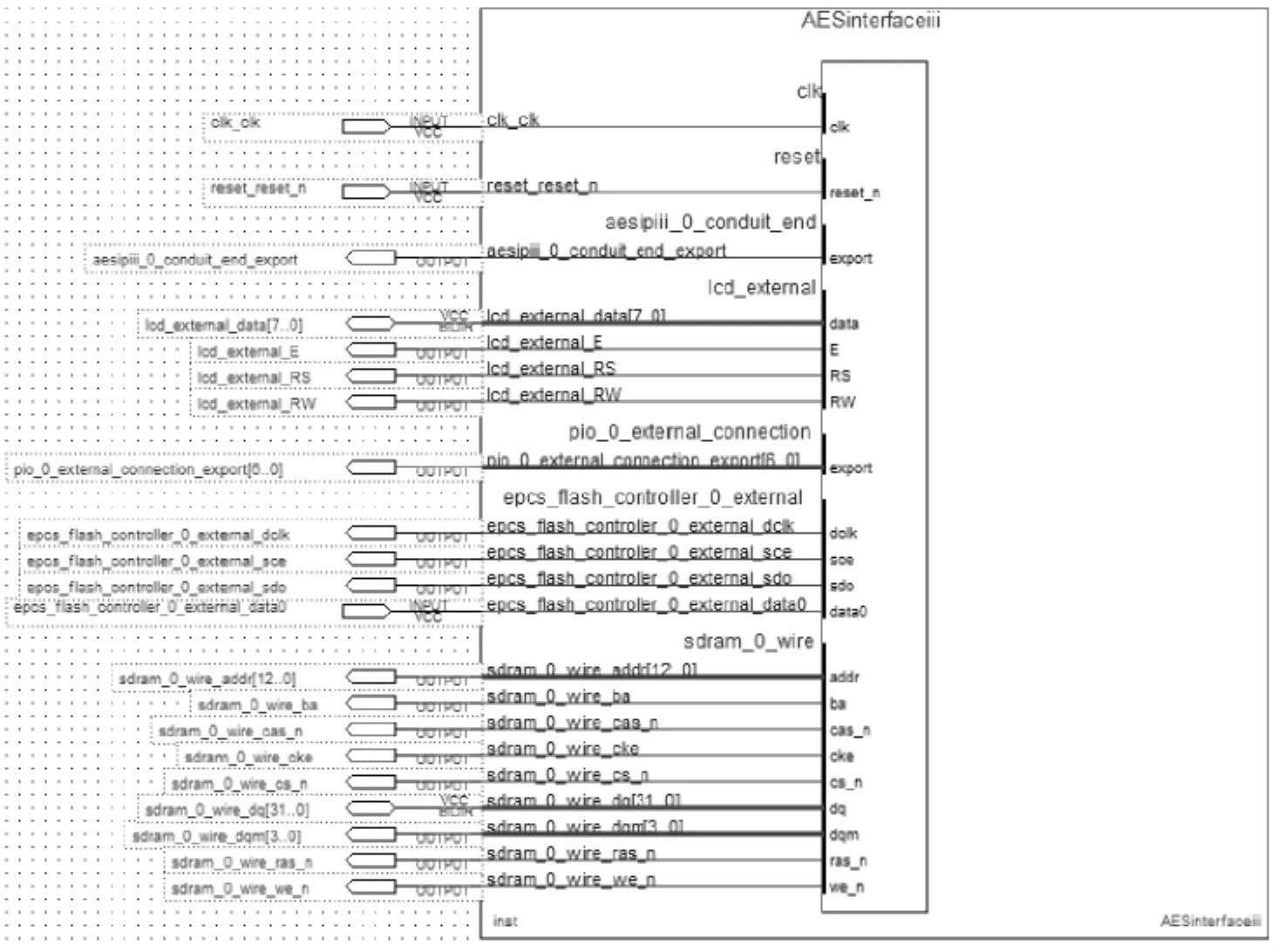

SOPC系统采用Altera QuartusII设计软件中的Qsys工具构建。Qsys的系统组件库提供了CPU,FLASH存储器接口,SDRAM控制器等IP核,AES加密则采用自定制设计IP核。AES加密系统的QuartusII工程顶层模块如图5所示。

图5 AES加密系统的QuartusII工程顶层模块

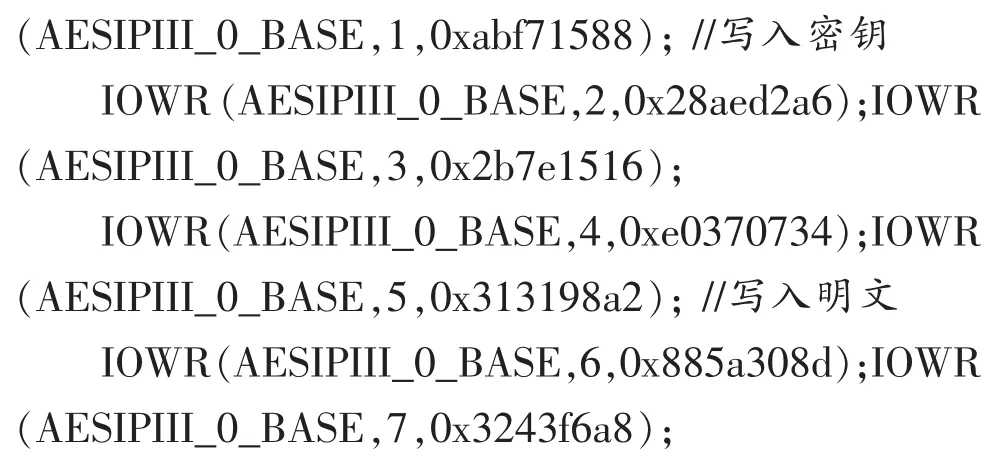

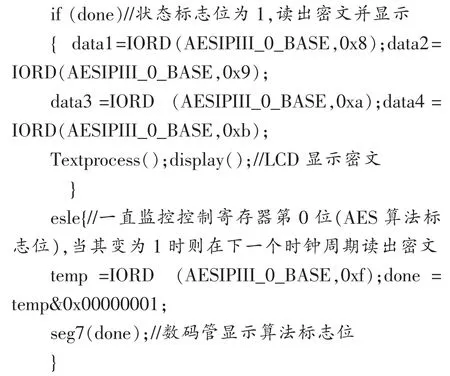

用户应用程序通过硬件抽象层(HAL)系统访问硬件,作为软件运行环境的HAL系统将C标准库,应用程序接口(API)和设备驱动程序集成在一起。当采用Qsys创建了NIOS II应用硬件系统后,就可以在NIOS II集成开发环境(EDS)中创建相应的HAL系统库,并进行IP核应用编程。使用API函数IOWR(AESIP_BASE,OFFSET,DATA)将与上文验证的128 位测试密钥2b7e1516_28aed2a6_abf71588_09cf4f3c和128位明文3243f6a8_885a308d_313198a2_e0370734分别写入密钥寄存器,数据寄存器,程序如下。

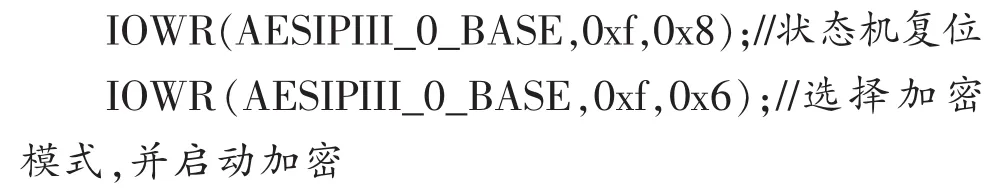

再将启动加密的控制字写入控制寄存器,AES IP核开始工作,程序如下:

加密完成后返回的加密完成信号触发结果读出及完成标志信号显示。

4 结束语

文中首先介绍了基于FPGA的AES算法硬件实现优化,从行移位,列混合和关键路径等进行硬件实现优化,获得了AES算法加密速度56.83 Gbit/s,加密效率 49.89(Mbit/s)/Slice,与同类设计相比,加密速度较快,加密效率最高;然后,优化后的AES算法进行接口逻辑声明,封装成自定制IP核,以便随时添加使用;最后,采用基于NIOS II的SOPC技术,构建了一个嵌入式AES算法加密系统,实现了数据的高速加密,该系统具有开发周期短,处理速度快,硬件可自由配置等优点,可以自由的应用于高速数据通信中。

[1]谷利泽,郑世慧,杨义先.现代密码学教程[M].2版.北京:北京邮电大学出版社,2015.

[2]刘艳萍,李秋慧.AES算法的研究与其密钥扩展算法的改进[J].现代电子技术,2016,39(10):5-8.

[3]韩津生,林家骏,周文锦,等.基于FPGA的AES核设计[J].计算机工程与科学,2013,35(3):80-84.

[4]韩少男,李晓江.一种小面积低功耗串行AES硬件加解密电路[J].微电子学, 2010,40(3):347-353.

[5]Henzen L,Fichtner W.FPGA parallel-pipelined AES-GCM core for 100G Ethernet applications[R].ESSCIRC, 2010 Proceedings of the, Seville,2010:202-205.

[6]Abolfazl Soltani,Saeed Sharifian.An ultra-high throughput and fully pipelined implementation of AES algorithm on FPGA[J].Microprocessors and Microsystems, 2015(39):480-493.

[7]El Maraghy M,Hesham S,Abd El Ghany M A.Real-time efficient FPGA implementation of aes algorithm[C]//SOC Conference(SOCC),2013 IEEE 26th International, Erlangen, 2013:203-208.

[8]武一,郭婷婷.基于FPGA的加密算法改进及实现[J].电视技术,2014,38(5):66-70.

[9]杨军,余江,赵征鹏.基于FPGA密码技术的设计与应用[M].北京:电子工业出版社,2012.

[10]Wang Y,Ha Y.FPGA-Based 40.9-Gbits/s Masked AES With Area Optimization for Storage Area Network[R].in IEEE Transactions on Circuits and Systems II, 2013:36-40.

[11]Hussain U,Jamal H.An efficient high throughput FPGA implementation of AES for Multi-gigabit Protocols[C]//Frontiers of Information Technology(FIT), 2012 10th International Conference on,Islamabad, 2012:215-218.

[12]Rahimunnisa K, Karthigaikumar P, Rasheed S,et al.Suresh Kumar,Fpga implementation of aes algorithm for high throughput using folded parallel architecture[J].Security Commun.Netw.(2014),7(11):2225-2236.

[13]谷大武,徐胜波译.高级加密标准(AES)算法-Rijndael的设计[M].北京:清华大学出版社,2003.

[14]龚向东,黄虹宾,刘春平.主从可配置I2C总线接口IP及其应用[J].电讯技术,2010,50(1):76-80.

[15]宋宇,宋隽炜.基于SOPC的微型无人机飞行控制系统设计[J].传感器与微系统,2016,35(9):101-103.

[16]张磊,武腾飞,申雅峰.基于SOPC的光信号数据采集解调系统设计 [J].光学技术,2016,42(4):321-324.

Optimization of AES algorithm hardware implementation based on FPGA and application of its IP core

GONG Xiang-dong1,WANG Jia2,ZHANG Zhun2,WANG Kun2

(1.College of Electronic Science and Technology , Shenzhen University,Shenzhen 518060,China;2.College of Optoelectronic Engineering,Shenzhen University,Shenzhen 518060,China)

According to the characteristics of AES algorithm,its hardware implementation is improved from three aspects in this paper:In parts of sub_Bytes and MixColumns,using lookup table replace matrix transform to reduce the computational complexity of AES algorithm implementation;Using pipeline architecture for optimization of critical path greatly increase encryption speed;Employing FPGA customized RAM (BRAM)store pre-computed lookup table value to further enhance the encryption speed.The optimized AES algorithm is simulated and verified,then it is implemented on a Xilinx Virtex-6 xc6vlx240T (speed grade-3) FPGA.Improved results are obtained:1 139 Slices is totally employed, maximum frequency is 443.99 MHz, throughput is 56.83 Gbit/s,and efficiency is 49.89(Mbit/s)/Slice; Then, declaring Interface logic for AES algorithm, the optimized AES algorithm is encapsulated into a custom IP core;At last,using SOPC technology to build an embedded AES algorithm encryption system based on NIOS II,the system implement high speed data encryption in data communication.

AES;pipelinearchitecture;maximumfrequency;efficiency;customIPcore;encryptionsystem

TN918

A

1674-6236(2017)12-0001-05

2016-10-08稿件编号:201610011

国家自然科学基金仪器专项(61027014)

龚向东(1956—),男,广东深圳人,教授。研究方向:瞬态光电技术,微机系统应用等。