基于FPGA的非接触电导检测FIR数字滤波器设计与研究

2017-06-21周彬彬袁海林廖红华

付 豪,周彬彬,吕 义,袁海林,廖红华

(湖北民族学院 信息工程学院,湖北 恩施 445000)

基于FPGA的非接触电导检测FIR数字滤波器设计与研究

付 豪,周彬彬,吕 义,袁海林,廖红华*

(湖北民族学院 信息工程学院,湖北 恩施 445000)

为解决非接触电导检测系统易受噪声干扰的问题,介绍了一种基于FPGA的FIR数字滤波器解决方案.应用Matlab中的Simulink对非接触电导检测模型建模并产生信号,通过DSP Builder搭建的FIR数字滤波器对信号的高频噪声进行滤波处理,最后用FPGA仿真相应功能.仿真结果表明:FIR数字滤波器可以较好的滤除电导检测中的高频噪声,系统处理速度快,运行稳定可靠,适合于非接触电导检测.

非接触电导检测;FIR数字滤波器;DSP Builder

非接触电导检测是近些年发展起来的一种新型的检测技术,特别是该检测技术应用在电泳芯片上,具有快速、高效且需要样品溶液少等优点.由于芯片的沟道较短,导致检测信号带有少量的随机、周期性激励信号干扰[1-2].为提高检测信号的灵敏度,本系统提出了一种基于FPGA的FIR数字滤波器,对检测信号进行滤波处理.本文提出的数字滤波器为低通滤波器,可以有效的滤除高频杂波,并且该滤波器具有稳定性高、成本较低、实时性强等优点,非常利于非接触电导检测的滤波处理.

1 非接触电导检测的建模与噪声分析

非接触电导检测模型为4电极电容耦合非接触电导检测模型[3-4].在非接触电导检测等效模型中,电容C1、C2、C3和C4为每两个电极之间的寄生电容,且每个电容都是并联关系.R0为恒流源的等效电阻,电阻R1、R2和R3分别为电极之间的等效电阻.在外测电极两端施加一个恒流源提供激励电流,内侧的两个电极产生检测信号V0.建立的非接触电导检测等效电路模型如图1(a)所示.由上述原理可知,噪声的主要来源检测电解液时产生信号自带的高频噪声,为了提高测试的精确性,必须减少测试产生的高频噪声.通过Matlab搭建模块并产生波形信号.非接触电导检测信号如下图1(b)所示.

消除信号噪声主要采取以下两种方法:

1)设计方法改进降噪.这种降噪方法需要对设计方法和硬件电路进行改进,但这种方法需要提高硬件成本,且理论上也很难实现.

图1 非接触电导检测模型Fig.1 Mode of contactless conductivity detection

2)设计滤波器的方式降噪.该方式成本低、实现方便,可控性较强.

结合两种方式的优缺点,本系统设计采用第二种方式的设计滤波器的方式降噪,不仅有成本低、实现方便,而且可以对滤除的噪声可调、可控的好处.

2 FIR数字滤波器基本原理

在实际的工程应用中,非接触电导检测为模拟信号,需要将电导检测电信号通过A/D转换为数字信号才能进行滤波处理.数字滤波器不仅有成本低、实现方便,

图2 FIR滤波器基本结构Fig.2 Basic Structure of FIR filter

而且可以对滤除的噪声可调、可控的好处.

3 基于AlteraDSP Builder的FIR滤波器的设计

DSP Builder为Altera可编程逻辑器件(PLD)中的DSP系统设计需要的高级算法和HDL开发工具[10-11].Altera DSP Builder可以很好的将Matlab和Simulink系统相结合,其中的算法搭建、仿真和验证可以在Matlab中独立完成,之后再与FPGA的仿真、编译综合融合在一起,且在设计实现较简单,免去了较为繁琐的软件编程.

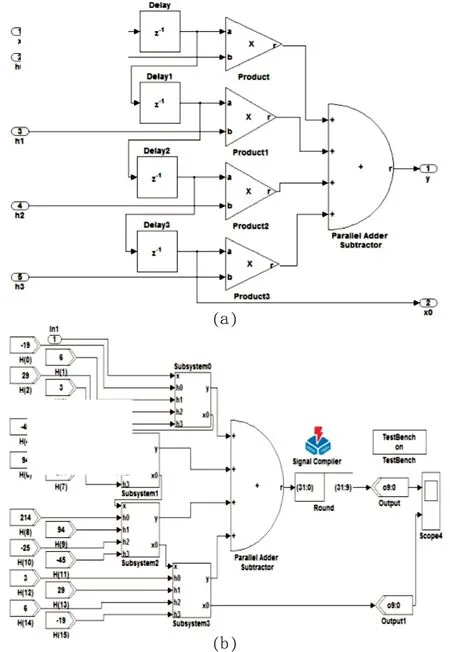

图3 基于AlteraDSP Builder的数字滤波器结构图Fig.3 Structure diagram of digital filter based on Altera DSP Builder

3.1 数字滤波器的参数设计

本系统需要设计一个16阶数字滤波器,主要设计方法如下:进去Matlab之后,点开Start选择其中的FDATool设计所需滤波器,接着进入Filter Design & Analysis Tool界面配置所需低通滤波器的参数:反应类型(Response Type)选择Lowpass、设计方法(Design Method)选择FIR&Window、滤波器阶数(Filter Order)定制为15、Fs为50KHz,Fc为10KHz.通过该滤波器的幅频特性曲线和相频特性曲线导出16阶滤波器的系数Num到Matlab的workspace中,再通过在主窗口中输入命令round(Num*(2^9)),则可以运用归一化在主窗口中得出滤波器的系数如下:

[H(0),H(1),…,H(15)] =[-19,6,29,3,-45,-25,94,214,214,94,-25,-45,3,29,6,-19]

3.2 FIR数字滤波器在DSP Builder中的设计

本系统需要设计一个16阶数字滤波器,则首先设计一个4阶的数字滤波器,如图3(a)所示,其中包括有DSP Builder模块中的AltBus接口总线、Delay延时单元、Product乘法器、Parallel Adder Subtractor加法器,再生成16阶数字滤波器所需的Subsystem子模块,通过模块级联的方式,组成16阶的数字滤波器,这种方法简单易操作,想提高滤波器的阶数只需复制子模块级联即可.16阶数字滤波器如图3(b)所示.

图4 FIR数字滤波器IP核模块Fig.4 IP core module of FIR digital filter

3.3 基于FPGA的功能实现

为了进一步实现相应功能,将Matlab中的模块转换为VHDL语言,进行仿真[12-13].首先在Altera DSP Builder工具箱中找到SignalCompilar模块和TestBench模块加到Simulink文件中,启动SignalCompilar模块生成为Quartus II工程,得FPGA平台搭建顶层原理图.FIR滤波器的IP核模块如图4所示.

4 仿真与验证

图5 FIR滤波器的Modelsim仿真结果Fig.5 Modelsim simulation results of FIR filter

本系统应用仿真环境为Modelsim,通过该环境对FIR滤波器进行仿真验证.仿真结果如图5所示.

通过图5的仿真结果图可以看出,所观测的信号都为自动无符号模拟信号,显示模式为波形信号.Input1为非接触电导检测信号,Output为经过滤波器滤波之后的输出信号.输出信号相对于输入信号有了一定的时间偏移,是因为滤波器延时器的原因,但不影响滤波效果.输入信号的干扰噪声得到了滤除,且很好地保持原信号的基本特征.

5 结论

本文介绍了非接触电导检测的基本原理,分析了噪声产生的不同原因,根据指标,通过DSP Builder搭建模型,再生成VHDL语言,通过Matlab+ModelSim进行仿真.结果表明:FIR数字滤波器可以很好地完成对非接触电导检测中的干扰噪声进行滤波,且很好地保持原信号的基本特征,对后面的工程提高非接触电导的微弱信号检测精度提供了强有力的支持.

[1] ZEMANN A J,SCHNELL E,VOLGGER D,et al.Contactless conductivity detection for capillary electrophoresis[J].Reference to a book: Analytical Chemistry,1998,70(3):563-567.

[2] 廖红华,吴长坤,廖宇,等.基于广义形态滤波的低电压芯片电泳电色谱信号去噪研究[J].湖北民族学院学报(自然科学版),2014,32(4):439-444.

[3] 唐俊妮,汤承.食源性病原微生物检测与控制技术研究新进展[J].西南民族大学学报(自然科学版),2016,42(2):139-150.

[4] 廖红华, 王骏, 周文利, 等. 基于SOPC的电泳芯片电导检测系统[J].仪表技术与传感器,2008(10): 66-71.

[5] 顾卫东, 卢新艳. FIR数字滤波在MEMS加速度计中的应用[J].MEMS器件与技术, 2009,46(12): 735-738.

[6] 田莎莎,喻成,汪红.用FPGA实现FIR数字滤波器的新方法[J].中南民族大学学报(自然科学版),2012,31(2):100-103.

[7] STOSIC B P,PAVLOVIC V D.On design of a novel class of selective CIC FIR filter functions with improved response[J].International Journal of Electronics and Communications,2014,68(8):720-729.

[8] 杨庆.基于VHDL与CPLD器件的FIR数字滤波器的设计[J].湖北民族学院学报(自然科学版),2005,23(1):66-68.

[9] 林志典,张方佩,袁国顺.基于FPGA的高速FIR滤波器的设计与实现[J].微电子学,2013,43(4):537-540.

[10] 李锦明,谢绪煜,马游春,等.基于FPGA的FIR滤波器系统的设计[J].化工自动化及仪表,2011(8):943-946.

[11] 白炳良.小功率单相电机的单片机变频调速系统研制[J].云南民族大学学报(自然科学版),2013,22(6):448-451.

[12] 张婧霞,沈三民,翟成瑞.基于FPGA乘法器的FIR滤波器系统设计[J].电视技术,2012,36(3):40-43.

[13] 杨鸿武,丁朋程,王全州.基于FPGA的高速全并行FIR滤波器的设计[J].西北师范大学学报(自然科学版),2012,48(1):48-51.

责任编辑:时 凌

Design of FIR Digital Filters for the Contactless Conductivity Detection Based on FPGA

FU Hao,ZHOU Binbin,LYU Yi,YUAN Hailin,LIAO Honghua*

(School of Information and Engineering,Hubei University for Nationalities,Enshi 445000,China)

To solve the noise problem of contactless conductivity detection system,we introduced a solution of FIR digital filter based on FPGA.Firstly,Simulink of Matlab is used to establish a model for the contactless conductivity detection and producing the signal.Secondly,the FIR digital filter built by DSP Builder filters out the high frequency noise of the signal.Finally,the corresponding function is simulated by using FPGA.The experimental results show that the FIR digital filter can greatly filter out the high frequency noise of the contactless conductivity detection.The system has the advantages of fast processing speed,high stability and reliability,which is suitable for the contactless conductivity detection.

contactless conductivity detection; FIR digital filter; DSP Builder

2017-03-21.

国家自然科学基金项目(61463014;61263030)

付豪(1993-),男,硕士生,主要从事电力电子与电力传动、嵌入式系统等的研究;*

廖红华(1972-), 男(土家族),博士,教授,主要从事电力电子与电力传动、嵌入式系统及微型全分析系统等的研究.

1008-8423(2017)02-0216-03

10.13501/j.cnki.42-1569/n.2017.06.024

TP311

A