基于EDA技术的流水线CPU创新设计

2017-05-24何芳成韩晓彤张珊时浩然周晓军

何芳成+韩晓彤+张珊+时浩然+周晓军

摘 要:基于EDA技术设计的一种五级流水线CPU,它将指令分解为取指令、指令译码、指令执行、访问存储器、数据写回五阶段流水处理。首先进行结构设计,然后解决流水线CPU的各项相关问题,再进行各模块设计。最后基于CycloneⅢ系列FPGA硬件平台和QuartusⅡ工具开发平台,利用EP3C40Q240C8型FPGA芯片进行设计与调试。

关键词:EDA;流水线;CPU

引言

CPU是由基本的功能模块和与之相连的数据通路组成,对于CPU的设计,首先必须了解其结构的细节和功能模块的内容。然后对各模块电路进行编辑设计、逻辑综合、时序仿真和硬件设计,最后组装完成整个硬件系统。在这个过程中还包括指令系统的设计和软件程序调试等步骤。在流水线CPU设计过程中重点解决结构冲突、数据冲突、控制冲突三大问题。

1 流水线CPU工作原理

1.1 流水线原理

对于一条具体的指令执行过程,通常可以分成五个部分:取指令,指令译码,取操作数,运算,写结果。其中前面三个步骤一般由指令控制器完成,后面两步则由运算器完成。指令控制器完成了对第一条指令的处理后,不等待运算器完成后续的处理直接开始对第二条指令的处理。

1.2 CPU的结构与功能

CPU是负责执行指令的,图1为一个简单指令的CPU结构图。

对于冯·诺依曼结构的计算机来说,一旦程序进入存储器后,就可由计算机自动完成取指令和执行指令的任务,控制器就是专门用于完成此项工作的,它负责协调并控制计算机各个部件执行程序的指令序列,其基本功能是取指令,分析指令和执行指令。

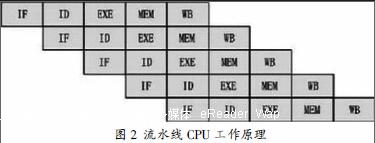

1.3 流水线CPU工作原理

流水线是一个可以提高CPU运行效率的技术,它的核心思想是把多條指令的不同执行阶段重叠,让CPU同时处理多条指令。在流水线CPU中,每条指令的执行过程被分成多个执行阶段。只有当某指令的执行阶段都完成后,该指令才算执行完毕。在每一个指令执行阶段中,当一条指令在该阶段中完成执行后,下一条指令将立即进入到该执行阶段来执行。当流水线处于饱和状态时,将同时有流水线级数的指令在同时运行。如图2所示。

1.4 指令集

指令集是指CPU指令系统所能识别执行的全部指令的集合。处理器要完成计算任务,需要具备运算、控制、传送等指令。运算指令是由运算器单元(ALU)实现,包括算术运算指令、逻辑指令和位移指令。控制指令是由除了做运算外的其他操作指令,如循环、跳转、CPU控制等指令构成,由CPU控制器单元实现。数据传送指令是完成数据传送的任务,如寄存器、存储器交换数据及自身交换数据的指令等。

2 流水线CPU创新设计

2.1 流水线工作的五个阶段

取指令阶段(IF),从指令存储器中获取指令存入IR寄存器,并更新PC寄存器的值。该阶段完成计算下一条指令的地址(+1)以及取指操作,加法器完成加1操作,Lpm_Instrom完成取指操作。指令译码阶段(ID),由IR寄存器中的指令的op和func字段译码出各个阶段需要的控制信号,同时从寄存器组RegSet中获取EXE阶段所需要的操作数并将指令的立即数进行扩展。指令执行阶段(EXE),根据操作数计算出结果,算数运算由ALU完成,移位运算由移位器完成,通过控制信号Resultop选择执行结果。访问存储器阶段(MEM),把EXE阶段计算的结果作为数据存储器的地址输入端读取数据,若数据存储器写使能信号DMwen为高电平,那么需要把rt寄存器的数据写入数据存储器的对应存储单元。数据写回阶段(WB),选择写回寄存器组RegSet的数据,根据前面的流水段传递的控制信号REwen和目的寄存器RegDest将数据写回。

在每一个阶段完成一条指令在该阶段的执行任务之后,将进下一条指令的执行。这样,每两个阶段之间都需要有一组寄存器来保存刚刚执行完成的指令的执行结果。该执行结果将交给下一个执行阶段,进行下一个阶段的处理任务。

2.2 流水线CPU顶层设计

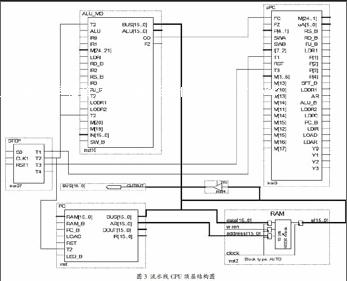

CPU主要由以ALU为核心的运算器模块、以程序计数器PC和地址寄存器AR为核心的数据通路模块、以微指令控制器为核心的控制器模块、以程序控制器和数据RAM为核心的存储模块四个模块构成。

算数逻辑单元模块主要有ALU运算器,数据寄存器DR等部件,ALU运算器是CPU的核心,它可以执行算数运算,也可以执行逻辑运算。数据缓冲寄存器DR为ALU提供一个或两个参与运算的操作数,同时作为CPU、外部设备、主存之间的信息中转站,对数据起暂存作用。数据通路模块主要由程序计数器PC,地址寄存器AR,指令寄存器IR组成。程序计数器PC的功能是给出在主存中的下一条指令的地址。PC值的变化分为两种情况,一是指令顺序执行的情况,二是跳转指令的情况。地址寄存器AR用来保存当前CPU所要访问的主存单元或I/O端口的地址。指令寄存器IR用来保存当前CPU正在执行的一条指令。微程序控制器主要由控制存储器、微指令寄存器和微指令地址形成部件三部分组成。控制存储器用以存放指令系统所对应的全部微程序。微程序控制器主要由微指令控制电路、微地址寄存器和微指令存储器三个模块组成。微地址分支转移控制电路根据来自指令寄存器IR的指令操作码生成一个微地址的控制信号,控制微程序按正确顺序执行微程序和实现分支转移。微地址寄存器是用来存放从微指令存储器中读出的一条微指令信息,由控制字段和下地址字段组成。微指令存储器是存取微程序的原件,其原件的生成可直接调用LPM宏模块。组成的流水线CPU顶层结构图如图3所示。

3 结束语

流水线CPU是现代CPU非常流行的设计方式,它在只需要添加少数硬件的条件下大大提高了CPU的性能。本设计从了解并研究CPU工作原理开始,到熟悉并运用EDA技术,再到流水线CPU局部器件设计、模块设计、整体设计,最后在FPGA硬件平台和QuartusⅡ工具开发平台进行模拟调试验证了本设计符合设计要求。但本设计的CPU与实际应用中的CPU还存在较大的差距,在接下来的研究中小组成员仍将不断丰富流水线CPU的知识,将本设计的流水线CPU升级至应用级别。

参考文献

[1]史展,李占宣.基于FPGA的嵌入式CPU的VHDL设计[J].科技创新与应用,2013(9).

[2]潘松,黄继业.EDA技术与VHDL[M].北京:清华大学出版社,2013(4).

[3]潘松,潘明,黄继业.现代计算机组成原理[M].北京:科学出版社,2013.