基于FPGA的DCM设计研究

2017-05-18江苏金陵机械制造总厂徐立升张建春

江苏金陵机械制造总厂 徐立升 张建春

基于FPGA的DCM设计研究

江苏金陵机械制造总厂 徐立升 张建春

Xilinx公司的FPGA中的数字时钟管理单元(DCM),具有强大的时钟管理作用。本文介绍了FPGA中的DCM的原理与应用,对其工作原理、组成、使用方法及应用进行了系统描述,通过对DCM IP核的参数设置和程序设计实现了时钟的倍频、分频和相位移动等功能。

FPGA;DCM;IP核

1 引言

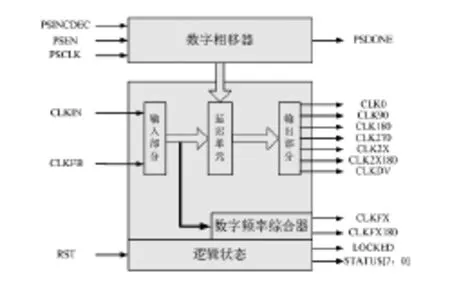

随着集成电路的发展,芯片的集成度越来越高,实现的功能越来越多。可编程逻辑器件FPGA是一种可在线编程的逻辑芯片,具有强大的实时处理与运算能力,在通信与图像处理中的应用越来越多。为了适应各种需要,FPGA内部集成了数字时钟管理单元DCM,DCM提供了强大的时钟管理功能:时钟去偏斜,频率综合,时钟相移,动态重配置等功能。DCM内部结构图如图1所示。

图1 DCM内部结构图

2 DCM组成

DCM是Xilinx公司专有的时钟管理模块,DCM由四个独立的功能单元组成:(1)延迟锁定环路(Delay-Locked Loop,DLL);(2)数字频率综合器(Digital Frequency Synthesizer,DFS);(3)数字相移器(Phase Shift,PS);(4)状态逻辑(Status Logic,SL)[1]。此外,DCM还有一个重要的动态可重配置功能。

2.1 DLL模块

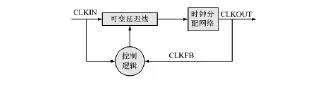

DLL模块由一条可变的延迟线和控制逻辑组成。延迟线由延迟单元组成,输入的时钟经过延迟线,每个延迟单元的输出代表着输入时钟的不同延迟版本。DCM输出的时钟信号经过全局缓冲器到达FPGA内部各个模块的延迟是相同的,但是与DCM输入时钟有一个固定的走线延迟,为了消除这段延迟,DCM中引入了反馈时钟CLKFB,通过CLKFB与输入时钟相比较,调节控制延迟单元的个数,使得CLKFB与输入时钟同相,消除走线延迟[2],使得到达各个模块的时钟与FPGA输入管脚的时钟同相。DLL原理框图如图2所示。

图2 DLL原理框图

2.2 数字频率综合器

数字频率综合器提供了强大的频率综合功能,除了直接实现时钟的倍频外,还提供一个倍频系数M与分频系数D,M和D可以为任意的正整数,输出频率可以是M/D表示的输入时钟频率的任意函数,可以输出多种时钟频率。

2.3 数字相移器

DCM的数字相移器提供粗粒度和细粒度两种时钟相移。对于粗粒度相移控制,DCM直接输出四种时钟CLK0,CLK90,CLK180,CLK270,这四种输出依次相对移相1/4个输入时钟周期。此外,CLK2X180和CLKFX180分别提供CLK2X和CLKFX的180°粗调相移。粗粒度相移直接从DLL的延迟线产生。数字相移器提供的细粒度相移可以精确的调整输出时钟与输入时钟之间的相位关系,细粒度相移使用CLKOUT_PHASE_SHIFT和PHASE_ SHIFT属性来调节输出时钟的相位[3]。DCM中时钟的移相是相对CLKIN而言的。DCM中的细粒度时钟相位调整为:

相移(ns)=(PHASE_SHIFT/256)*FCLKIN

其中FCLKIN为输入时钟CLKIN的频率。

DCM中数字相移器可以提供正负相位的调整,在VARIABLE_ CENTER和FIXED模式下,PHASE_SHIFT属性的全范围始终是-128到+128。在VARIABLE_POSITIVE模式下,PHASE_SHIFT属性的范围是0到+255,可以实现输入时钟的1/256相位的精确调整。

2.4 状态逻辑

状态逻辑表示出DCM的工作状态。STATUS[7:0]只有低3位有定义;STATUS[0]置高时,表示DCM相移溢出;当STATUS[1]置高时,表明CLKIN端没有输入时钟;当STATUS[2]置高时,表明CLKFX端没有输出信号。

2.5 动态重配置

动态重配置端口可以实时加载来更新DCM的初始设置,不需要重新启动电路。动态重配置端口可以完成以下功能:

(1)可动态调整倍频系数M与分频系数D,产生新的时钟频率。

(2)可动态调整相移因子PHASE_SHIFT值,产生新相移。

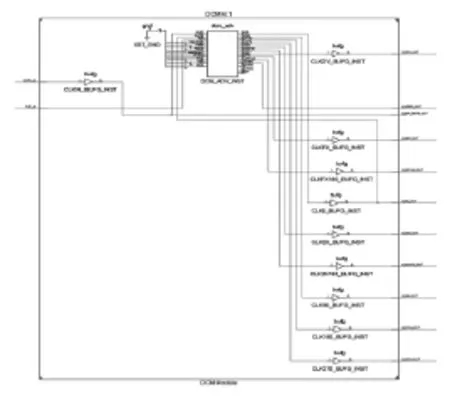

图3 FPGA中DCM硬件电路示意图

3 DCM的设计与应用

DCM是FPGA重要的资源,本文以Xilinx Virtex-5系列的FPGA为例来研究DCM IP核的设计与使用。在Virtex-5系列的FPGA中集成了DCM的IP核,用户使用时,直接配置IP核即可。配置代码如下所示。

DCMM DCMModule (

.CLKIN_IN(clkin), //输入时钟信号

.RST_IN(reset), //输入复位信号

.CLKDV_OUT(clkdv), //输出可配置分频信号

.CLKFX_OUT(clkfx), //输出反馈信号

.CLKFX180_OUT(clkfx180), //输出反馈信号的反相信号

.CLK0_OUT(clk0), //输出与输入时钟同相信号

.CLK2X_OUT(clk2x), //输出倍频信号

.CLK2X180_OUT(clk2x180), //输出倍频信号的反相信号

.CLK90_OUT(clk90), //输出移相90度的时钟信号

.CLK180_OUT(clk180), //输出移相180度的时钟信号

.CLK270_OUT(clk270), //输出移相270度的时钟信号

.LOCKED_OUT(locked) //输出锁定信号

);DCM具有强大的时钟管理功能,FPGA内部通过DCM可以产生各种需求的时钟信号,满足不同系统对时钟频率的要求。并且通过代码可以直接修改时钟频率,大大简化系统的工作量,能够满足各种应用需求,此外DCM中的LOCKED信号表明DCM已正常工作,可以用作电路中其它模块的复位信号。FPGA中DCM硬件电路示意图如图3所示。

图4 DCM产生的时钟信号

通过图3可看出所有的输出时钟都接入到全局时钟缓冲器。全局时钟缓冲器输出的时钟信号到达各个触发器的延迟相等,可以消除走线延迟对触发器同步产生的影响。输出时钟的同相位CLK0经过走线后接入CLKFB输入端,消除走线延迟,始终保持输入时钟与输出时钟同相。DCM产生的各种频率的时钟信号如图4所示。

4 结论

时钟是FPGA电路正常工作不可或缺的部分。FPGA中DCM具有频率合成,相移调整、动态可重配置等功能。本文介绍了Xilinx系列的FPGA中DCM的设计和使用,通过仿真产生不同频率的时钟信号,可以满足各种应用需求。

[1]李丙玉,王晓东,吕宝林,刘文光.FPGA设计中DCM的原理分析及应用研究[J].微计算机信息,2009,12-2:164-166.

[2]贾亮,马兴,孙伟等.基于Xilinx FPGA DCM的研究与设计[J].电子测量技术,2014,10:85-88.

[3]Xilinx.Virtex-5用户指南.Xilinx INC,2007.