PLLFS快速锁定方法的研究与设计

2017-05-13尹军舰赵潇腾李仲茂

赵 雯,尹军舰,赵潇腾,李仲茂

(中国科学院微电子研究所 北京 100029)

PLLFS快速锁定方法的研究与设计

赵 雯,尹军舰,赵潇腾,李仲茂

(中国科学院微电子研究所 北京 100029)

在跳频通信中,锁相环频率合成器(PLLFS)需要在极短的时间内完成频率切换,为此本文分析了典型PLLFS频率锁定时的暂态响应全过程,并提出了一种加速锁定的新环路滤波结构,该结构利用开关二极管的单向导通特性,在频率跳变时加快非线性响应速度,而且不影响频率稳定后的频谱纯度。仿真结果显示,典型滤波结构的锁定时间为219.3 μs,而该滤波结构的锁定时间只有52 μs,极大的加速了PLLFS的频率切换。

频率合成器;锁相环;锁定时间;非线性响应;开关二极管

锁相环频率合成器(PLLFS)输出的信号不仅具有如晶体振荡器般准确且稳定的频谱质量,而且能在很宽的频率范围内实现快速的数字编程控制,是现代无线通信系统中重要的功能器件。随着跳频通信、雷达探测等应用技术的发展,系统的频率切换时间(也称跳频时间)越来越严苛,比如GSM系统中是577 μs[1],GPRS通信标准规定的是200 μs,而4G移动通信TD-LTE标准中缩短到了20 μs[2],这需要设计人员采取各种手段加快锁相环的跳频速度。

但是PLLFS的跳频时间与其输出频率的信道带宽、稳定度、相位噪声和杂散等性能指标相互制约[3-4],又与系统内诸多参数息息相关,我们必须在清楚锁相环的瞬时响应过程后,才能研究出合理加速锁定的方法。为此本文首先分析了具备电流型电荷泵、无源环路滤波器以及分数分频结构的宽带锁相环频率综合器在跳频时输出信号的瞬时响应全过程,这类PLLFS采用了当前应用最为广泛的设计方案,其暂态响应典型代表了锁相环的频率切换过程,为设计加速锁定提供了扎实的理论依据。根据锁相环跳频过程中四个不同时段的瞬时响应特性,着重探讨了影响锁定速度的因素,重新归纳了加速锁定的方法,最后在第4节提出了一种减小锁定时间的新思路,并给出了结构原理图以及仿真验证结果。

1 PLLFS暂态响应全过程分析

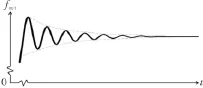

PLLFS的频率锁定经历一个逐渐稳定的过程,图1显示了典型的时域响应波形,为了便于分析,将这一暂态响应全过程分解为4个不同的时段。

图1 PLLFS频率跳变下的暂态响应波形

1.1 第一阶段T1(0-t1):

数字粗调阶段,也称VCO频段选择阶段

通常锁相环集成芯片里的压控振荡器(VCO)分为了多个子频带[5],各子频带VCO的调谐增益和交叠比例基本相同,如图2所示,如此设计既保证了高质量的输出频率,又展宽了输出频率范围,但是系统选择VCO频段较为繁琐,耗时较长[6]。

图2 VCO子频带结构及其电压与频率的关系

频率跳变以系统数字逻辑控制改变锁相环分频比为起始时刻,同时VCO的调谐端与环路滤波器的输出断开并连接到系统内部的数字频段选择控制端,根据跳变的目标频率自动选择出逻辑正确的VCO及其子频段,然后锁相环路正常连接进行后面的动作。第一阶段结束时,VCO被数字粗调到所需频率子频段中心频率附近,调谐端电压正比于输出频率。

在VCO频段选择阶段,数字选择逻辑以鉴相频率作为时钟,一般需要数十个PFD周期完成频段选择,数字时钟不能过高(一般为几百kHz),保证给正确选择频段提供足够的时间。

1.2 第二阶段T2(t1-t2):非线性响应阶段

数字粗调完成后,VCO与环路滤波器联通,锁相环进入正常的锁定过程。由于环路的反馈鉴相特性,动态锁定是一个非线性的复杂过程,锁定过程分为非线性和线性两个阶段[7],在图1中以时刻t2为分界。开始时目标频率和VCO子频段输出频率相差比较大,锁相环非线性响应,频差在环路的反馈调谐作用下逐渐减小,进入锁定频率范围内锁相环的各模块就可用线性s域模型近似表达,锁相环开始线性响应。锁相环的非线性响应阶段并非一定存在,当数字粗调阶段后VCO的输出频率已在目标频率的锁定范围内,并且环路参数设置在合理范围内时,锁相环就直接进入了线性响应阶段。

在时域内,非线性阶段的响应时间可近似由“响应速度(Skew Rate)”确定,其表达式[8]为:

其中ICP是电荷泵电流,KVCO是VCO的调谐增益,C为环路滤波器的所有电容和。若锁相环的响应速度跟不上系统的鉴相速度,那么这段非线性响应时间一定不能忽略[9],因此,也就是时,系统的暂态响应中必须要考虑非线性响应阶段。可见当无法改动VCO的调谐增益时,非线性响应时间和鉴相频率、电荷泵电流以及环路滤波器的参数密切相关。

1.3 第三阶段T3(t2-t3):线性响应阶段

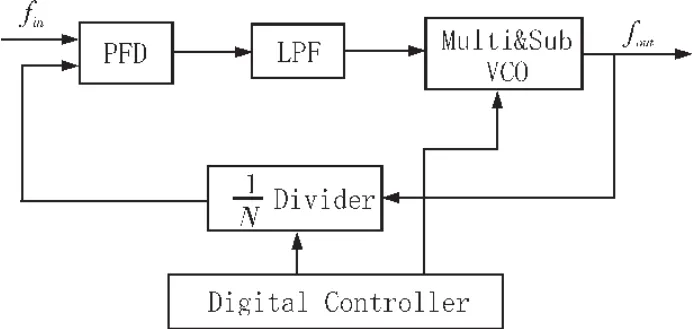

锁相环进入线性响应阶段后,其鉴频鉴相器(PFD)、低通滤波器(LPF)和压控振荡器(VCO)等模块可近似用相位在s域的数学模型表示,如图3所示,根据此模型推导出系统的传输函数,也就是PLL的闭环传递函数为:

图3 锁相环的线性s域相位模型

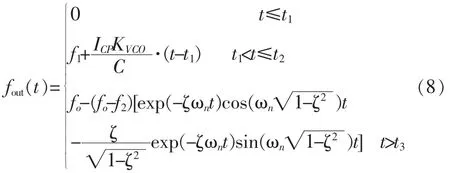

经过拉普拉斯逆变换,将系统H(s)的频域响应变换到时域响应,从而得到PLL输出频率的瞬时响应:

其中,ωn是锁相环的固有频率,与环路滤波器的带宽BW正相关;ζ是系统的阻尼因子,环路稳定时必有0<ζ<1[10]。由此可知,PLL输出频率的线性响应是一个衰减振荡的过程,按t负指数衰减,按-ζωnt频率为的正余弦函数振荡,如图4所示。

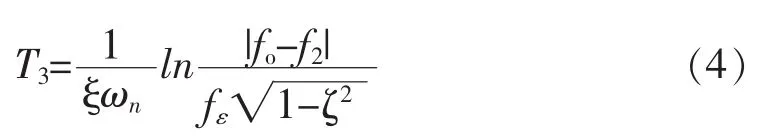

令fε为输出频率fo的精度,表示系统达到频率(fo±fε)即视为锁定,可反解出频率从f2锁定到fo经历的时间[11]:

图4 锁相环输出信号的瞬时线性响应波形

1.4 第四阶段T4(t3之后):锁定跟踪阶段

按锁相环频率综合器的跳频指标,输出频率达到fo±fε的t3时刻即视为锁定,但此时锁相环实际是未达到真正的稳定状态,对于严苛的系统指标来说,我们有必要考虑这段时间内的相位误差以及与之对应的输出信号频差,明确跳频系统的锁定性能。

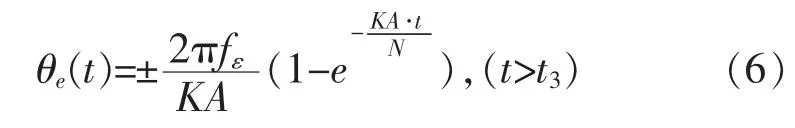

由2.3的分析可知,fout(t3)=fo±fε,fout(t→∞)=fo,我们假设 t3时锁相环的输入频差为 finε(t3)=±fε·ε(t3)/N,ε(t3)是单位阶跃信号,对应的s域输入相位为,并且在锁定跟踪阶段2πfε<<BW环路带宽),因此这段时间内无源环路滤波器的传递函数F(s)≈A,A表示LPF的直流增益或衰减。

输出相位误差为:

同样经过拉普拉斯逆变换求解出接近锁定时相位误差的瞬时响应:

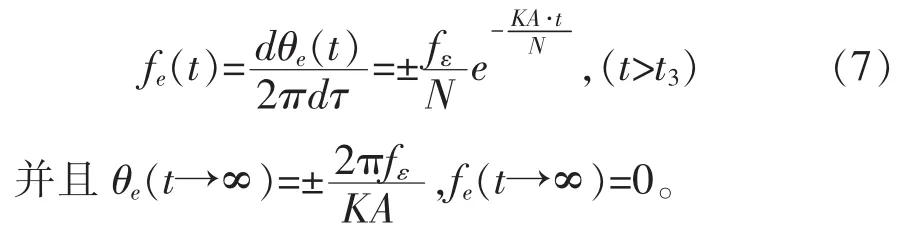

对应的瞬时频差为:

综合以上分析,我们得到了PLLFS输出频率跳变过程中的的全部暂态响应:

对应的锁定时间为:

其中,M为VCO频段选择所需的PFD周期数,f1近似为VCO某子频段的中心频率,|fo-f2|是PLL的锁定范围(也称快捕带),在电荷泵结构中近似为

通过式(9)可以看出,PLLFS的跳频速度在数字粗调阶段由鉴相频率控制,在非线性响应阶段主要取决于频差(f2-f1)、环路滤波器的总电容和电荷泵电流,在线性响应阶段与系统的固有频率ωn、阻尼因子ζ以及输出频率精度成反比。根据这些影响锁定时间的系统参数,人们采取了许多方法来加速锁定,所以在下一节,针对这3个不同的响应阶段,归纳了当前普遍采用的减小锁定时间的方法。

2 减小PLLFS锁定时间的方法

2.1 提高数字粗调速度的方法

2.1.1 提高鉴相频率

加快VCO频率选择速度可以减小响应时间,但鉴相频率(即芯片的工作时钟)与数字逻辑的采样率以及锁相环路的整体性能密切相关,提高的频率十分有限。

2.1.2 预置调谐电压

变系统自动选择逻辑为直接预置,在控制分频数N跳变的同时,预先求得目标频率对应的VCO子频段及其调谐电压,如图5所示,从而减小环路循环的过程,加快锁定[13]。

图5 预置调谐电压的锁相环结构

2.2 提高非线性响应速度的方法

2.2.1 加大电荷泵电流

由式(1)可知,增大电荷泵电流可加快非线性时段的响应速度,但是单纯的加大电荷泵电流会改变锁相环路的带宽,极易引起VCO调谐端的电压抖动,增加输出频率的相位噪声和杂散[14]。因此实际应用中一般采用双电荷泵环路结构,如图6所示,环路失锁时开关闭合,大电流电荷泵接入系统环路,同时环路带宽增加,锁相环快速锁定,当输出频率稳定后,开关断开,环路电荷泵电流减小,带宽变窄,使PLLFS的频谱纯度满足系统要求[10]。

图6 增大电荷泵电流的电路设计方案

2.2.2 减小环路滤波器电容

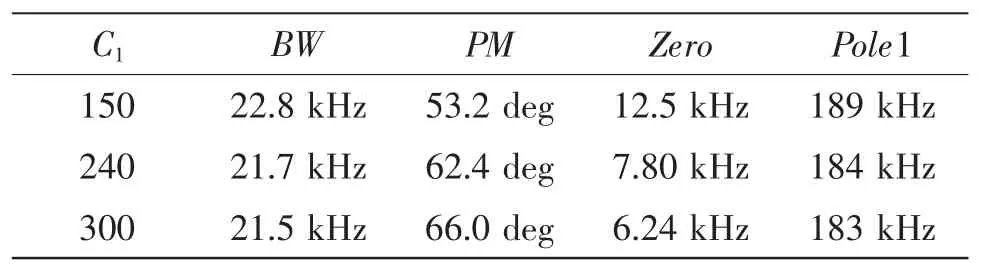

为了保证PLL闭环控制系统的稳定性,无源环路滤波器的阶数、环路带宽、相位裕度和零极点都有严格的限定[15],受此约束,图7中的二阶或三阶无源LPF的电容参数总是有C1>>C2,C1>>C3,所以这类环路滤波器的总电容C≈C1,在设计LPF时尽量减少电容值C1有利于提高系统的非线性响应速度。特别的,图8的仿真结果说明,锁相环在保持环路带宽(BW)基本不变的前提下(如表1所示),电容C1越小,系统的瞬时响应速度越快,锁定时间越短。

图7 二阶和三阶环路滤波器的结构示意图

表1 环路参数对比

仿真时锁相环路的其他参数固定如下:Fref=25.6 MHz,ICP=2.5 mA,KVCO=40 MHz/V,N=93+111/ 128,R1=85 Ohm,C2=10 nF,C3=500 pF,R3=300 Ohm, Pole2=1.12 MHz。

图8 不同 时的瞬时仿真波形

2.3 提高线性响应速度的方法

2.3.1 采用分数分频

受锁相环系统稳定性的约束,环路带宽应小于鉴相频率的1/10,而在分数分频PLL中,根据等式fout=N·fPFD,N为分数,则输出频率的分辨率 (信道宽度)不再等于鉴相频率,也就是说环路带宽不再受到输出频率分辨率的限制,可以成倍提高鉴相频率以加大环路带宽,减小锁定时间。

2.3.2 动态环路带宽

环路带宽越大,频率锁定速度越快,但锁相环的参考杂散和相位噪声也急剧恶化,因此实际应用中不能单独增加带宽来缩短锁定时间,而是采用动态变换的方式,增大环路带宽以加快锁定速度;在频率锁定时,减小环路带宽,来保证输出的频谱质量。通常在增大带宽的同时再增大电荷泵电流,进一步加快锁定。

3 一种加速非线性响应的新思路

3.1 设计原理

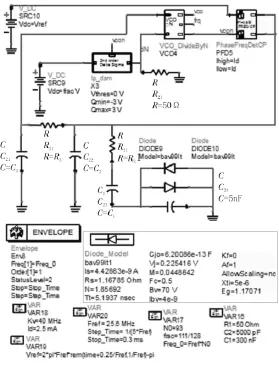

根据1.3以及2.2.2的分析,在非线性响应阶段,跳频速度与系统环路带宽(BW)并不直接相关,并且式(1)可以近似为:,在不改变系统其它参数的情况下,与成反比。类比于动态环路带宽的设计思想,我们希望在跳频过程中的非线性响应阶段较小以加速锁定,响应结束后又较大以保证锁相环的高性能指标,据此思路设计的原理结构如图9所示。

图9 加速锁定结构设计

图9中给三阶环路滤波器的电容C1串联了一个小电容Cp(Cp<<C1),使总电容,由C=Q/U并且电容串联时电荷量相等可知端电压UP>>U1,但是Cp又与一对开关二极管并联,当Cp两端电压充电或放电到使其中一个二极管正向导通时就被钳位,相当于Cp被旁路。因此当频率跳变时,若目标频率比原频率高则电荷泵电流IUP有效,LPF内的电容开始充电,电容Cp起主要作用,锁相环的非线性响应速度加快,根据可知电容Cp两端的电压迅速增大使一个二极管导通,这时电容Cp失效而电容C1继续充电,环路滤波器恢复原有结构,锁相环继续后面的瞬时响应。同理,若目标频率比原频率低则电荷泵电流IDN有效,LPF内的电容开始放电,仍然是Cp先起主要作用加速非线性响应,当另一个二极管导通时Cp失效而端电压不变,电容C1继续放电进行后面的响应。

3.2 软件模拟与仿真结果

下面给出利用该加速非线性响应技术设计的锁相环仿真验证结果。PLLFS的系统结构如图10所示,模拟PLL芯片ADF4351的参数特征,参考频率Fref=25.6 MHz,电荷泵电流ICP=2.5 mA,调谐增益KVCO=40 MHz/V,不考虑VCO的频段选择,输出频率从2380.8 MHz跳变到2403 MHz。选用三阶无源环路滤波器,电容Cp被旁路时的环路带宽为15.2 kHz,相位裕度为52.7 deg,C1=300 nF,CP=5 nF,开关二极管的SPICE模型按BAV99LT1G芯片的参数设置。

图10 基于ADF4351的加速锁定结构原理图

对典型滤波结构和新滤波结构的锁相环路分别进行瞬时特性仿真,输出频率的瞬时响应曲线如图11所示,典型滤波结构的锁定时间为219.3 μs,而新滤波结构的锁定时间只有52 μs,比典型结构减少了167.3 μs,仿真结果说明了这种新的环路滤波结构能最大程度的加快PLL的非线性响应速度,明显减小了锁定时间。

图11 ADS瞬时仿真验证结果

4 结束语

通过研究典型的锁相环频率合成器在频率跳变时的4个瞬时响应阶段,得到了锁定时间与系统各参数的制约关系,并以此为根据归纳了加速锁定的设计方法。为降低锁相环在非线性响应阶段的时间,给出了动态改变系统参数的滤波结构,只在无源环路滤波器中增添一个小电容和一对开关二极管,就得到了媲美动态环路带宽方法的快速锁定效果,极大的简化了设计复杂度,又没有额外的增加系统功耗,输出频率的信道带宽、稳定度、相位噪声和杂散等性能指标均不受影响。ADS的仿真结果验证,新环路滤波结构能最大程度的加快锁相环的非线性响应速度,有效的减小锁定时间。这种加速非线性响应的新思路填补了PLLFS快锁模式的设计空白,为进一步提升跳频通信的性能提供了可行方案。

[1]王志勤,魏然,王小云.全球移动通信系统(GSM)的技术及发展[J].电信科学,1996(4):9-18.

[2]黄武.一种TD-LTE综测仪中跳频合成器的设计[J].电子设计工程,2014(22):171-173.

[3]Banerjee B.PLL Performance,simulation,and Design.3rd Edirion[C].15th IEEE International Conference on 3rd Edition.Aug.2012,35(21): 802-805.

[4]远坂俊昭.锁相环电路设计与应用[M].北京:科学出版社,2006.

[5]徐野.基于锁相环的快速跳频源的设计[D].沈阳:沈阳工业大学,2015.

[6]尹雪曼.宽带锁相式频率合成器快速锁定模式研究[D].上海:复旦大学,2008.

[7]Rhee W,Multi-bit delta-sigma modulation techniqueforfractional-N frequencysynthesizers[D].Ph.D,University of Illinois,Urbana-Champaign,2001.

[8]Rui He,Jun Li.Transient analysis of nonlinear settling behaviorin charge-pump phase-locked loop design[C].International Symposium on Circuits and Systems(ISCAS),2009:469-472.

[9]V.Manassewitsch,Frequency Synthesizers,Theory and Design[M].New York:JohnWiley&Sons,1987.

[10]Dean Banerjee.PLL Performance,Simulation and Design,4th Edition[M].National Semiconductor Corporation,2006.

[11]陈敏华,李江夏,时翔,等.基于锁定时间分析的锁相环频率合成器 [J].微波学报,2012,28(1): 57-61.

[12]Shu K,Sanchez-Sinencio E.CMOS PLL Synthesizers:Analysisand Design[M].New York:Springer,2005.

[13]Kuang X F,Wu N J.A fast-settling PLL frequency synthesizer with direct frequency presetting[C]// IEEE International Solid-State Circuits Conference,2006:741-750.

[14]Hanumolu P K,Brownlee M,and Moon Un-Ku. Analysis of charge-pump phase-lock loops[J]// IEEE Trans.on Circuits and Systems I,2004,51(9):1665-1674.

[15]简科军,马成炎,龚敏,等.采用快速锁定技术的Σ-ΔFractional-N PLL行为仿真 [J].电子器件,2007(5):1704-1707.

Analysis and design of fast-lock methods for PLLFS

ZHAO Wen,YIN Jun-jian,ZHAO Xiao-teng,LI Zhong-mao

(Institute of Microelectronics of Chinese Academy of Sciences,Beijing 100029,China)

Infrequency-hopping communication,the frequency-switchingprocess of Phase-locked loop frequency synthesizer (PLLFS)needs to be completed in a very short time.Based on this situation,this papercomprehensively analyses the whole transient response of typical PLLFS and designs a newloop filter structureto speed up locking.By using the unidirection continuity of the switching diode,the improved structurespeeds up frequency hopping but does not affect the output spectrum purity.The ADS simulation results show that the locking-time oftypical structure is 219.3 μs,but the improved structure is only 52 and it greatly accelerates PLLFS frequency-switching.

frequencysynthesizer;phase-locked loop;locking-time;nonlinear response;switching diode

TN99

A

1674-6236(2017)09-0162-05

2016-03-27稿件编号:201603356

赵 雯(1989—),女,辽宁抚顺人,硕士研究生。研究方向:无线通讯射频微波模块研制。