基于PCI Express总线的同步时钟卡的设计与实现

2017-05-09陈永志魏丰王旭东

陈永志,魏丰,王旭东

(华中科技大学 自动化学院,湖北 武汉 430074)

基于PCI Express总线的同步时钟卡的设计与实现

陈永志,魏丰,王旭东

(华中科技大学 自动化学院,湖北 武汉 430074)

本文介绍了一种基于PCI Express(简称PCI-E)总线的同步时钟卡的设计与实现,简要叙述了自行研发的PCI-E同步时钟卡的系统架构及工作原理。基于本卡小批量数据传输和响应中断的特点,提出一种用CH367芯片联合单片机、双口RAM、CPLD等芯片来设计GPS同步时钟卡的硬件设计方案,并用VC++开发设计应用软件用于满足时间的测试与显示需求。测试结果证明同步时钟卡工作稳定,保证了数据传输的连续性和完整性。

PCI Express总线;CH367;小批量数据;同步时钟卡

时间是基础研究、科技实验和自动控制系统等领域的一个非常重要的参数,它为电力自动化系统中的时序计量提供了至关重要的时间基准[1]。电力系统中的故障录波和故障诊断等,需要毫秒级的精确时间计量。为了实现系统中各个设备之间时间的一致性和准确性,系统中配备时钟源进行授时,同步时钟卡从时钟源获取高精度的时间,使系统中各个设备与主机时钟源保持高精度的同步。

同步时钟卡采用PCI-E总线的方式,PCI-E总线具有点对点串行互联,双通道、高带宽、传输速度快的特点,总线性能的优势是非常明显的[2-3]。由于同步时钟卡传输的数据量小,速度快的特点,本设计没有采用应用广泛的PCI-E总线专用桥接芯片PEX系列,而是运用一种新型的桥接芯片CH367来简化总线驱动并加以实现,从而大大简化硬件设计难度和制作成本。

1 同步时钟卡系统架构

自行研发的PCI-E同步时钟卡,其总体结构图如图1所示。本同步时钟卡主要分为单片机控制,双口RAM模块,CPLD本地逻辑控制,CH367桥接芯片等部分组成。

图1 系统总体结构图

同步时钟卡从时钟源接收时钟信号,单片机对信号进行解析生成高精度的时间信息,根据控制逻辑CPLD产生的PPS秒脉冲中断信号解码IRIG-B格式时间码[4],得到当前基准时间,并产生精确到200 μs的绝对时标,将时标连续写入双口RAM中,PC机通过PCI-E总线控制CH367读入双口RAM中的200 μs的时标信息,从而得到高精度的绝对时间。PC机可以主动查询双口RAM中的数据,也可以由外部事件通过中断通知PC机,从而读取双口RAM中的数据。文中主要介绍如何使用桥接芯片CH367,设计和实现PCI-E同步时钟卡,完成外部数据与PC机的传输交换。

2 同步时钟卡的硬件设计

PCI-E总线是第三代IO总线技术,这是一种全新的总线规范[5]。不同于PCI总线的共享并行架构方式,PCI-E总线采用的设备通讯方式是端到端的串行通信,这使得每个PCI-E设备都拥有独自的数据连接,不同设备同时进行数据交互时不会相互干扰,保障了数据传输的完整性和可靠性[7-8]。下面介绍本同步时钟卡数据交换电路设计和PCI-E总线接口的实现。

2.1 同步时钟卡的数据交换设计

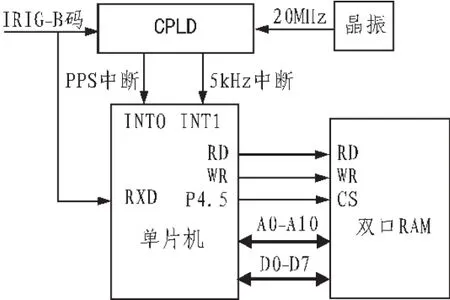

2.1.1 时间刻度的生成

为了满足毫秒级的时间精确计量,因此设计200 μs的时间刻度足以满足要求,产生200 μs时间刻度的原理图如图2所示。恒温晶振生成20 MHz的频率,经控制逻辑CPLD分频产生5 kHz、25 Hz、秒脉冲等信号。IRIG-B码时间信号对分频产生的各种信号进行同步处理。同步后的秒脉冲PPS信号用于中断单片机,单片机在中断INT0中解码IRIG-B时间码得到精确的时标信息,包含年、月、日、时、分、秒等信息,并存储存在单片机中,并完成整秒清零操作,此刻时间精度为秒。同步产生的5 kHz用于中断单片机,每次中断将200 μs的计数值加1,即每一个计数值代表200 μs,将时标信息和毫秒计数值组合成时间刻度,使时间精确到毫秒级别。单片机控制片选选中双口RAM芯片,控制WR信号有效,将时间刻度写入双口RAM中。

PC机要读取解析后的时间刻度,高速PC机与低速单片机共享双口RAM中的数据,那么读取速率不匹配会严重影响数据的准确性和稳定性。即当PC机通过总线读取双口RAM中的数据时,单片机此时也正在向双口RAM中书刷新存储数据,则PC机无法读到准确的时间数据,本设计采用一种奇偶页数据交换的方案解决这个问题。

2.1.2 奇偶页的数据交换

为了解决数据读取速度匹配问题,可以将双口RAM中的地址分为两部分,奇页和偶页,对应地址区间为10H--1BH和20H--2BH。单片机交替向奇偶页写入时间刻度,时间刻度包含时标信息和200 μs计数值。当单片机向奇页写完时间刻度数据时,将0FH地址中的数据标志置为0x80,当5 kHz中断信号触发中断,将200 μs的计数值加1,写入偶页并置0FH地址中的数据标志为0x00。如此交替分别向奇偶页写入数据,共可写2 500个时间刻度。当上位机应用软件读取数据时,可根据0FH地址中的数据标志来判断哪一页的数据是有效的。

图2 200 μs时间刻度生成原理图

图3 双口RAM数据格式图

双口RAM中地址00H--2BH中存储数据的含义如图3所示,其中地址10H--1BH为数据奇页,20H--2BH为数据偶页,地址0FH是PC机读取时间刻度时判定奇偶页中哪一页数据为有效的标志。地址00H--09H是用于PC机将时间数据写入供单片机读取,当没有时钟源信号时用PC机的时间来对时同步时钟卡。地址09H的值是时钟数据准备就绪标记:若值为55H,则表示用PC机同步对时;若值为00H,则表示PC机时间更新单片机完成。应用程序要用PC机同步对时,将当前的PC机的时间写入双口RAM的地址00H--08H,地址09H的值置为55H。单片机查询地址09H时,若值为55H,则用该时间值更新时钟芯片DS1302中的时间,并置09H的值为00H。

2.2 PCI-E总线接口实现

2.2.1 桥接芯片CH367性能简介

PCI-E总线的桥接芯片采用沁恒电子研发的一种新型桥接芯片CH367,能够将高速的PCI-E转换成易用的8位并行接口,支持I/O端口映射和扩展ROM以及中断请求。其主要特点是:支持I/O读写,自动分配I/O基址,支持长度为232字节的端口;存取数据可达到每秒1 MB;支持两线串行接口的EEPROM用于存储非易失数据;支持电平中断或边沿中断请求,支持中断共享;内含硬件计数单元,支持低功耗的睡眠模式等[10]。CH367芯片在需要的时候可进入睡眠状态,可大大降低电流的功耗,本卡只是进行小批量数据传输,需要中断功能,使用该芯片开发简单节省开发时间,所以CH367是桥接芯片的最好选择。

2.2.2 基于CH367的接口设计

CH367接口芯片与 PCI-E总线连接,可将CH367的8位数据总线 (D7-D0)和8位地址总线(A7-A0)分别与存储器双口RAM对应的总线直接相连,通过控制读信号RD和写信号WR来实现对存储器的访问,CH367还能接受来自其他芯片的如CPLD或单片机的INT#中断信号,从而中断PC机。通过CH367芯片的IIC总线可串联EEPROM用于定制设备的VID和DID等信息,通过SPI总线可串来FLASH用于保存掉电后需要保存的应用数据。PCI-E总线配置空间可被设备用来向系统提供设备自身的基本信息[11-12],系统也可以通过配置空间控制和获取设备的状态,其中地址13H—10H这四个字节是用于存储I/O基址值。I/O基址的相关寄存器及本地I/O端口的实际地址为配置空间中地址为I/O基址值加上下表中寄存器的偏移地址。CH367芯片的I/O空间总共有256个字节,芯片内部的寄存器占用了24个字节(FFH--E8H),剩余的地址E7H--00H是长度为232个字节的I/O端口空间,可映射到外部双口RAM的存储区域。当同步时钟从卡插到PCI-E总线上后,系统会将CH367芯片的这256个I/O资源映射成系统的虚拟地址,从而PC机可以直接访问双口RAM。

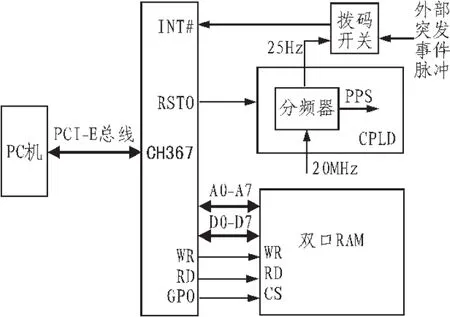

图4 同步时钟卡PCI-E总线接口图

此同步时钟卡PCI-E总线接口设计图如图4所示。将解码后的200 μs时间刻度写入双口RAM后,PC机通过中断方式或查询方式读取时间刻度。CPLD控制逻辑将20 MHz频率进行分频产生秒脉冲PPS和25 Hz脉冲信号,拨码开关可在25 Hz周期性信号和外部突发事件脉冲中进行选择来中断PC机。PC机收到中断信号后,使芯片CH367的RSTO引脚有效,控制CPLD清除中断源信号INT#。然后CH367的GPO引脚控制并选中双口RAM片选信号CS,通过读信号RD来读取双口RAM中地址00H--2BH区间的所有数据,并根据地址0FH的值来判断奇偶页的数据有效性。在没有时钟源信号时,PC机应用程序通过控制CH367芯片GPO引脚片选选中双口RAM,并控制WR信号有效,从而将其当前时间写入双口RAM中地址00H--09H中。

3 系统软件设计

本系统的软件设计应包括驱动程序和上位机应用软件。桥接芯片CH367的硬件驱动是以PCI-E总线为基础的,由于芯片驱动已由厂家提供故本系统只涉及上位机的应用软件设计。应用软件的开发环境为Microsoft Visual Studio 2013,设计的界面运行于Windows 7平台。根据驱动程序中为设备创建的符号链接名打开指定硬件设备[13],如果此时驱动及装置都有效便可成功打开,如无效则会提示设备打开失败,打开成功后,系统会自动加载驱动版本号、DLL版本号、中断号、IO基地址[14-15]。一方面可以用查询方式和中断方式读取200 μs的时间刻度为PC机对时,并将获取到的时间数据按照一定格式显示出来,如图5所示。另一方面也可将PC机的当前时间写入到同步时钟卡的双口RAM中,达到用PC机对时同步时钟卡的目的,从而实现时钟卡与上位机之间的数据交互。

图5 测试界面图

4 结束语

对于PCI-E总线小批量的数据传输,本系统使用新型的桥接芯片CH367来完成接口实现,并且设计了200 μs时间刻度的产生电路以及将200 μs时间刻度提供给PC机的数据交换电路,完成了PC机与同步时钟卡的时间信息的传输。通过应用程序来测试功能实现,结果表明200 μs的时间刻度完整未出现丢失,中断对时方式和定时查询对时方式都成功获取到了同步时钟卡中的时间信息,时间数据传输稳定可靠。本卡应用在电力系统的故障录波和事件记录等装置中,不仅满足了电力系统所需的授时精度和时间分辨率,而且有效解决电力系统的故障录波和故障诊断的问题,大大降低了设计成本。

[1]雷震,魏丰.IRIG-B格式时间码在GPS同步时钟卡中的应用[J].现代电子技术,2004(5):75-79.

[2]李丹,贺占庄,李灏.PCI Express总线接口板的设计与实现[J].现代电子技术,2009,32(4):158-161.

[3]马萍,唐卫华,李绪志.基于PCIExpress总线高速数采卡的设计与实现[J].微计算机信息,2008,24(9):116-118.

[4]平步青.基于FPGA的IRIG_B编解码系统设计与实现[D].江苏 :苏州大学,2012.

[5]周立国,梁淮宁,谢冬冬.基于PCI Express总线的数据传输卡的设计与实现 [J].电子测量技术,2007,30(11):28-31,39.

[6]曾祥君,尹项根,林干.晶振信号同步GPS信号产生高精度时钟的方法及实现[J].电力系统自动化,2003(8):49-53,89.

[7]王祥.基于FPGA的PCI-E数据采集系统的设计与实现[D].成都:电子科技大学,2012.

[8]张斌,张东来,王超.基于FPGA的IRIG-B(DC)码同步解码设计[J].测控技术.2008,27(2):45-479.

[9]Ravindran M.Cabled PCI Express-a standard highspeed instrument interconnect[C].Proc.of IEEE Autotestcon,2007.

[10]沁恒电子.CH367中文接口手册[EB/OL].(2014-07-15).http://www.wch.cn.

[11]唐彬.基于PCI-E的嵌入式B码时统终端研究与设计[D].安徽:安徽理工大学,2014.

[12]周骞,陈金树.超高速数据采集存储系统的设计与实现[J].计算机应用研究,2003,10(8):139-141.

[13]张小磊,孟李林,崔晨琪.基于KMDF的PCI Express设备驱动设计 [J].西安航空学院学报,2014,32(1):59-63.

[14]武安河.WINDOWS设备驱动程序WDF开发[D].北京:电子工业出版社,2009.

[15]刘娟,田泽,黎小玉.PCI-E接口驱动软件设计与实现[J].计算机技术与发展.2012,22(8):53-56.

Design and implementation of synchronous clock card based on PCI Express bus

CHEN Yong-zhi,WEI Feng,WANG Xu-dong

(School of Automation,Huazhong University of Science and Technology,Wuhan 430074,China)

The paper introduces a design and implementation of synchronous clock card based on PCI Express(Abbreviated for PCI-E)bus,and describes briefly the system architecture and works on our own PCI-E synchronous clock card.Based on the characteristics of small batch data transmission and interrupt response of this card,the design uses the CH367 chip,microcontroller,dual port RAM,CPLD and other chips to complete the hardware circuit of the GPS synchronous clock card,then designs application interface to satisfy time test and display by VC++.Finally,test results proved that the synchronous clock card works stably,which ensure continuous data receiving and the integrality of the data.

PCI-E;CH367;small batch data;synchronous clock card

TP336

:A

:1674-6236(2017)01-0106-04

2016-01-13稿件编号:201601095

陈永志(1989—),男,河南林州人,硕士研究生。研究方向:检测技术与自动化装置,仪器仪表。