基于双线性插值算法的缩放IP核设计

2017-05-08邹学瑜刘昌禄胡敬营��

邹学瑜+刘昌禄+胡敬营��

摘要:设计了基于双线性插值算法的IP核,通过减少乘法器数量,优化了对该算法的实现。针对一般的双行缓冲器不能满足高实时显示要求,及帧存储器成本高且还需另外进行帧存储器的控制逻辑设计的缺点,设计了一个RAM FIFO的缓冲阵列,利用多个RAM存储器保证图像数据存储和时序性控制,它能够有效进行数据缓冲。最后给出了设计的时序仿真,进行结果验证后得到缩放的图像质量较好。通过和已有IP核进行对比,得出绝对平均误差非常小。

关键词:图像缩放;Scaler IP核;双线性插值算法;RAM FIFO

中图分类号:TN911.73文献标识码:ADOI:10.3969/j.issn.10036199.2017.01.023

1引言

图像缩放是液晶显示系统中的一个重要功能,这是因为显示器的分辨率是固定的,但视频源的分辨率是多样的,所以要经过缩放处理[1,2]。图像缩放有多种算法,综合考虑缩放质量与成本,本文选择双线性算法,设计一个针对Scaler IP核。

2双线性插值算法原理

双线性插值的核心思想是利用4个像素点,从行列两个方向各插值一次[3]。其原理如图1所示,逆映射得到的目标像素点S,与其最邻近的左上角点A在水平、垂直方向的距离分别为dx、dy,设原图像像素点间距为1,则dx∈(0,1],dy∈(0,1]。

根据待求的目标像素点与4个相邻像素点的距离关系,进行加权求和,过程如下。水平方向插值公式:

3算法的FPGA实现

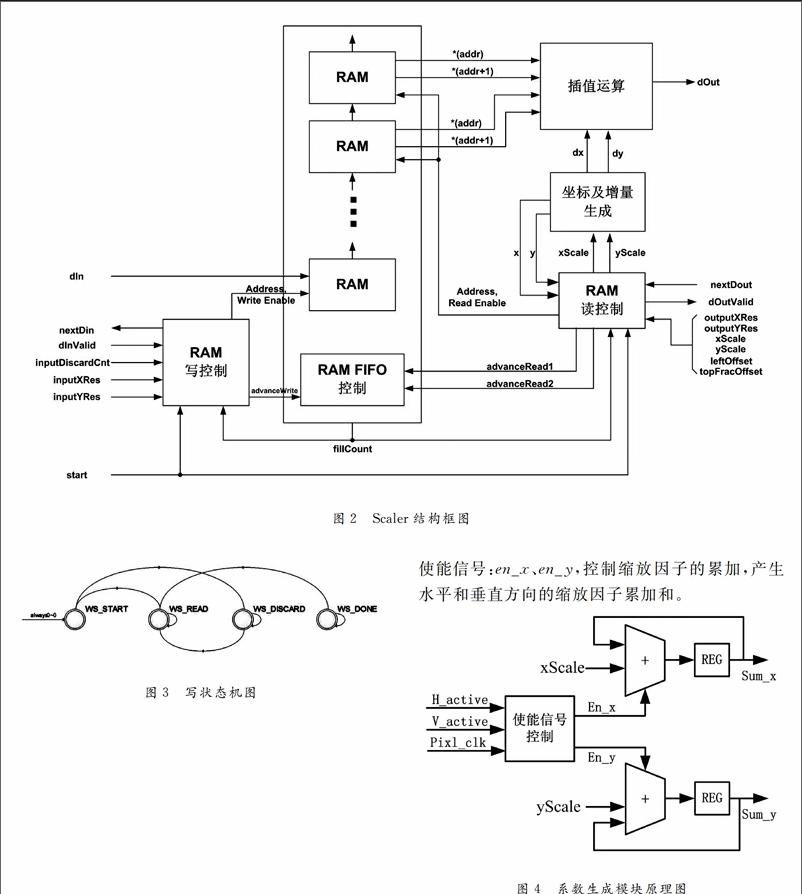

Scaler结构框图如图2所示,包括Ram FIFO模块、RAM写控制模块、RAM读控制模块、坐标及增量生成模块、插值运算模块。

3.1数据存储与时序控制

一般实现方法只使用两个行缓冲器以分别存储插值所需的两行数据,不能满足高实时显示要求[4]。还有利用帧存储器,通过“PingPong”轮换机制实现数据缓冲的方法,这种方法成本高,而且还需另外进行帧存储器的控制逻辑设计[5]。

本文利用FPGA的内部逻辑资源,设计出一个包含多个RAM存储器的图像数据的缓冲阵列,并由FIFO来控制阵列的推进,称为Ram FIFO,合称RFIFO。RFIFO模块配合以相应的RAM读控制模块、RAM写控制模块,共同完成了图像数据存储和时序控制。

RFIFO模块由一组RAM阵列和RAM FIFO控制逻辑组成。可以认为,RFIFO的输入和输出不是单个数据,而是RAM中的块数据,除了这点,它的操作和普通FIFO都一样。RAM存储器的数量根据延迟要求和支持的缩放模式设定,每个RAM提供一个写端口和两个读端口,两个读端口输出插值点所邻近的原图像的两行数据。每个读端口同时地读取*(address) 和 *(address+1)信号,随着连续的视频行数据写入到这些RAM中,插值点最邻近的4个像素点数据就已经为双线性插值准备好。RAM FIFO控制逻辑把这些RAM存储器当做数据一样处理,它根据advanceWrite和advanceRead信号选择对哪一个RAM进行读和写,本着先进先出原则,控制这些RAM的推进。

RAM写控制模块一方面为RFIFO的RAM端口驱动地址和写使能,实现有效数据到存储器的写入;另一方面,当上一个输入视频行被写入时,产生advanceRead信号,推进RFIFO的写端口,这就决定了将输入数据放入哪个RAM中。插值运算模块要使用的所有数据都被写入到FIFO中,称为有效数据,其余数据被舍弃。比如图像缩小时会有很多输入行数据在插值计算中不被使用,为了减少资源占用,这些行数据将直接舍弃,可用inputDiscardCnt信号实现。写RFIFO的状态机如图3所示。RAM读控制模块根据输入输出分辨率信息生成水平和垂直缩放因子,并根据增量生成模块反馈回来的x、y坐标信息驱动RFIFO的RAM端口的地址和读使能,以读取RAM中的相应数据。并且当新的输出视频行被读出时,产生advanceRead信号给RAM FIFO控制逻辑,以推进RFIFO的读端口。

4时序仿真和功能验证

采用Verilog HDL语言进行描述,程序下载到FPGA上,在modelsim环境下进行时序仿真和功能验证。

输入输出时序图如图5所示。首先,用户逻辑在start信号之前置位控制信号。在一帧开始时,start信号被用户逻辑置高一个或者多个时钟周期,这样就在前一帧后复位Scaler模块。然后Scaler从输入数据端口读取视频数据,数据是从左上像素开始以标准的光栅图输入,只有有效视频数据才被送给Scaler,Scaler读入有效行数据直到缓存存满。若被控制信号指定,输入数据将在缓存满之前被舍弃。一旦两行数据被读入,数据就可以开始被从dOut读取。控制信号在Scaler运行时(读入或写出数据)不可以改变,否则将破坏一帧输出数据。在下一帧的开始信号声明之前,控制信号在读出完成后应该改变。

写数据到dIn的时序如图6所示。用户逻辑把初始数据和dInValid一起声明。Scaler响应dIn和nextdIn。当nextdIn和dInValid一起为高电平时,用户逻辑必须改变dIn为其他值。

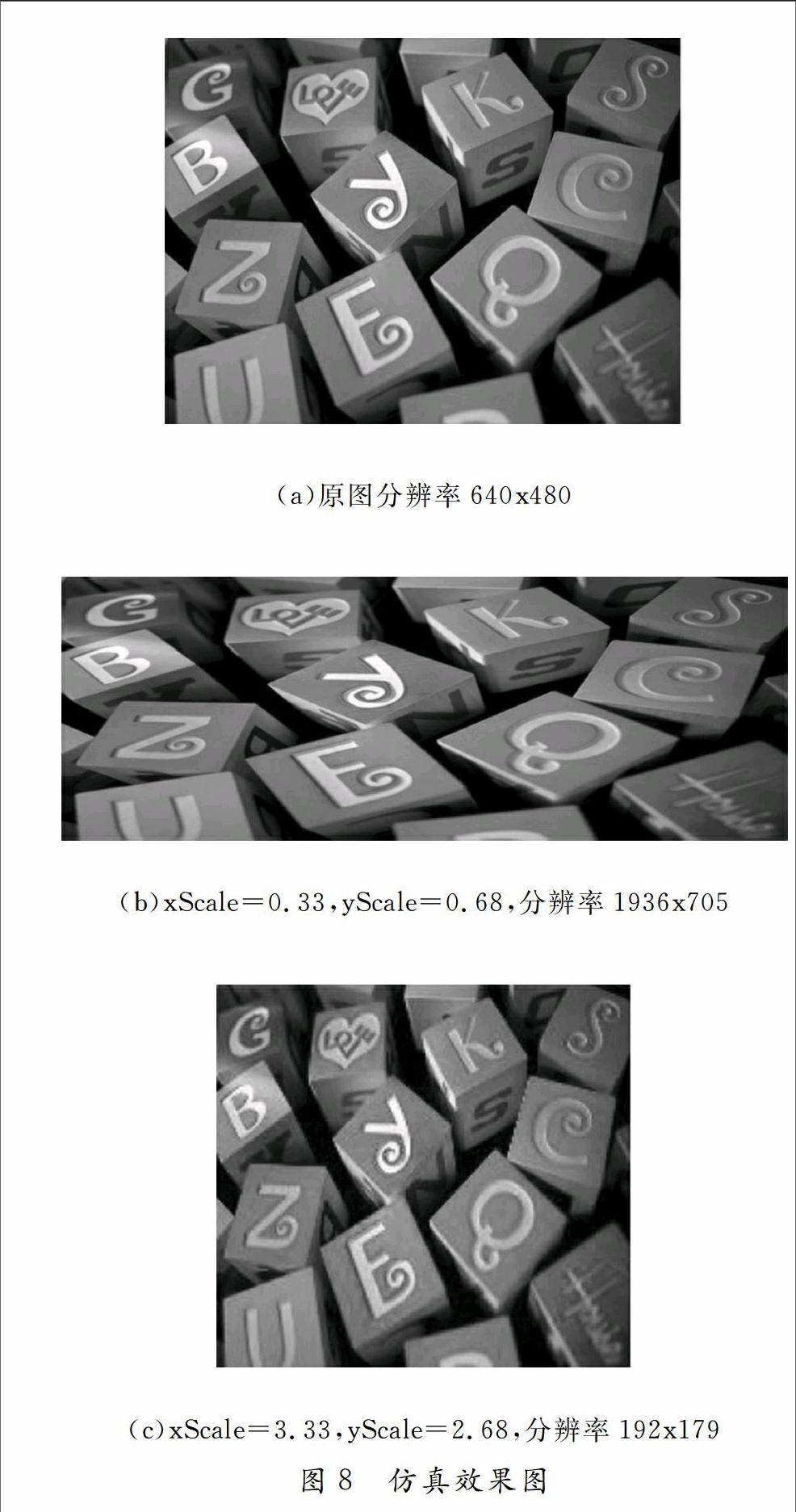

本文设计了一种基于双线性插值法的IP核,采用了RFIFO的控制方法有效的进行数据缓冲,克服了一般双行缓冲器不能满足高实时显示要求、及帧存储器成本高且控制复杂的缺点,在实时性、成本与设计难度上取得了平衡。时序仿真表明该IP核可以正确运行,对例图缩放后得到较好的效果,该IP核和已有IP核的绝对平均误差非常小。因此,该IP核可以应用于显示控制系统的设计与实现,同时IP核的设计方法和RFIFO的控制方法也为其他图像处理和数据缓存的设计提供了参考,对液晶显示控制的开发和设计有一定的参考和应用价值。

参考文献

[1]钟建.液晶显示器件技术[M].北京:国防工业出版社,2014:1-2

[2]ZHENG Huaqiang. Realtime Video Collection and Processing System Based on FPGA, TheThird International Symposium on Test Automation & Instrumentation(ISTAI) ,2010

[3]陳伟,卢贵主,郑灵翔.基于双线性算法的定标器及其FPGA实现[J].电子技术应用,2008(4):40-43

[4]赵坚勇.平板显示与3D显示技术[M].北京:国防工业出版社,2012:15-16

[5]马思博.基于Scaling算法的FPGA验证[D].北京交通大学硕士学位论文,2013.

第36卷第1期2017年3月计算技术与自动化Computing Technology and AutomationVol36,No1Mar. 2 0 1 7第36卷第1期2017年3月计算技术与自动化Computing Technology and AutomationVol36,No1Mar. 2 0 1 7