基于FPGA+W5100的数据传输系统设计*

2017-04-25李锦明张虎威高文刚

郭 淳,李锦明*,朱 平,张虎威,高文刚

(1.中北大学电子测试国家重点实验室,太原 030051;2.中北大学仪器科学与动态测试教育部重点实验室,太原 030051)

基于FPGA+W5100的数据传输系统设计*

郭 淳1,2,李锦明1,2*,朱 平1,2,张虎威1,2,高文刚1,2

(1.中北大学电子测试国家重点实验室,太原 030051;2.中北大学仪器科学与动态测试教育部重点实验室,太原 030051)

为提高存储测试系统的实时性和稳定性,并考虑到数据量较大和数据存储安全的特点,设计了一种新型无线数据传输系统。该系统采用FPGA+W5100架构的以太网接口设计方法,外围电路采用NAND Flash存储器来作数据备份,引入了片外存储坏块地址的方法对Flash的坏块进行检测,并给出了系统的结构组成、硬件连接和软件实现方法。该系统增强了数据存储安全性,满足了远程和复杂环境下数据通信的要求。

数据传输;以太网;W5100;FPGA;NAND Flash;坏块检测

现代数据存储领域中,数据存储、数据采集、黑匣子记录系统等工作过程中要求数据能够准确、安全传输存储,并且经常要利用计算机进行数据处理与计算,所以越来越多的现场采集设备需要扩展网络功能以实现远程控制和数据传输[1]。以太网以其开放性、可靠性、价格低、速度高、传输距离远、多种传输介质可选、连接方式灵活多变、易于组网应用等优势得到广泛应用。而基于WIZnet的W5100解决了传统以太网需软件实现TCP/IP协议栈开发周期长、难度大的问题,同时也增强了系统数据传输稳定性[2]。由于在恶劣和苛刻的环境条件下,数据的采集和回收处理经常受到外界环境的干扰而导致重要数据的损坏和丢失,所以还需要对实时数据进行备份。

鉴于动态测试技术特点要求,设计了基于FPGA、W5100和NAND Flash的数据传输系统。采用W5100实现可靠稳定运行的数据通信,并利用NAND Flash实现对实时数据的备份,通过FPGA强大的并行处理能力,使得W5100对数据的通信和NAND Flash对数据的备份互不干扰。

1 系统的结构组成

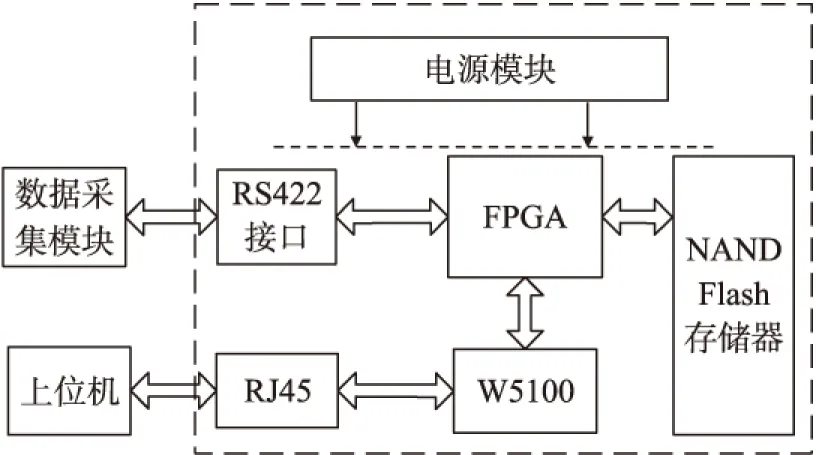

该数据传输系统主要由XILINX公司生产的低成本、高性能的Spartan3E系列XC3S500E FPGA,WIZnet公司的集成了全硬件的TCP/IP协议栈、以太网介质传输层(MAC)和物理层(PHY)网络接口芯片W5100,三星公司生产的大容量数据存储的NAND Flash K9K4G08U0M,RS422接口芯片、双绞线接口RJ45、电源模块组成。系统结构框图如图1所示,数据采集模块的数据经过数据传输系统内部的RS422接口芯片输入到FPGA,经过FPGA的内部统一编帧后,通过W5100芯片传输到上位机的同时存储到NAND Flash中用于数据分析和备份。

图1 系统结构框图

2 系统的硬件设计

硬件设计包括FPGA与W5100接口设计,以及与外部存储器Flash接口电路设计。FPGA的引脚的输入输出可配置性,极大的提高了外围芯片与FPGA接口的灵活性。并且由于使用W5100不需要考虑以太网的控制,只需要进行简单的端口编程,就能实现与上位机的通信,所以作为主控单元的FPGA

主要完成W5100寄存器的初始化和读写时序及NAND Flash的读写时序控制。

2.1 W5100的接口电路设计

W5100内部集成了全硬件的、且经过多年市场验证的TCP/IP协议栈、以太网介质传输层(MAC)和物理层(PHY);并支持TCP、UDP、Ipv4、ICMP、ARP、IGMP和PPPoE等网络协议;内置4个独立的Socket端口,并能同时运行,通信速率最高可达到25 Mbit/s[3]。

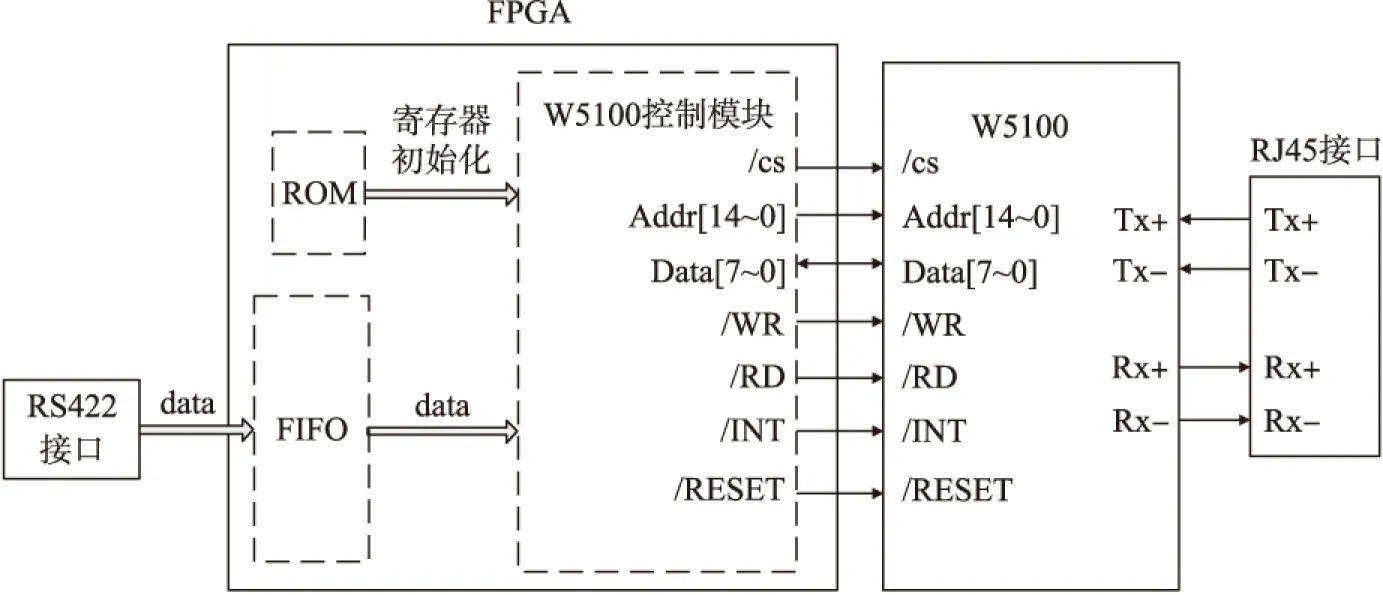

本设计W5100采用直接寻址模式,FPGA通过设置 BIT16EN 信号为高电平将W5100配置成接收模块,直接寻址模式下,FPGA通过地址总线可以访问W5100的内部寄存器。W5100与FPGA的接口信号有15位地址总线(Addr[14~0])、8位数据总线(Data[7~0])以及一些控制信号[4]。W5100与FPGA的接口的原理图如图2所示。

图2 W5100与FPGA的接口

为进一步优化系统性能,RJ45网络接口选择内部集成网络变压器,在实际的电路设计中,RJ45网络接口的发送差分线和接收差分线之间要并联2个49.9 Ω或者50 Ω(精度1%)的终接电阻,主要是为了实现阻抗匹配[5]。这样设计可以增强信号,使其传输距离更远的情况下,使芯片端与外部隔离,抗干扰能力大大增强,而且对芯片增加了很大的保护作用,当接到不同电平的网口时,不会对彼此设备造成影响并且在户外操作时可以有效的抗雷击、静电。

2.2 外部存储器的设计

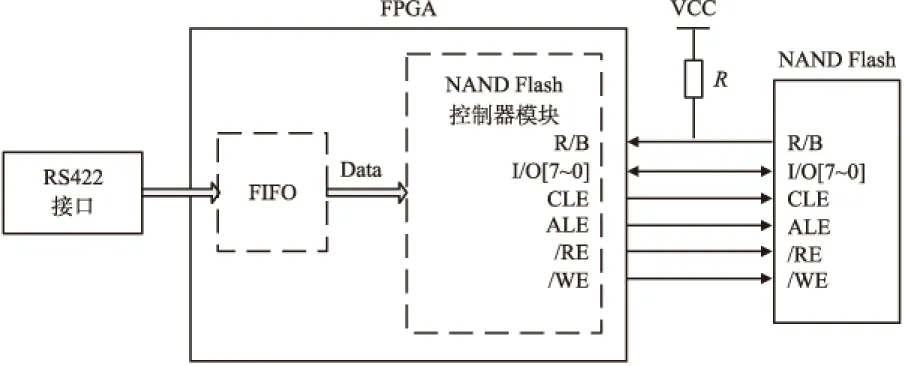

由于在恶劣和苛刻的环境条件下,数据的采集和回收处理经常受到外界环境的干扰而导致重要数据的损坏和丢失,对数据备份也是必需的。而NAND Flash由于大容量,小体积,读写速度快,外围接口电路简单等特点,成为了当今数据存储的最佳选择。本系统采用三星公司的K9K4G08U0M闪存芯片,其具有4 Gbyte的容量,管脚分别为地址、命令和数据复用的接口(I/O0~I/O7),读写控制端口(/RE和/WE),地址锁存(ALE)和命令锁存(CLE),Flash工作状态信号R/B[6]。当Flash处于忙状态时,R/B信号将输出低电平;当Flash处于空闲状态时,R/B信号将输出高电平。由于该信号是漏极开路端口,需要外接上拉电阻。

图3 NAND Flash与FPGA的接口

与FPGA的接口连接如图3所示,经外部数据采集模块将相关的参量采样并转化为数字信号后,通过422串行总线传输给系统,系统内的FIFO作为缓冲器将高速采样数据存储,再由FPGA控制数据从FIFO中读出写入到NAND Flash 芯片中[7]。

3 系统软件设计

系统软件设计主要可分为FPGA控制W5100与上位机的传输和NAND Flash的存储两部分。在XILINX的ISE14.7的环境下用硬件表述语言VHDL完成程序的编写。

3.1 W5100 程序设计

通过设置W5100的寄存器和存储器,W5100就可以和上位机连接。W5100软件程序设计流程主要为W5100的复位、公共寄存器的初始化、端口寄存器初始化和W5100的读写[8]。本系统中采用UDP网络协议,本系统与上位机一对一连接,负荷小、数据的丢失的可能性小、端口不需要建立连接就可以进行数据传输,故其传输速率也比TCP模式高出许多。

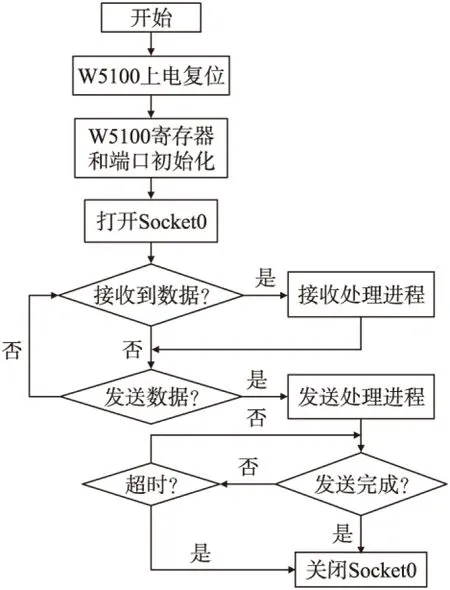

W5100工作流程如图4所示,系统上电后,首先进行W5100的复位,复位引脚低电平有效,低电平持续时间不小于2 μs。复位结束后系统对W5100公共寄存器和端口寄存器进行初始化[9]。在本系统中只选用Socket0进行通信,并分配8kbit的存储空间给Socket0,使W5100有足够大的接收和发送存储空间,避免因数据量太大而导致数据的覆盖和丢失。

图4 W5100工作流程图

采用ISE14.7的IP核中的单端口只读ROM来进行公共寄存器和端口寄存器的初始化配置,将公共寄存器和端口寄存器的地址和相应的初始化值生成coe文件,将该coe文件加载到FPGA自带的IP核搭建的ROM中,其配置过程如图5所示[10]。首先生成1个txt的文本文档,其文本内容首先定义数据的进制,memory_initialization_radix=16,即数据为16进制;另一部分是定义寄存器地址及寄存器的值,不同寄存器地址和值之间用逗号分离,将生成好的txt文本修改后缀名为coe文件,以后用记事本打开修改内容。之后在ISE软件中新建1个IP core核,深度为64,宽度为16,读取方式为只读,将建立的coe文件载入此核中,生成rom。最后编写VHDL程序读取IP核中的数据。对W5100的公共寄存器和端口寄存器的初始化过程就是FPGA将初始化后的ROM里的值读出来并写入到W5100中。

图5 ROM的初始化配置

表1中体现了W5100部分寄存器的地址和初始化值,图5中的Memory Values里的值要与W5100寄存器的地址和初始化值一一对应。

表1 W5100部分寄存器配置

W5100的读写过程要严格遵守W5100芯片手册中的时序要求,时序不对应可能会导致数据的丢失和出错[7]。由于FPGA无总线接口,W5100中 Add、CS#、WR#、RD#、Data等信号只能由FPGA的I/O引脚直接控制,因此必须在程序中采取模拟总线时序的方法。

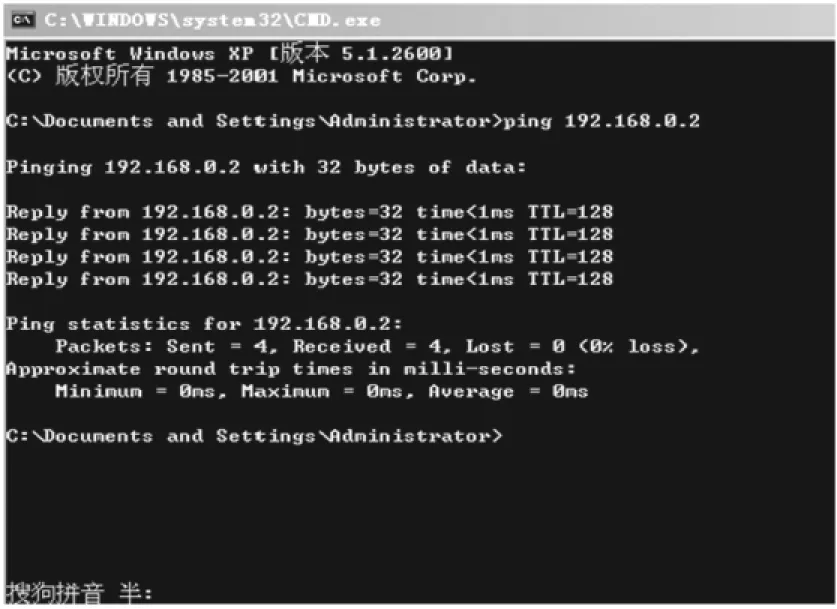

为验证W5100是否初始化成功,可以使用W5100 提供的自动Ping响应和处理的命令,若W5100初始化成功,就可以自动响应Ping请求。Windows系统中提供了DOS命令ping,通过ping可以检查,在Windows系统中点击“开始”、“运行”,输入命令ping 192.168.0.2,回车后,出现如图6所示的结果,证明W5100初始化成功,ping通了。

图6 使用ping命令检验W5100初始化成功

3.2 Flash程序设计

NAND Flash控制器完成的基本操作包括:坏块检测、Flash擦除、Flash写、Flash读[11]。为了避免数据读写过程受到坏块干扰,必须首先对FLASH进行坏块检测。对于固有坏块,利用FPGA对NAND Flash进行初始化,检查块标志4096列的值是否为FFH,当该块为非OxFF时,表明该块是坏块。获取坏块信息后,进行坏块统计并建立并更新坏块表;对于进行操作时随机产出新的坏块,当对NAND Flash 进行写操作或擦除操作时,可以根据状态寄存器判断 Flash 的运行是否成功,当状态寄存器接收到错误信息时,即认定此时正在使用的块是坏块,需要用好块进行替换,以保证数据的可靠性。

图7 Flash操作状态转换

FLASH操作流程图如图7所示,在每次上电之后,FPGA对NAND Flash发起访问时,通过坏块表控制访问地址实现坏块的屏蔽[12]。之后,执行写命令0x80,进入写状态,写相应的有效块地址,将FIFO中的数据写入,写命令0x10,等待R/B变为1,写数据完成;执行读命令0x00,进入读状态,写入要读数据的地址,写命令0x30,按照读时序将数据读出。每一次坏块判断成功后,其对应FIFO地址加一。

4 测试系统通信功能

运行网络调试助手,对网络进行初步的设置,协议类型设置为UDP,本地IP地址最终设置为192.168.10.106。本地端口号设置为5 000,如图8所示通过该网络调试助手向系统发送一组数据,系统成功将发送来的数据传送回上位机,表明系统通信正常。

图8 系统测试结果

5 结语

本系统采用FPGA控制W5100对数据进行传输和NAND Flash对数据进行备份。给出了W5100接口电路设计和NAND Flash接口电路设计和测试结果。本文的创新点是加入了数据备份,确保了数据的安全,使系统能广泛的应用于恶劣的环境。

[1] 祖静,申湘南,张文栋. 存储测试技术[J]. 测试技术学报,1994.8(2):25-31.

[2] 瞿鑫,吴云峰,李华栋,等. 基于FPGA的千兆以太网数据传输的设计与实现[J]. 电子器件,2014,37(4):662-664.

[3] WIZnet Co,W5100 Datasheet Ver.1.1.3,Wiznet Corporation[R]. Korea,WIZnet Co.,2006.

[4] 梁中英,苏涛,武荣伟,等. 基于FPGA和W5100的以太网通信系统设计[J]. 通信技术2010,11(43):95-97.

[5] 邹坤,石云波,焦佳伟,等. 基于以太网的加速度传感器数据采集传输系统设计[J]. 传感器与微系统,2015,34(12):66-68.

[6] Lasser M,Yair K. Flash Memory Management Method that is resistant to Data Corruptionby Power Loss:US 6,988,175 B2[P]. 2006:1-17.

[7] 王顺,戴瑜兴,段小康. 基于FPGA的NAND Flash控制接口电路设计[J]. 计算机科学与工程,2010.32(7).

[8] 陈实,王琪,张铁军,等. 一种基于W5100的数据传输系统[J]. 电子技术应用2010,29(12):54-60.

[9] 王炳义,刘爽,张伟,等. 基于硬件协议栈W5100的图像采集传输系统[J]. 电子技术应用,2009,35(3):92-96.

[10] 刘东华. Xilinx系列FPGA芯片IP核详解[M]. 北京:电子工业出版社,2013:301-308.

[11] Wang C,Wong W F. Extending the Lifetime of NAND Flash Memory by Salvaging Bad Blocks[C]//Proceedings of the Conference on Design,Automation and Test in Europe. EDA Consortium,2012:260-263.

[12] 舒文丽,吴云峰,赵启义,等. NAND Flash存储的坏块管理方法[J]. 电子器件,2011,34(5):580-583.

The Design of the Data Transfer System Based on W5100 and FPGA*

GUOChun1,2,LIJinming1,2*,ZHUPing1,2,ZHANGHuwei1,2,GAOWengang1,2

(1.National Key Laboratory for Electronic Measurement Technology,North University of China,Taiyuan 030051,China;2.Key Laboratory of Instrumentation Science and Dynamic Measurement of Ministry of Education,North University of China,Taiyuan 030051,China)

In order to improve the real-time and stability of the storage test system,and to take into account the large amount of data and the security of data storage,a new wireless data transmission system is designed. The system adopts Ethernet interface design method of FPGA+W5100 architecture,the peripheral circuit using NAND Flash memory for data backup method introduces the external memory address of the bad block on Flash bad block detection,and gives the realization method of system components,hardware connection and software. This system enhances the security of data storage and meets the requirements of data communication in the remote and complex environment.

data transfer;Ethernet;W5100;FPGA;NAND flash;bad block detection

项目来源:国家自然科学基金项目(61335008)

2015-10-27 修改日期:2016-04-19

C:6210

10.3969/j.issn.1005-9490.2017.02.022

TP393

A

1005-9490(2017)02-0370-05