一种新型低功耗电流模式CMOS带隙基准设计

2017-04-25吴婷茜

肖 丹,吴婷茜

(1.上海金融学院信息管理中心,上海 201209;2.上海金融学院实验教学与教育技术中心,上海 201209)

一种新型低功耗电流模式CMOS带隙基准设计

肖 丹1*,吴婷茜2

(1.上海金融学院信息管理中心,上海 201209;2.上海金融学院实验教学与教育技术中心,上海 201209)

为了降低传统带隙基准源的功耗和面积,提出了一种新型基于电流模式高阶曲率修正的带隙基准电压源电路。通过改进的电流模式曲率校正方法实现高阶温度补偿,并且通过集电极电流差生成绝对温度成正比PTAT(Proportional To Absolute Temperature)电流,因此所需电阻以及双极型晶体管BJT( Bipolar Junction Transistor)数量更少。采用标准0.35 μm CMOS技术对提出电路进行了具体实现。测量结果显示,温度在-40 ℃~130 ℃之间时,电路温度系数为6.85×10-6/℃,且能产生508.5 mV的基准电压。相比其他类似电路,当供电电源为3.3 V时,提出电路的整体静态电流消耗仅为9.8 μA,面积仅为0.09 mm2。

带隙基准;电流模式;曲率补偿;温度系数;低功耗

基准电压电路对于许多模拟、复合信号集成电路的精准运行都起着至关重要的作用,如AD转换器、功率管理器、调压器和存储器,因为这些电路为系统中的其他电路提供了一个稳定点。低压和低消耗是高性能电压基准电路最为关键的性能参数[1-2],并且要求对温度、进程和电源电压变化不敏感。

带隙基准BGR(Bandgap Reference)可在较低电压下运行,在本质上是带一阶(或高阶)温度补偿功能的正向偏压二极管基准。电路的工作原理基于两个电压的叠加,这两个电压有相反温度依赖关系,以产生温度稳定的基准电压。一般情况下,与双极型晶体管的基射极间电压(Vbe)相对应的正向偏压二极管电压,会随着温度变化线性减少。因此,在传统带隙基准中,不受温度影响的电压Vref的生成是通过适当调整的PTAT电压和与绝对温度互补CTAT(Complementary To Absolute Temperature)电压来实现的,即:

VREF=VCTAT+KVPTAT

(1)

式中:K为调整系数。

然而,典型的一阶带隙基准可以达到的准确程度受到VCTAT对温度依赖性的限制。并且对于很多系统来说,一阶带隙基准的精度是远远不够的。因此,出现了多种高阶补偿技术,通过温度补偿来进一步改善基准电压的温度稳定性,如指数温度补偿[3]、对温度非常敏感的电阻补偿[4]、分段线性曲率修正[5]以及匹配或精确的非线性补偿[6-7]。

在传统非线性补偿技术的基础上,本文提出的带隙基准电路以电流模式运行,并且利用改进的Tln(T)非线性电流来进一步补偿基准电压的温度变化。利用标准的0.35 μm CMOS技术进行了带隙电压基准设计。通过集电极电流差生成PTAT电流,而不是发射极面积差,并且所需电阻以及BJT数量更少,因此电路所占面积和功耗更小。温度在-40 ℃~130 ℃之间时,温度系数为6.85×10-6/℃。当供电电源为3.3 V时,功耗消耗仅为9.8 μA,且产生508.5 mV的基准电压。

1 电流模式带隙基准原理

电流模式带隙基准的基本理论包括生成不受温度影响的电流,这种电流被反射到输出电阻上来产生任意的输出电压。

图1对文献[9]中提到的CMOS电流模式带隙基准电压源进行了说明。基准电压是通过两个电流I1(Q1、Q2和R1形成的PTAT电流)和I2(Veb2和R2形成的电流)的求和产生。因此,VREF的产生方式如下:

(2)

一阶温度补偿是通过选择适当的R2/R1比和N来获取的。

图1 电流模式CMOS带隙基准原理图

对于传统的带隙基准,基准电压的结果值接近于硅的带隙电压(≈1.2V)。另一方面,对于电流模式带隙基准,基准电压可通过设置R1和R2的比值来按比例缩小,其值可小于1.2V。因此,Vref的数值可以根据不同的应用来进行调整。此外,需要注意的是,传统电流模式带隙基准的实现需要3个适当匹配的电阻,以便将输出基准电压的温度系数设置为零。

2 提出的电流模式带隙基准电压源

2.1 改进的曲率校正法

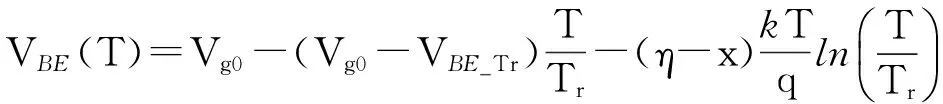

如前文所述,CTAT电压由二极管或基射电压生成。它有着不同的温度依赖性,如式(3)[10]所示:

(3)

这个公式中,在0 K,Vg0是推测的带隙电压,Tr是基准温度,VBE_Tr是基准温度时的基射电压,k是玻尔兹曼常数,η是对条件有依赖性,但是对温度无依赖性的变量(通常η≈3-4),x为集电极电流温度阶数(Tx)。

带隙基准的基本操作依赖于基射电压VBE的补偿线性和非线性温度依赖性组件。线性元件,即式(3)中第2项,是由PTAT电压补偿的。式(3)中Tln(T)这项表示VBE的非线性温度依赖性;因此,需要高阶的温度补偿来取消该项。

图2 改进的Tln(T)曲率校正法的简化原理图

为了对提出电流模式带隙基准电路进行高阶温度补偿,对原有的Tln(T)曲率校正方法[10-11]进行了改进,以便适用于本文提出电路。改进的Tln(T)曲率校正简化原理图,如图2所示。其中,非线性元件(即式(3)中第三项)利用两个双极型晶体管(Q1和Q2)的基射电压差异进行补偿,这两个双极型晶体管由不同温度依赖性的集电极电流驱动。为了简单起见,图中并未显示PTAT电流的生成。Q1由IPTAT驱动,而Q2由IPTAT和ICTAT共同驱动,其不受温度影响。因此,Q1和Q2的基射电压的公式如下:

(4)

(5)

Q1和Q2基极发射极电压之间的电压差会使电阻RNL产生非线性补偿电流INL,将其添加至IVBE可生成CTAT电流。可计算出RNL的固有值以便取消式(3)中的非线性项,如下所示:

(6)

IVBE=VBE/R1

(7)

(8)

RNL=R1/(η-1)

(9)

Tln(T)补偿之后,ICTAT电流可表示为:

(10)

2.2 提出电路的具体实现

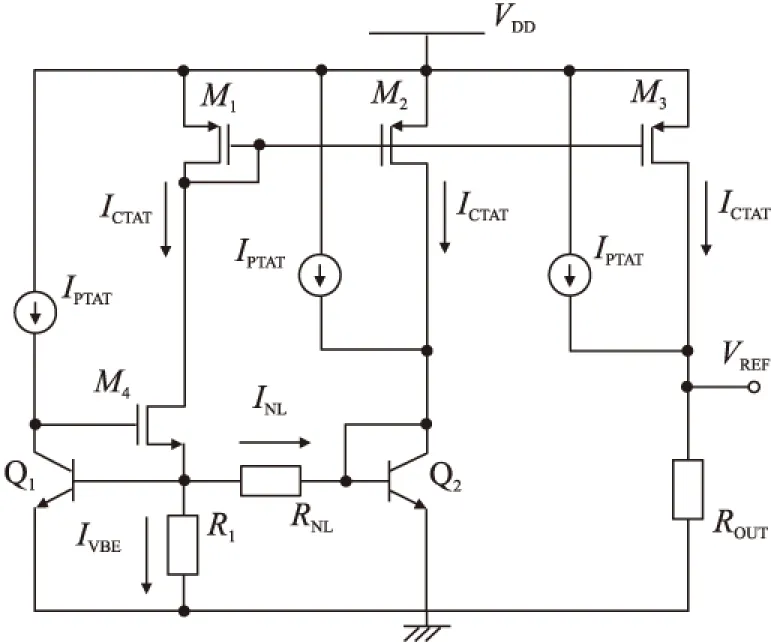

图3是本文提出的带隙基准电路原理图。

图3 本文提出的电流模式带隙基准电路原理图

该带隙基准电路会生成3种不同的电流。第1种电流是PTAT线性电流,是通过驱动两个大小相等的BJT(Q0,Q1)而生成,BJT(Q0,Q1)带有不同的集电极电流。此电流可表示为:

(11)

式中:N表示Q0和Q1的集电极电流之比,可通过调整PMOS晶体管(MP0,MP1)的纵横比获得。第2种和第3种电流是IVBE和INL,用于生成具有一阶温度依存性的CTAT电流,具体内容如上文所述。输出电流IOUT是CTAT电流与PTAT电流之和,表示如下:

(12)

为了消除CTAT电流的线性温度依存性,R1必须为:

(13)

最后,将式(13)代入式(12)得出:

IOUT=Vg0/R1

(14)

因此,输出电压可表示为:

(15)

在温度依存性分析中,为了简化分析,忽略了双极晶体管的基极电流。但是,除了IVBE和INL,CTAT电流同样也包括Q0和Q1的基极电流。

ICTAT=IVRE+INL+Ib0+Ib1

(16)

Q1的集电极电流是Q0的N倍,但是二者的发射极面积完全相同,所以,电流Ib1与Ib0之间的关系式为Ib1=N×Ib0。因此,式(16)可改写为:

ICTAT=IVRE+INL+(N+1)Ib0

(17)

为了补偿不需要的输出基极电流,利用基极电流补偿电路,从IOUT减去双极晶体管的基极电流。需注意,在子电路中,MOS晶体管在亚阈值区工作。

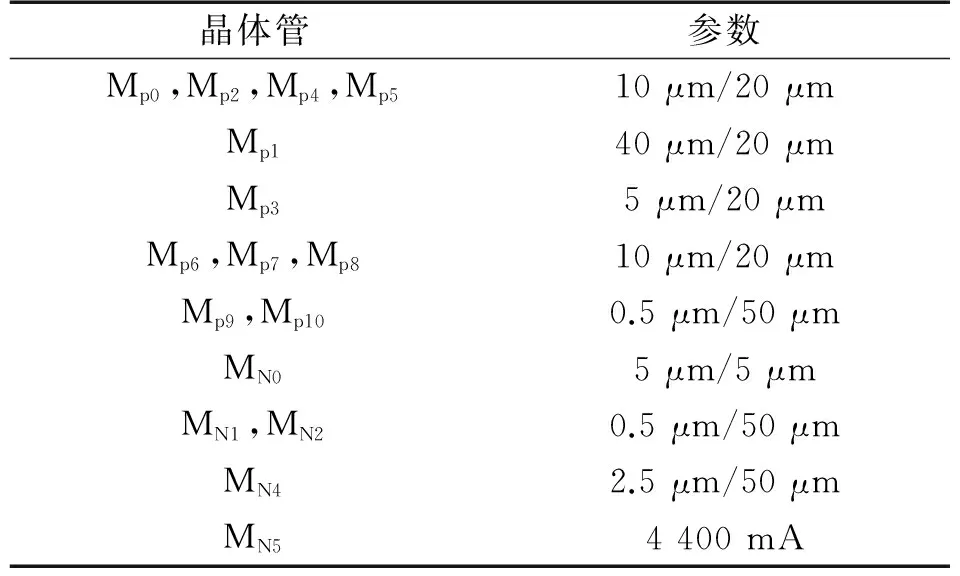

在实现本文提出的电路过程中,选择相同发射极面积的BJT以便与设备相匹配。BJT 中Q0和Q1的集电极电流镜像比为N=4。此外,由于可通过平均输出电阻ROUT将输出电压调节至任意水平,选择256 kΩ可获得0.5 V基准电压。表1是本文设计的曲率校正带隙基准的晶体管参数。

表1 本文提出的曲率校正带隙基准的晶体管参数

由MN1、MN2和MP3组成的反馈放大器,会迫使MP0和MP1的漏极电流达到适当的数值。尽管MN2减少了放大器的开环增益,但还是必须向Q0和Q1提供相似的运行条件。实现的反馈放大器信号增益较小,这与偏置电流无关。为了减少功率损耗,用于确定反馈放大器电流水平的比率m设为2,可减少放大器的偏置电流。将补偿电容器CC仅与反馈环路的高阻抗节点连接。

电路的最小电源电压可计算为|Vth,p|+|Vth,n|+3VDS,sat。在-40 ℃~130 ℃的温度范围内,0.35 μm CMOS工艺中MOS阈值电压(Vth,p和Vth,n)的最大值分别约为-0.9 V和0.6 V。通过选择约为100 mV的晶体管VDS,sat电压,本文设计的带隙基准可在电源电压降至1.8 V的情况下工作。

式(18)给出了本文提出的带隙基准的总电源电流。考虑到电流设计,R0为50 kΩ。

(18)

电源抑制PSR(Power Supply Rejection)的简化表达式为:

(19)

式中:VT表示热电压,λP表示P沟道金属氧化物半导体PMOS(P-Channel Metal Oxide Semiconductor)电流镜的通道长度调制参数。为了达到规定的功率损耗,将R0值固定。由预期的输出基准电压电平设置ROUT。因此,为提高电路的PSR性能,应降低通过长度调制参数λP。因此,可通过修改拓扑如使用共源共栅晶体管实现,或者通过将退化电阻添加至PMOS源端子实现,或者通过增加电流镜中PMOS晶体管的通道长度实现。

由于输出电压为零时电路有其他稳定的工作点,需要使用启动电路。该电路由电阻组成RS,x下拉电路由晶体管(MP0-MP5)组成。在稳定状态下,反馈放大器可调节其输入,所以,MP3漏极电流可达到预期水平。因此,启动电路无需额外功率。由于RS偷走了一部分MN1偏置电流,为确保所需的环路增益,启动电阻应足够大。通过补偿输出节点上双极晶体管的基极电流实现带隙基准的设计。

相较于现有的(常规)电路实现[4,6],本文提出的电流模式Tln(T)曲率校正带隙基准所占面积和功耗较小,原因在于所需电阻以及BJT数量更少,仅仅使用了一个R1,且通过集电极电流差生成PTAT电流,而不是发射极面积差。提出的电路仅需于2个匹配的电阻,并非3个电阻。

3 实测结果分析

本文设计的带隙基准电路是采用标准0.35 μm CMOS工艺制成。在测量中使用ESPEC BTZ-175E热处理室以便控制测试芯片的温度,使用安捷伦6705B获得了电路的电源,同时使用安捷伦3 458 A数字万用表测量了输出电压。通过安捷伦B1500A半导体参数分析仪测量了低频噪声,使用FSU-26频谱分析仪测量了PSR。通过NI Labview控制测量设备实现测量自动化。图4是提出芯片显微图。电路的有效面积为(350 μm×250 μm)0.09 mm2。

图4 本文提出的带隙基准芯片显微图

使用5个样品进行了实测。图5是根据温度得出未经调整的实测输出电压。电路生成了508.6 mV基准电压,并且标准偏差为4.67 mV。在-40 ℃~130 ℃的温度范围内,未经调整的温度系数平均值为20.36×10-6/℃,并且标准偏差为5.83×10-6/℃。

图5 根据温度得出未经调整的输出电压

图6 根据温度得出的实测与模拟输出电压

图6是R18-bit微调之后根据温度得出的实测输出电压。在-40 ℃~130 ℃的温度范围内,电路输出的平均值为508.5 mV,平均温度系数为6.85×10-6/℃。在相同的温度范围内获得了7.25×10-6/℃ TC。

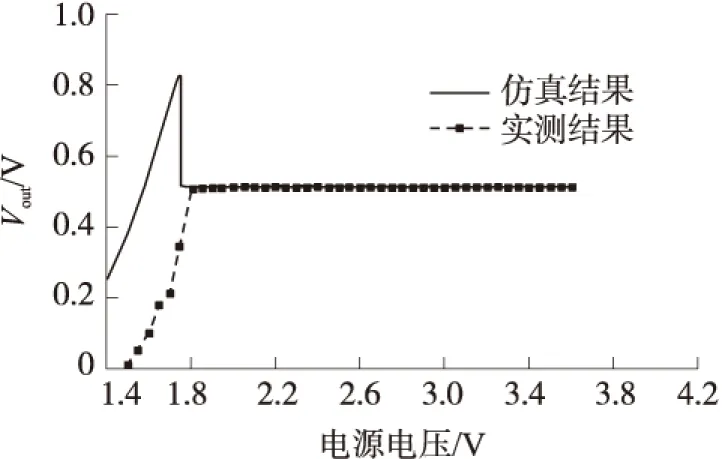

图7是关于电源电压的输出电压变化。当电源电压为1.8 V时,实测结果与模拟结果一致,证明电路的电源电压降至1.8 V,并且在室温下,电源电压(1.8 V~3.6 V)的线性调整率为781.2×10-6/V。由于反馈放大器与启动电路之间出现冲突,电源电压略低于1.8 V时输出电压增加。如果反馈放大器强度较大,则模拟结果中不会显示输出电压增加。

图7 根据电源电压得出的实测与模拟输出电压

因此,实测结果与模拟结果之间的差异归因于制造过程分布,相较于过程模型预测的反馈放大器,此反馈放大器的强度较大。在标称温度为25 ℃的条件下,当单电源的电压为3.3 V时,电路的实测静态功耗约为9.8 μA。

图8是本文所设BGR的PSR。当频率为100 Hz时,电路的PSR为-65.2 dB。从图8可看出,实测结果与模拟结果一致。测量数据的高低频率界线由测量设置确定。

图8 实测与仿真输出电压的PSR

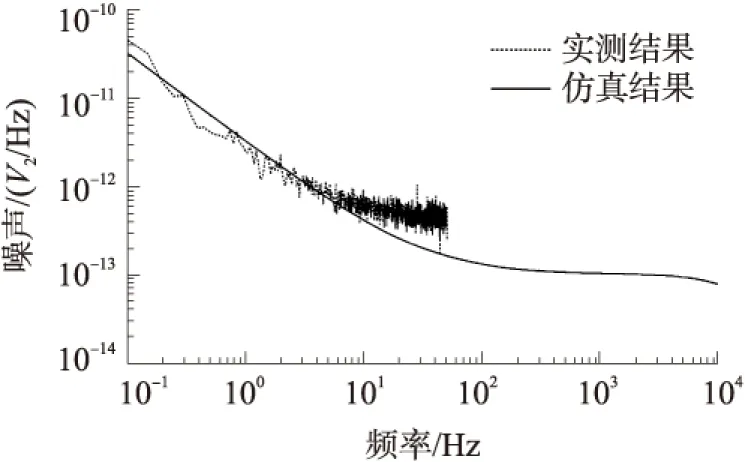

图9 实测与模拟输出电压的噪声功率频谱密度

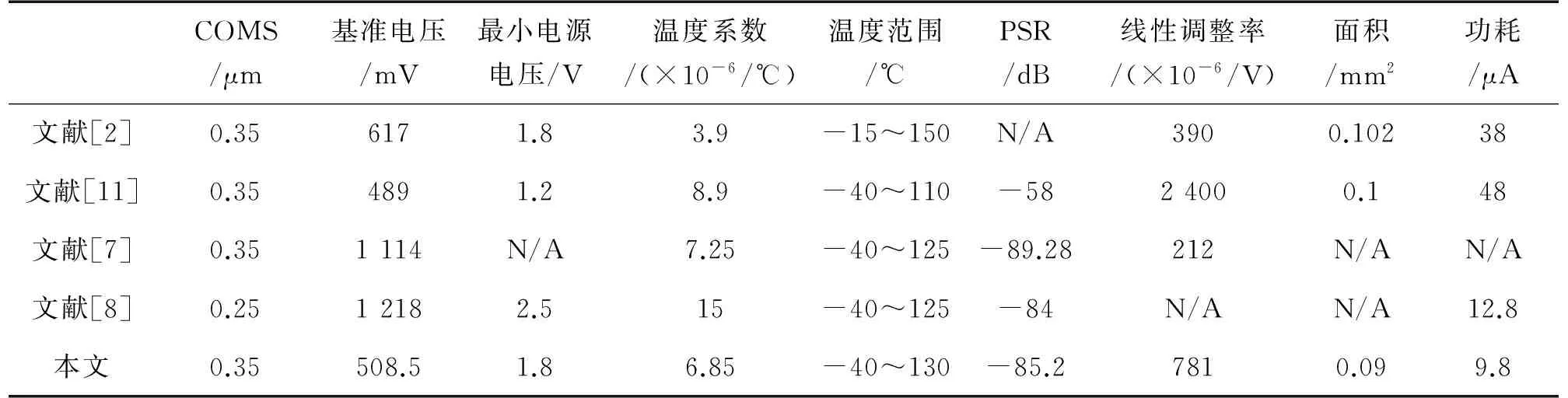

表2是本文设计的电路性能总结以及与公开文献描述的其他高阶补偿带隙基准电路的比较。从表2可以看出,相比现有的带隙基准,本文提出并实现的带隙基准具有较好的温度系数,最小的面积以及电源电流。

表2 曲率校正带隙基准电路的性能比较

4 结论

[1] 王红义,来新泉,李玉山,等. 采用二次曲线校正的CMOS带隙基准[J]. 电子器件,2007,30(4):1155-1158.

[2] Andreou C M,Koudounas S,Georgiou J. A Novel Wide-Temperature-Range,3.9×10-6/C CMOS Bandgap Reference Circuit[J]. Solid-State Circuits,IEEE Journal of,2012,47(2):574-581.

[3] Lee I,Kim G,Kim W. Exponential Curvature-Compensated BiCMOS Bandgap References[J]. IEEE Journal of Solid-State Circuits,1994,29(11):1396-1403.

[5] Rincon-Mora G,Allen P E. A 1.1-V Current-Mode and Piecewise-Linear Curvature-Corrected Bandgap Reference[J]. IEEE Journal of Solid-State Circuits,1998,33(10):1551-1554.

[6] Bowers D F,Modica E J. Curvature-Corrected Low-Noise Sub-Bandgap Reference in 28 nm CMOS Technology[J]. Electronics Letters,2014,50(5):396-398.

[7] 胡勇,彭晓宏,刘云康,等. 一种新型电流模式带隙基准源的设计[J]. 微电子学,2013,43(4):457-459.

[8] 唐宇,冯全源. 一种低温漂低功耗带隙基准的设计[J]. 电子元件与材料,2014,33(2):35-38.

[9] Banba H,Shiga H,Umezawa A,et al. A CMOS Bandgap Reference Circuit with Sub-1-V Operation[J]. IEEE Journal of Solid-State Circuits,1999,34(5):670-674.

[10] Malcovati P,Maloberti F,Fiocchi C,et al. Curvature-Compensated BiCMOS Bandgap with 1-V Supply Voltage[J]. IEEE Journal of Solid-State Circuits,2001,36(7):1076-1081.

[11] Li J H,Zhang X B,Yu M Y. A 1.2-V Piecewise Curvature-Corrected Bandgap Reference in 0.5 m CMOS Process[J]. IEEE Transactions on Very Large Scale Integration Systems,2011,19(6):1118-1122.

Design of a New Low Power Current Mode CMOS Bandgap Reference

XIAODan1*,WUTingxi2

(1.Center Department of Information,Shanghai Finance University,Shanghai 201209,China;2.Center for Experimental Teaching and Education Technology,Shanghai Finance University,Shanghai 201209,China)

In order to reduce the power consumption and area of the traditional bandgap reference,a new band gap reference voltage source circuit based on current mode high order curvature correction is proposed. Through the improvement of current mode curvature correction method high-order temperature compensation is realized,and the collector current difference generation absolute temperature is proportional to the PTAT current,therefore resistance and bipolar transistor(BJT)fewer. The implementation of the proposed circuit is realized by using standard 0.35 μm CMOS technology. The measurement results show that the temperature coefficient of the circuit is 6.85×10-6/℃,and the reference voltage is 508.5 mV in -40 ℃~130 ℃. Compared to other similar circuits,when the power supply is 3.3 V,the overall static current consumption of the circuit is only 9.8 μA,the area is only 0.09 mm2.

bandgap reference;current mode;curvature compensation;temperature coefficient;low powe

2016-03-08 修改日期:2016-07-25

C:2570D

10.3969/j.issn.1005-9490.2017.02.005

TN433

A

1005-9490(2017)02-0285-06