ARM+FPGA的双模导航接收机硬件平台设计

2017-04-25刘宁马洪涛王晓君

刘宁,马洪涛,王晓君

(河北科技大学 信息科学与工程学院,石家庄 050000)

ARM+FPGA的双模导航接收机硬件平台设计

刘宁,马洪涛,王晓君

(河北科技大学 信息科学与工程学院,石家庄 050000)

卫星导航系统能够为广大用户提供全天时、全天候、高精度的导航、定位和授时服务。本文介绍一种基于ARM+FPGA架构的GPS/BDS双模导航接收机的设计方法。该设计分为3部分:射频部分电路设计、FPGA部分电路设计和ARM电路设计。其中,射频部分主要完成GPS/L1频点、BD2/B1以及B3频点卫星信号的下变频及采样。FPGA部分做信号处理,ARM负责信息处理。经过测试,此设计是可行的,能够达到导航接收机对于定位和授时精度的要求。

导航接收机;ARM;FPGA;信号

引 言

卫星导航系统现已发展为人类活动和促进社会发展的重要基础设施。目前,世界上正在运行的有美国的GPS系统、俄罗斯的GLONASS系统、我国的北斗导航系统[1]。

虽然说,卫星导航系统能提供全球、全天候、连续和高精度的服务,但是,由于信号容易受到外界干扰以及由遮蔽引起的卫星信号中断,从而使得导航接收机在某时、某地不能完成定位功能。从中国方面看,GPS和BD2间的相互融合成为发展趋势,双星座兼容机在定位的可靠性、准确性方面将大大提高。目前,国内已经出现很多双模导航接收机,但大多数是DSP+FPGA架构的导航接收机,外围接口比较单一,标准化和通用性做的不好,而且功耗较大[2]。而本课题研制的ARM+FPGA架构的导航接收机,在满足性能的同时,还具有较低的成本和功耗,可以移植操作系统,支持现有DSP和FPGA接收机的程序移植,还具有强大的网络功能,功能更强大,能够应用于各个领域。因此在市场上该接收机将有更强的竞争力。

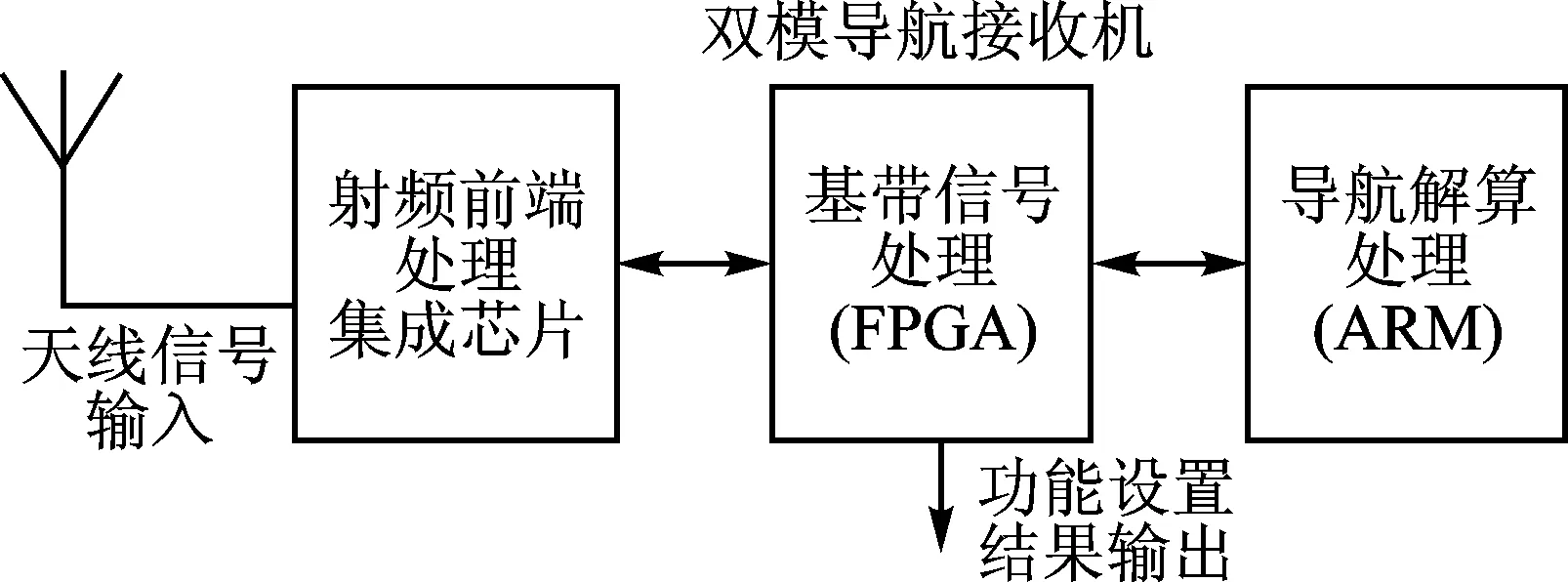

1 基于ARM+FPGA的双模导航接收机硬件平台设计方案

该导航接收机需要完成双卫星系统3频点的组合定位、导航和授时服务,基于这样的特点,射频前端采用集成度高、成本低、体积小且功耗低的专用集成芯片来对接收到的卫星信号进行下变频、滤波、采样、A/D变换输出数字中频信号[3]。在基带信号处理部分来复制出与接收到的卫星信号相一致的载波和伪码信号,需要完成大量并行的实时运算,需要多个信号通道,因此本设计中选用了FPGA来实现对卫星信号的捕获跟踪,并且从中获得测量值以及导航电文[4]。在导航解算部分需要在短时间内处理大量的数据,进行各种复杂运算来解算出用户的位置、速度和时间等信息,且还要兼顾功耗、成本以及功能扩展性[5]。经上述分析,该设计选用了ARM芯片来实现,最后将解算结果输出到上位机。该导航接收机的总体结构图如图1所示。

图1 双模导航接收机总体结构框图

2 单元电路设计

该接收机硬件电路主要包括射频前端、基带信号处理模块、导航解算处理以及GPMC接口电路的设计。

2.1 射频前端设计

此导航接收机需要接收双卫星系统3频点的卫星信号,为了适应它的多频点要求,且把一路输入的卫星中频信号能量分成3路相等的能量输出,选用了功分器芯片SCA-4-20+。从功分器出来的3路信号每一路信号都需要经过一个声表面滤波器,利用不同频带滤波器的选频特性,选用的滤波器为TA0967A和TA08,可以把BD2的B1/B3频点和GPS的L1频点的卫星信号过滤出来,分别输出给3块射频芯片。

根据设计要求,选用的射频信号处理芯片为SFM953DEQ,该芯片可以接收BD2的B1/B3、GPS/L1这3个频点的卫星信号,并且可以按照不同卫星系统信号的特点,通过接口进行设置,设定不同的带宽和晶振频率,对这3个频点的信号进行下变频、滤波、中频采样处理。射频前端的功能框图如图2所示。

图2 射频前端功能框图

2.2 基带信号处理模块设计

本设计中选用了Virtex-5系列的FPGA为基带信号处理部分的主控芯片。这款芯片有丰富的I/O资源,还有6个PLL时钟发生器的增强型时钟管理模块,核心频率可以达到几百兆,完全满足各通信接口的时钟要求。

基带信号处理模块主要包括FPGA、JTAG接口、Flash、复位接口以及时钟电路等[6],其硬件结构框图如图3所示。FPGA选用的是Virtex-5系列的XC5VLX155_FFG1153,根据芯片型号和设计要求选用了Flash芯片,型号为XCF128XFTG64C,内部存储空间有128 M B。该芯片不仅具备电子可擦除可编程的性能,还具有非常先进的写保护机制。

图3 基带信号处理模块硬件框图

2.3 导航解算处理模块设计

本设计中导航解算处理部分的主控芯片选用的是ARM A8系列的AM3354。它的主频最高可以达到1 GHz,自身运算速度较快,精度较高,自带通用存储器控制器GPMC和外部存储器接口EMIF,可与FPGA、SDRAM等实现无缝连接[7],该设计中使用了具有更高运行效能和更低电压的存储器DDR3,它还具有更高的外部数据传输率。该芯片还支持Linux, Android和高级操作系统HLOS,同时自身还带有多达2个网口、串口、音频串行端口、LCD控制器等,大大满足了用户对接收机的功能扩展。

导航解算处理模块硬件电路主要包括时钟电路、调试使用的JTAG接口、存储DDR3接口、复位以及LCD显示屏接口电路等。其硬件电路结构框图如图4所示。

图4 导航解算处理模块硬件框图

2.4 GPMC接口电路设计

AM3354自带的GPMC是一个内存控制器,可支持异步或同步8位、16位存储器或者闪存设备,而存储器或闪存设备的类型决定了GPMC的控制信号。本设计中利用FPGA来代替外部存储器,模拟GPMC总线的读写时序,在读时序中,FPGA采集的高速信号在寄存器中存储完成后,给ARM发出中断请求信号,ARM进行读取操作,从而使CPU的效率大大提高,因此本设计利用GPMC总线作为FPGA与ARM的接口来完成高速数据的传输。

3 测试结果

本硬件平台制作出来后,为验证本设计的正确性,将平台上电后进行测试,为了防止因电压过高而烧毁芯片,在芯片焊接前先用万用表对芯片电路所供电压情况进行测试,然后焊接芯片写测试程序对Flash、DDR、I/O、串口、总线接口等硬件电路进行测试。验证结果显示电压正常,电路的各个部分工作正常,通信正常。

结 语

本文提出了一种双模导航接收机的设计方案,并根据此方案设计了接收机的硬件平台,编写了硬件驱动程序,测试程序、把DSP+FPGA导航接收机程序移植到该平台,完成了捕获跟踪以及定位解算[8]。经多次测试,该接收机工作稳定、精度较高、功耗较低,且通过串口与上位机软件相结合,能明显直观地为用户提供精确的位置和时间服务。本文设计的双模导航接收机在实现定位、测速、授时的同时,还具有体积低、成本低,扩展性、通用性超强等特点、可被应用于导航相关的各个领域。

[1] 武虎子,南英,付莹珍.国内外卫星导航技术发展综述[J].现代防御技术,2008,36(5):46-51.

[2] 唐斌,刘富,张益青.GNSS接收机发展趋势与研究思路分析[J].导航天地,2011(s1):82-84.

[3] 张北南.基于ARM的三模导航接收机基带技术研究与实现[D].北京:北方工业大学,2014.

[4] 谢钢. GPS 原理与接收机设计[M]. 北京:电子工业出版社,2009.

[5] 薛涛,赵伟,李荣冰,等.北斗导航接收机的硬件设计与实现[J].航天控制,2015,33(1):94-98.

[6] 刘竞超,邓中亮.基于ARM+FPGA北斗接收机设计[J].软件,2012,33(12):38-40.

[7] 时东飞.基于FPGA及ARM核的GPS信号处理平台的设计及实现[D].上海:上海交通大学,2012.

[8] Akopian D.Fast FFT based GPS Satellite Acquisition Methods[J].IEEE Proceedings on Radar,Sonar & Navigation,2005,152(4):277-286.

刘宁(在读研究生)、王晓君(教授),主要研究方向为卫星应用技术;马洪涛(副教授),主要研究方向智能化仪器仪表、电力电子技术。

Hardware Platform Design of Dual-mode Navigation Receiver Based on ARM+FPGA

Liu Ning,Ma Hongtao,Wang Xiaojun

(Hebei University of Science&Technology,Shijiazhuang,050000,China)

The satellite navigation system is able to provide the broad masses of users throughout the day,all-weather,high precision of the navigation,positioning and timing services.In the paper,a design scheme and implementation of GPS/BDS dual-mode navigation receiver based on ARM+FPGA is introduced.The design is divided into three parts,such as the radio frequency circuit design,FPGA and ARM circuit design.The satellite signal of GPS L1 and BD2 B1 and B3 frequency point is amplified,down-converted and sampled by the radio frequency circuit.The signal is processed by the FPGA and the information is processed by ARM.The experiment results show that the design is feasible,and it can meet the accuracy requirement of the navigation receiver for positioning and timing.

navigation receiver;ARM;FPGA;signal

TN965.5

A

迪娜

2016-11-14)