基于FPGA和DDS的频率步进信号源的设计与实现

2017-04-25许文浩屈乐乐殷文浩

许文浩+屈乐乐+殷文浩

摘要:本文基于FPGA和DDS技术设计实现了一种频率步进信号源系统。系统是通过编写硬件描述语言Verilog,以QuartusⅡ软件为工具以FPGA为载体完成对DDS在波形频率、跳跃间隔、起始频率、终止频率等方面的控制和调节。该系统可以产生10-50MHz的频率步进信号,步进频率可调节,输出的信号具有频谱纯度高、频率分辨率高和频率转换速度快等优点,该系统可以广泛应用于通信、雷达等领域。

关键词:FPGA;DDS;频率步进信号源

中图分类号:TN74 文献标识码:A 文章编号:1007-9416(2017)01-0147-01

1 引言

随着数字信号理论和超大规模集成电路的发展,在频率合成领域出现直接数字频率合成(DDS)技術,DDS技术是一种全数字化的波形发生技术,其频率分辨率高、调频时间短、频率稳定度高。目前的专用集成DDS芯片频率单片可达1GHz,在各种信号源系统中得到了广泛的应用。

现场可编程门阵列(FPGA)是近年来发展迅速的大规模、高密度的可编程逻辑器件。FPGA具有高度的灵活性,长生命周期性,可反复编程修改等特点,从而使其在通信、数据处理、网络、工业控制、军事和航空航天领域中得到迅速普及和广泛应用。

2 基本原理

利用FPGA完成对DDS芯片的时序配置和工作控制,通过DDS芯片AD9854实现对步进信号源的设计,利用LCD1602直接显示出调制波形的工作参数信息。

2.1 基于DDS芯片AD9854的介绍

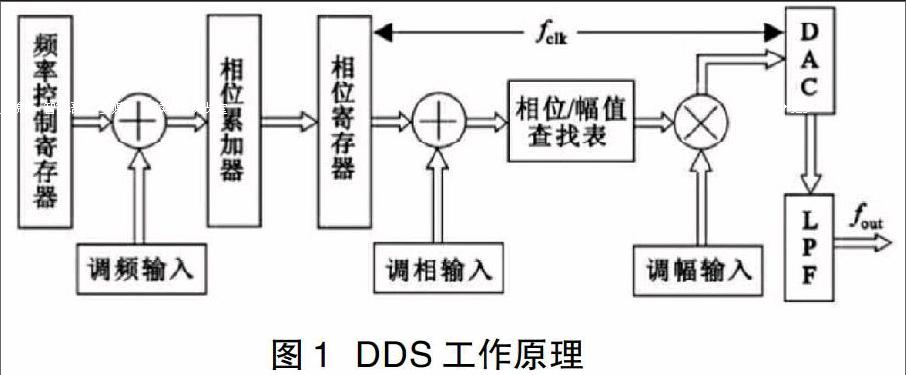

AD9854数字合成器是CMOS型DDS单片集成电路,采用了先进的DDS技术,该芯片具有极高的工作频率、方便灵活的外部接口、多种信号输出形式等特点。AD9854的结构如图1所示。它的主要原理为:片内整合了两路高速、高性能的正交D/A转换器和高速比较器,可以实现数字合成的正交I路和Q路输出。在高稳定度时钟的驱动下,AD9854将产生一个高稳定的频率、相位、幅度可编程的正弦和余弦信号,作为振荡器用于通信、雷达等领域。

2.2 频率参数计算

当时钟信号f到来时,相位累加器对频率控制字FTW进行线性累加,从累加得到的相位码中取n位有效位对波形存储器进行寻址,输出相应的幅度码,再经过DAC得到阶梯波,最后通过低通滤波器LPF得到所需的连续变化的信号波形。系统时钟频率f、输出信号频率F和频率控制字 FTW的关系为

FTW=F*2N/f

式中: FTW(频率控制字)是一个定义数字,N为相位累加器的资源。

3 基本构成

DDS扩展模块板主要由一片2路模拟输出的AD9854DDS芯片,以及两片AD8009高速运算放大器组成,可以满足对于高速信号产生的要求,借助FPGA核心模块板,通过模式控制和频率字控制实时产生点频、扫频、ASK、FSK等各种形式的模拟信号信号。

4 性能测试

对整个10-50MHz工作带宽内进行多个频点的输出测试,结果如图2所示。

5 结语

基于FPGA和DDS芯片AD9854能够灵活方便地实现步进信号源的设计与实现,并在10-50MHz频率范围内实现任何的单频输出和扫频输出信号。