基于FPGA数字频率计的设计

2017-04-18雷能芳

摘要:介绍了一种以FPGA作为核心器件,以Verilog作为描述语言的数字频率计测量方法,并通过Quartus II软件对编写的代码进行了时序仿真,验证了设计的正确性。

关键词:频率计;FPGA;Verilog HDL

中图分类号:TN713 文献识别码:A 文章编号:1001-828X(2016)033-000-01

随着电子技术的发展,频率的测量已经成为非常热门的话题,应用范围也随之更加广泛。大多数的数字频率计都习惯采用单片机来实现,但是单片机本身也存在很多不足:时钟频率有限;PCB版的集成度不高。因此单片机很难使频率计的工作频率得到提高。为此,采用可编程逻辑器件来实现数字频率计的设计,使其得到改善。

本设计主要包含两大功能:脉冲信号频率测量及占空比测量。

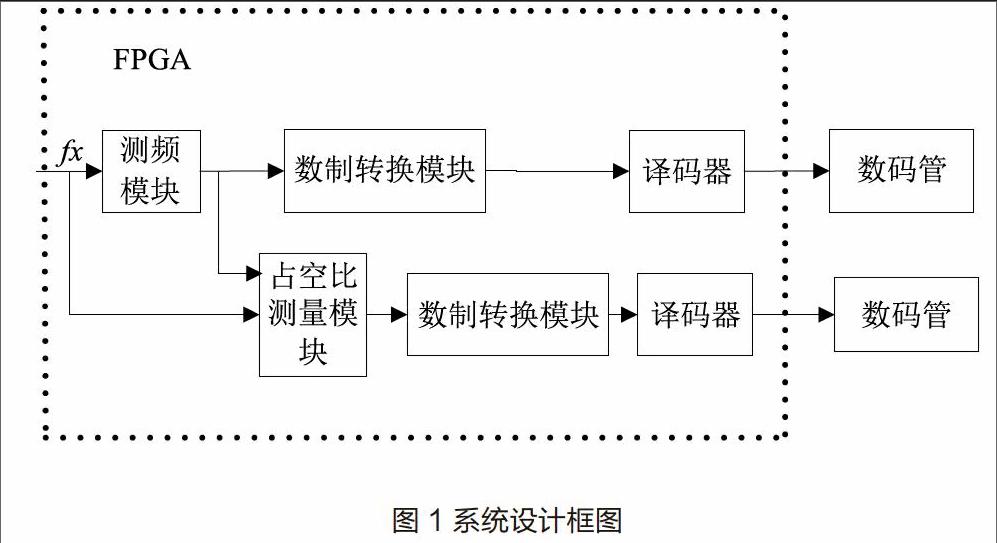

一、系统总体设计

图1 系统设计框图

系統总体设计框图如图1所示。首先将待测脉冲信号fx分别通过测频模块和占空比测量模块进行频率及占空比的测量;然后将测出的频率值与占空比值经过数制转换模块将二进制数转换为BCD码,最后再通过数码管将测量结果直观地显示出来。

二、测量原理

1.频率测量原理

主要思路是:在1s的闸门时间内,统计出待测信号的上升沿个数。由公式(1)则可计算出被测信号的频率。

(1)

式中N是指闸门信号内对被测信号的计数值,T为闸门时间。

频率测量原理波形图如图2所示。闸门信号en主要用于对计数器的工作状态进行控制。当闸门信号为高电平时,在待测信号的上升沿到来时,计数器开始对脉冲信号的上升沿进行计数;而当闸门信号为低电平时,计数器停止计数,则1s的闸门时间内计数器的计数值即为被测信号的频率[1]。

图2频率测量原理波形图

2.占空比测量原理

占空比是指在一个脉冲周期中高电平所占的百分比。本设计采用的测量方法是间接测量法,即测出脉冲周期和脉冲信号的高电平持续时间T1。根据脉冲占空比的定义可以得出:

(2)

由式(2)可知,要测出脉冲信号占空比,必须测出T1。以1MHz信号为计数的频率基准,当待测信号为高电平时进行计数,即可测出T1。

三、基于FPGA的频率及占空比测量模块设计

以FPGA作为核心器件,采用Verilog HDL对脉冲信号频率及占空比测量模块进行了逻辑设计,并通过Quartus II软件对编写的代码进行了时序仿真[2-3],仿真波形图如图3所示。

图3 频率及占空比测量模块仿真波形图

图3中,clk为系统时钟信号,被测信号fx的频率设置为25Hz,占空比设置为50%。n为被测信号频率测量值;D为被测信号占空比测量值。仿真结果与设定值一致,验证了设计的正确性。

参考文献:

[1]王振红.基于VHDL语言的数字频率计的设计[J].北方工业大学,2006,32(03):234-237.

[2]梁淼,刘会军.数字系统电子自动化设计教程[M].北京:北京理工大学出版社,2008:1-59.

[3]王金明.Verilog HDL程序设计教程[M].北京:人民邮电出版社,2004:10-30.

作者简介:雷能芳(1973-),女,陕西澄城人,讲师,主要从事电路系统设计自动化,数据采集与传输研究。