基于FPGA的RS232接口设计与实现

2017-04-13丁超

丁超

【摘要】 RS232是一种常用的异步的串行通讯接口,本文介绍了基于FPGA的RS232接口设计与实现过程,利用FPGA完成全双工串口通信,波特率可任意设置,接口挂载数量多,并能实现多通道同步处理,设计方式灵活,通用性较强。

【关键字】 FPGA RS232接口 串口通信 帧数据解析

一、前言

RS232作为低速短距离通信的串行接口,常用于配合上位机通信。传统单片机实现的RS232串口通信,波特率设置固定,接口挂载数量有限,接口速度较慢等诸多缺点,并且单片机的并行操作,难以实现RS232的全双工功能。为此,本文介绍基于FPGA的RS232接口设计与实现,弥补了单片机在RS232通信中的不足。

二、接口电平转换的设计

使用9针RS232通信接口实际使用时,利用TXD(发送数据)、RXD (接收数据)、GND(地线)三线便能实现串口通信。RS232规定的逻辑电平与一般处理器的逻辑电平不同,在TXD、RXD中,邏辑1电压为-3~-15V,逻辑0电压为+3~+15V。因此要想与PC的232接口通信,需要专门的电平转换芯片将RS232电平转换为TTL电平。我们使用专门的MAX232电频转换芯片可实现电平的转换,保证处理机与PC通信的正常进行。接口传输线缆少,电路设计相对简单。如图2-1所示:

三、逻辑设计

利用FPGA设计RS232接口通信,设计灵活性较大。在FPGA中,接口的通信可同时进行,互不干扰。因此可实现全双工的串口通信。数据的发送与接收可使用独自的波特率,并且波特率可任意设置,保证数据的正确接收与发送。

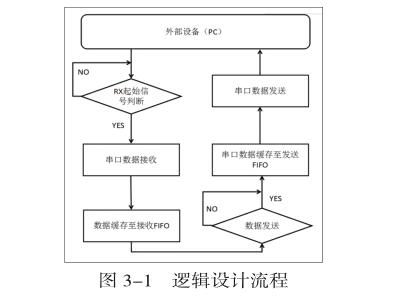

例如在与PC进行数据交互时,我们规定接收来自PC的数据波特率为115200bps,发送速率为9600bps,数据收发同时进行。在单片机中指令顺利执行,速度也相对较慢,要实现这样一组RS232接口通信较为困难。在FPGA设计中,接口的数据收发可同步进行,RXD,TXD映射到底层的收、发子模块,子模块的操作只受敏感信号主时钟CLK与复位信号的影响,实现收、发同步的同时,每个子模块中波特率可设置为任意波特率,波特率由FPGA描述各自模块内部的计数器,计数到标志位产生波特率时钟,因此可独立将接收波特率设置为115200bps,将发送波特率设置为9600bps。FPGA实现数据收发的逻辑描述如图3-1所示:

当FPGA的RX引脚检测到外部信号发送时,RX电平拉低,进入起始位,FPGA内部接收子模块中,已设置好接收波特率设置,在移位操作后,将8位数据信息解析出来。由于数据流要进行发送处理,并且接收速度大于发送速度,这便会出现数据丢失的可能。因此在接收子模块中将数据缓存如FIFO中作为数据保留,待需要发送时,将数据发送至发送子模块的缓存区域(FIFO),准备好发送状态,数据发送时,由起始位、数据位8位、校验位(可删)、停止位重组 发送至PC端。设计中,接收,发送端保留自身的速度特性,互不影响,实现RS232的全双工通信。FIFO作为数据缓存使用,防止数据流失的可能,确保了数据流收发的正确性。

总结:基于FPGA的RS232接口设计,尽管在成本上高与单片机,但在功能需求较高的接口通信设计中,仍具它独特优势。较之单片机功能固定、资源有限、串行数据处理的缺点,利用FPGA实现RS232接口通信,设计更为灵活,可挂载多组RS232接口实现并行通信,波特率可任意设置,可实现收、发同步进行,内部FIFO数据缓存避免了数据流失。基于FPGA的RS232接口设计具有良好的应用价值。

参 考 文 献

[1]赵志军, 王建英. RS232/CAN智能协议转换器及其通信网络[J]. 中国铁道科学, 2007, 28(3):134-139.

[2]吴兴中, 欧青立. 一种PC与单片机多机RS232串口通信设计[J]. 国外电子测量技术, 2009, 28(1):74-76.

[3]张雄飞, 方方. Windows平台下数据采集串口通讯的实现[J]. 计算机测量与控制, 2001, 9(3):66-68.

[4]戴鹏, 刘剑, 符晓,等. 基于TMS320F2812与LabVIEW的串口通信[J]. 计算机工程, 2009, 35(4):94-96.

[5]陈廷侠, 赵红枝. MAX232在串口通信中的作用分析与测试[J]. 新乡学院学报, 2009, 26(4):19-21.