一种实现ADC采样数据回路自检的方法

2017-03-31叶品勇陈新之岳峰

叶品勇,陈新之,岳峰

(南京国电南自自动化有限公司,南京 211100)

一种实现ADC采样数据回路自检的方法

叶品勇,陈新之,岳峰

(南京国电南自自动化有限公司,南京 211100)

ADC采样数据作为电力系统二次保护装置数据的重要来源,是保护装置动作行为的重要判断依据。然而目前市场上主流的多通道同步ADC芯片不具备采样数据校验功能,芯片焊接问题导致的采样数据异常无法及时发现,而这将可能导致保护装置误动作,造成严重的电力事故。本文提出了一种ADC采样数据回路自检的实现方法,通过外部自检回路回馈的方式巧妙的配合ADC芯片采样时序来检查ADC芯片是否存在焊接问题,从而判断ADC采样数据回路是否连接正常。该方法实时性高,可有效降低因ADC采样数据异常而导致保护装置错误的动作行为而产生的恶劣影响和经济损失。

ADC芯片;数据回路;采样时序;自检

引 言

在电力系统二次保护装置中ADC采样数据是装置数据的重要来源,是保护装置动作行为的重要判断依据。在电力系统二次保护装置中通常采用多通道同步ADC采样,这是因为电力系统二次保护装置需要采集的电压、电流信号量较多,且必须保证同步相位关系[1-7]。然而目前市场上主流的多通道同步ADC芯片,如TI公司的ADS8555、ADS8556,ADI公司的AD7656、AD7606,无论采用并行数据传输还是串行数据传输都没有采样数据校验功能[8-12],因此当焊接问题而导致的采样数据异常是无法及时发现的,而这将导致保护装置误动作,造成严重的电力事故。曾有厂家生产的500 kV线路保护装置因没有采样数据自检功能,当采样数据回路异常时采样数据冒大点而导致了误跳闸,造成的影响是极其恶劣的。

随着IC制造工艺的发展,ADC芯片集成度越来越高,封装尺寸和引脚间距也越来越小,在焊接过程中比较容易发生连焊、虚焊问题。产品在投运过程中因受外部环境影响(如氧化、腐蚀、污染等)也会出现芯片引脚连焊、虚焊问题。而传统的焊接质量检测方法,如肉眼观察加万用表进行焊接质量检测,由于观察点较多,而且小而密集,不易观察,如果是BGA或QFN封装的芯片,肉眼是观察不到焊接点的,达不到检测的目的。X-Ray观察适合连焊检查,但虚焊或缺焊不容易检查出来,而且X-Ray设备对人体还有一定伤害。飞针测试仪检测需要编写测试程序及测试文件,复杂度高,设备成本高。并且这些检测手段只能适用于生产测试中,在产品整个生命周期中因受外部环境影响(如氧化、腐蚀、污染等)出现的芯片引脚焊接问题就无能为力了[13-15]。

因此,本文提出了一种用于ADC采样数据回路自检的实现方法,它通过外部自检回馈电路巧妙地配合ADC芯片采样时序来实时检测ADC采样数据回路连接状态。

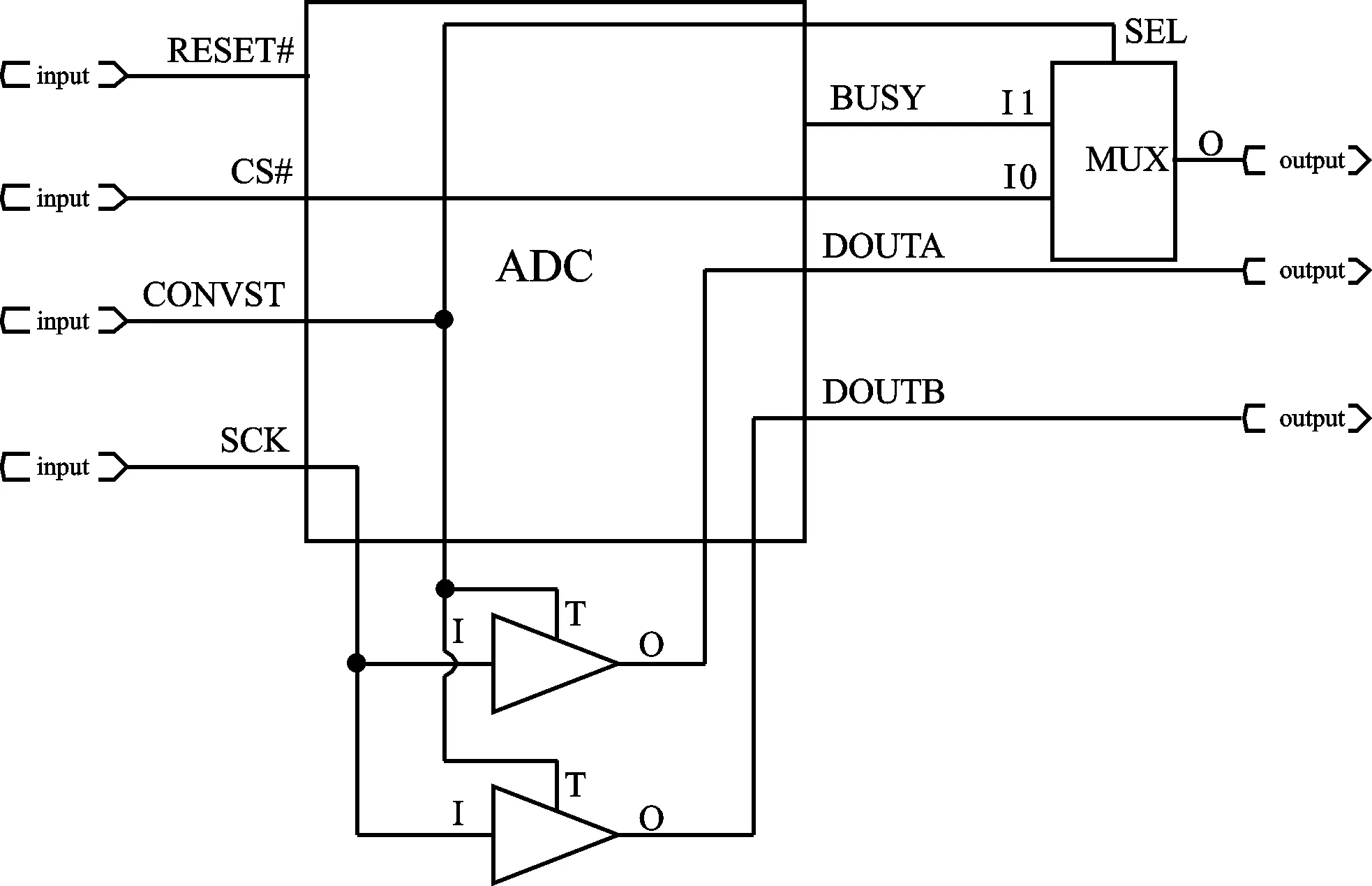

1 自检回路

首先通过在ADC芯片(以AD7606串行数据传输为例)关键引脚外部增加三态缓冲器和多路复用器来实现如图1所示三态缓冲器和多路复用器真值表见表1、表2。通过在不同回路施加自检信号,然后比较输入和输出自检信号状态,配合ADC采样时序,可以检查出回路之间是否存在短接问题,防止连焊。

图1 ADC采样数据自检回路示意图

表1 三态缓冲器真值表TO0Z(高阻)1I表2 多路复用器真值表SELO0I01I1

在制作ADC芯片封装的时候,CS#、CONVST、SCK及DOUTA(B)引脚焊盘要做成主-副焊盘的形式,如图2所示。主-副焊盘通过芯片引脚桥接到一起,只有当芯片引脚与主-副焊盘可靠焊接后回路才能导通,由此可通过回路是否导通判断芯片焊接是否可靠,防止虚焊。

图2 主-副焊盘示意图

2 自检时序

ADC采样数据回路自检需要配合ADC采样时序完成,如图3所示。图中RESET#、CONVST、BUSY_ADC、CS#、SCK和DOUTA(B)_ADC表示ADC芯片引脚上的信号,BUSY_OUTPUT、DOUTA(B)_OUTPUT为连接到主控芯片上的信号。图中上半部分表示原始ADC芯片采样时序,图中下半部分表示带自检功能的ADC芯片采样时序。

图3 ADC采样数据回路自检时序图

RESET#:ADC复位信号,由主控芯片输出低电平复位ADC芯片。通常只在上电后复位一次即可。

CONVST:ADC启动采样信号,由主控芯片输出高电平通知ADC芯片对其输入的模拟量信号进行采样转换。

BUSY_ADC:ADC忙信号,其为ADC芯片的输出信号,表示当前ADC正在对模拟量信号进行采样转换中。

CS#:ADC片选信号,低电平有效,由主控芯片输出低电平选通该ADC芯片,从而可进行数据读取操作。

SCK:ADC串行数据接口时钟信号,由主控芯片输出周期信号进行数据读取操作。

DOUTA(B)_ADC:ADC串行数据接口数据信号,可配置为单线或多线模式,由ADC芯片在SCK时钟边沿触发下输出采样数据。当CS#片选为高电平时输出为高阻态,当CS#片选为低电平时输出数据。

DOUTA(B)_OUTPUT:ADC串行数据接口引脚与三态缓冲器引脚共同连接到主控芯片的同一线网信号。它反映的是ADC串行数据接口DOUTA(B)_ADC输出和三态缓冲器输出的公共信号。

BUSY_OUTPUT:多路复用器连接到主控芯片的线网信号。不同的时刻可以表征ADC芯片的BUSY信号和CS#信号。

当ADC上电复位完成后,进入一个采样周期的A阶段,CONVST由主控芯片驱动为高电平,CS#维持在高电平。ADC开始对模拟量信号进行采样转换,BUSY_ADC由ADC芯片输出高电平。多路复用器SEL引脚为高电平,I1被选通,BUSY_OUTPUT呈现BUSY_ADC信号,也输出高电平。三态缓冲器被使能,主控芯片在SCK上面输出一组脉冲自检信号,此时DOUTA(B)_ADC为高阻态,DOUTA(B)_OUTPUT呈现SCK上的脉冲自检信号。如果主控芯片能够在BUSY_OUTPUT上成功捕获BUSY_ADC脉冲信号及在DOUTA(B)_OUTPUT上捕获与SCK一致的脉冲自检信号,表明ADC芯片的CONVST、SCK、BUSY、DOUT引脚没有连焊或虚焊的情况发生。

进入B阶段时,CONVST由主控芯片驱动为低电平,多路复用器SEL引脚为低电平,I0被选通,BUSY_OUTPUT呈现CS#信号,此时输出为高电平。三态缓冲器被禁止,输出高阻态。此时CS#仍维持在高电平,DOUTA(B)_ADC输出高阻态,因此DOUTA(B)_OUTPUT呈现高阻态。

进入C阶段时,CONVST保持低电平,CS#由主控芯片驱动为低电平,开始读取ADC采样数据。多路复用器SEL引脚为低电平,I0被选通,BUSY_OUTPUT呈现CS#信号,此时输出低电平。主控芯片输出SCK时钟,ADC依据SCK节拍输出采样数据。三态缓冲器被禁止,输出高阻态。DOUTA(B)_OUTPUT呈现DOUTA(B)_ADC信号,如果主控芯片在B、C段能够在BUSY_OUTPUT上成功捕获CS#高低变化的信号,表明ADC的CS引脚没有连焊或虚焊的情况发生。

3 应用实例

以上ADC采样数据自检回路在公司的PS6000+平台的多个系列装置中得到了很好的验证和应用,包括线路、主变、母差保护装置、测控装置、合并单元等。ADC芯片选用ADI公司的8通道同步采样芯片AD7606,采用2-线串行数据读取方式;三态缓冲器芯片选用TI公司的74LS244,实现由使能端控制的三态输出;多路复用器芯片选用TI公司的74LS157,实现二选一功能。

该自检回路用于生产测试阶段可以快速查找定位ADC采样数据回路的焊接问题,通过返修工序将存在焊接问题的单板重新焊接后可作为成品发货,大大提高了产品的成品率。在装置运行过程中,由于每个采样周期内都进行回路自检,从而保证了每个采样点数据的可信度,一旦自检回路发现异常,立即通知保护装置闭锁相关保护功能并通过事件信息告知ADC采样回路存在异常需要尽快解决,大大降低了保护装置误动作的风险。

结 语

[1] 胡国,唐成虹,徐子安.数字化变电站新型合并单元的研制[J].电力系统自动化,2010(24):51-54.

[2] 梁晓兵,周捷,杨永标.基于IEC61850的新型合并单元的研制[J].电力系统自动化,2007(7):85-89.

[3] 殷志良,刘万顺,杨奇逊.一种遵循IEC 61850标准的合并单元同步的实现新方法[J].电力系统自动化,2004(11):57-61.

[4] 赵应兵,周水斌,马朝阳.基于IEC 61850-9-2的电子式互感器合并单元的研制[J].电力系统保护与控制,2010(6):104-106,110.

[5] 张兆云,刘宏君.数字化变电站光纤差动保护同步新方法[J].电力系统自动化,2010(22):90-92.

[6] 闫志辉,胡彦民,周丽娟. 重采样移相技术在过程层IED中的应用 [J].电力系统保护与控制,2010(6):64-66,71.

[7] 胡永兵,周云飞,杨钦.一种高精度多通道采集系统及其性能分析 [J].微型机与应用,2012(16):28-31.

[8] 徐加彦,张之万,陈兴林.基于FPGA的高速多通道AD采样系统的设计与实现[J].自动化与仪表,2014, 29(9):49-52.

[9] 王伟,杨智涛,吴佳楠.提高DSP的AD转换器精度的研究与实现 [J].现代制造工程,2009(9):47-48.

[10] 于克泳,孙建军.新一代16位8通道同步采样ADC-AD7606在智能电网中的应用[J].电子产品世界,2010(10):71-73.

[11] Analog Device Inc .AD7606 datasheet.8-Channel DAS with 16-Brt,Bipolar input, Simultaneous Sampbng ADC,2010.

[12] Analog Devices Inc .Layout Considerations for an Expandable Muthchannel Simuttaneous Sampling Data Acquisition System(DAS)Based on the AD7606 16-Brt,8-Channel DAS,2010.

[13] 代镭.一种IC芯片引脚焊接缺陷频域检测算法的研究[J].电子技术应用,2008, 34(4):77-80.

[14] 王立伟,孙鹤旭,崔丽娜.激光焊接焊缝质量视觉检测系统[J].自动化仪表,2013,34(2):76-79.

[15] 何志刚,梁堃,周庆波.基于X射线成像的BGA焊接质量检测技术[J].电子工艺技术.2016 (1): 32-34.

叶品勇、陈新之、岳峰(工程师),主要从事电力系统继电保护及自动装置硬件平台开发。

Method of ADC Sampling Data Circuit Self-test

Ye Pinyong,Chen Xinzhi,Yue Feng

(Nanjing Sac Automation Co.,Ltd.,Nanjing 211100,China)

The ADC sampling data is an important source of power system protection,which is an important basis to judge behavior of protection devices.However,the multi-channel simultaneous ADC chips do not have the data check function,so the abnormal sampling data caused by welding problems can not be able to detect,and which can result in the protection device malfunction and serious electrical accidents.Therefore,a method to achieve ADC sampling data circuit self-test is proposed,it uses the ADC sampling timing by an external feedback circuit to check whether the ADC chip welding problem exists,in order to determine the ADC sampling data circuit is connected properly.The method can effectively reduce adverse impacts and economic losses by protection device wrong behavior caused by ADC sampling data abnormal.

ADC chip;data circuit;sampling timing;self-test

TP211

A

�迪娜

2016-10-24)